Professional Documents

Culture Documents

Code: 9A04504 B.Tech III Year I Semester (R09) Supplementary Examinations, May 2013

Code: 9A04504 B.Tech III Year I Semester (R09) Supplementary Examinations, May 2013

Uploaded by

Mahaboob SubahanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Code: 9A04504 B.Tech III Year I Semester (R09) Supplementary Examinations, May 2013

Code: 9A04504 B.Tech III Year I Semester (R09) Supplementary Examinations, May 2013

Uploaded by

Mahaboob SubahanCopyright:

Available Formats

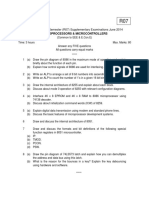

Code: 9A04504 R9

B.Tech III Year I Semester (R09) Supplementary Examinations, May 2013

DIGITAL IC APPLICATIONS

(Electronics and Communication Engineering)

Time: 3 hours Max Marks: 70

Answer any FIVE questions

All questions carry equal marks

*****

1 (a) Explain the effect of floating inputs on CMOS gate.

(b) Explain how a CMOS device is destroyed.

(c) What is the difference between transmission time and propagation delay? Explain these two

parameters with reference to CMOS logic.

2 (a) Compare CMOS, TTL and ECL with reference to logic levels, DC noise margin, propagation

delay and fan-out.

(b) Draw the circuit diagram of basic CMS gate and explain the operation.

3 (a) Explain with an example the syntax and the function of the following VHDL statements:

(i) Process statement. (ii) Case statement.

(b) Explain implicit and explicit visibility of a library in VHDL.

4 (a) Write the data flow style VHDL program for this IC.

(b) Write a process based VHDL program for the prime-number detector of 4-bit input and explain

the flow using logic circuit.

5 Draw the logic diagram of 74X283 and explain its operation and write a VHDL code in data flow

model.

6 Draw the logic diagram of 74X283 and explain its operation and write a VHDL code in data flow

model.

7 (a) Design a conversion circuit to convert a SR flip-flop to JK flip flop.

(b) Write a VHDL code for a SR flip-flop in behavioral model.

8 Determine the ROM size needed to realize the combinational logic function performed by each of

the following MSI parts 74X49, 74X139, 74X153, 74X257, 74X381, 74X682.

*****

You might also like

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandFrom EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandNo ratings yet

- 9A04504 Digital IC Applications6Document4 pages9A04504 Digital IC Applications6subbuNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- Campusexpress - Co.in: Set No. 1Document8 pagesCampusexpress - Co.in: Set No. 1skssushNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- Rr310403-Digital Ic ApplicationsDocument1 pageRr310403-Digital Ic ApplicationssivabharathamurthyNo ratings yet

- Digital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013Document1 pageDigital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013subbuNo ratings yet

- 1 Semester Model Question PapersDocument17 pages1 Semester Model Question PapersBalaji MohantyNo ratings yet

- 9A04504 Digital IC Applications4Document1 page9A04504 Digital IC Applications4subbuNo ratings yet

- R7221004 Digital IC Applications7Document1 pageR7221004 Digital IC Applications7subbuNo ratings yet

- Code: 07A4041 B.Tech III Year I Semester (R07) Supplementary Examinations June 2015Document1 pageCode: 07A4041 B.Tech III Year I Semester (R07) Supplementary Examinations June 2015subbuNo ratings yet

- SS07A4041 Digital IC ApplicationsDocument1 pageSS07A4041 Digital IC ApplicationsMahaboob SubahanNo ratings yet

- Summer 2023Document2 pagesSummer 2023khushalee.chavadaNo ratings yet

- R5310404 Digital IC Applications12Document1 pageR5310404 Digital IC Applications12subbuNo ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- Code No: R05320402Document4 pagesCode No: R05320402chvsrsettiNo ratings yet

- 9A05704 Advanced Computer ArchitectureDocument4 pages9A05704 Advanced Computer ArchitecturesivabharathamurthyNo ratings yet

- Switching Theory and Logic Design - June-2015Document55 pagesSwitching Theory and Logic Design - June-2015Rama HarithaNo ratings yet

- 9A12301 Digital Logic Design and Computer OrganizationDocument4 pages9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNo ratings yet

- NR-320502 Computer NetworksDocument6 pagesNR-320502 Computer NetworksSrinivasa Rao G100% (2)

- 9A12301 Digital Logic Design & Computer OrganizationDocument4 pages9A12301 Digital Logic Design & Computer OrganizationsivabharathamurthyNo ratings yet

- Jntuworld: R07 Set No. 2Document4 pagesJntuworld: R07 Set No. 2Ram KrishnaNo ratings yet

- 9A04602 Microprocessors & Microcontrollers5Document1 page9A04602 Microprocessors & Microcontrollers5subbuNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- R7320202-Microprocessors and MicrocontrollersDocument1 pageR7320202-Microprocessors and MicrocontrollerseltpgroupNo ratings yet

- CS-68 Bachelor in Computer Applications Term-End Examination June, 2012 Cs-68: Computer NetworksDocument2 pagesCS-68 Bachelor in Computer Applications Term-End Examination June, 2012 Cs-68: Computer Networksr_k_sNo ratings yet

- R7310201-Computer System OrganizationDocument4 pagesR7310201-Computer System OrganizationsivabharathamurthyNo ratings yet

- R7320202 Microprocessors & Microcontrollers12Document1 pageR7320202 Microprocessors & Microcontrollers12subbuNo ratings yet

- RT 21053112016Document4 pagesRT 21053112016RaunaqNo ratings yet

- r5410207 Vlsi DesignDocument1 pager5410207 Vlsi DesignsivabharathamurthyNo ratings yet

- 9A04602 - SS9A04602 Microprocessors & MicrocontrollersDocument1 page9A04602 - SS9A04602 Microprocessors & MicrocontrollerssubbuNo ratings yet

- Computer NetworkDocument5 pagesComputer Networkkuvarjigupta2004No ratings yet

- 7th ITDocument6 pages7th ITYashika JindalNo ratings yet

- r05320402 Vlsi DesignDocument4 pagesr05320402 Vlsi DesignSRINIVASA RAO GANTANo ratings yet

- r05321002 Principles of CommunicationDocument8 pagesr05321002 Principles of CommunicationSRINIVASA RAO GANTANo ratings yet

- Advanced Computer ArchitectureDocument4 pagesAdvanced Computer ArchitectureSaikumarVavilaNo ratings yet

- Ect206 Computer Architecture and Microcontrollers, June 2022Document2 pagesEct206 Computer Architecture and Microcontrollers, June 2022instapc0210No ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssivabharathamurthyNo ratings yet

- R7310404 Digital IC Applications2Document1 pageR7310404 Digital IC Applications2subbuNo ratings yet

- 9A04706 Digital Design Through Verilog HDL PDFDocument4 pages9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumNo ratings yet

- 9A15502 Digital System DesignDocument4 pages9A15502 Digital System Designsivabharathamurthy100% (1)

- ETC Raisoni Endsem PaperDocument14 pagesETC Raisoni Endsem PaperYogesh Jounjalkar100% (1)

- 07a80402 EmbeddedandrealtimesystemsDocument6 pages07a80402 EmbeddedandrealtimesystemsSharanya ThirichinapalliNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- QuestionsDocument5 pagesQuestionsgirishdsk2002No ratings yet

- Computer NetworksDocument4 pagesComputer NetworksSavari RajNo ratings yet

- SS 9A04602 Microprocessors & Microcontrollers6Document1 pageSS 9A04602 Microprocessors & Microcontrollers6subbuNo ratings yet

- s4 CAM July 2022Document2 pagess4 CAM July 2022rensiNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssubbuNo ratings yet

- Set No: 1: Code No: V3224/R07Document4 pagesSet No: 1: Code No: V3224/R07jitendra28No ratings yet

- 2022 Dec. ECT203-CDocument2 pages2022 Dec. ECT203-CAthul RamNo ratings yet

- Switching Theory and Logic DesignDocument8 pagesSwitching Theory and Logic DesignVenkat ChadalavadaNo ratings yet

- IUT 9A05503 Computer GraphicsDocument1 pageIUT 9A05503 Computer GraphicssivabharathamurthyNo ratings yet

- Intelligent Manufacturing SystemsDocument5 pagesIntelligent Manufacturing SystemsVenkata RamuduNo ratings yet

- Microcontrollers For Embedded Systems Nec022rDocument1 pageMicrocontrollers For Embedded Systems Nec022rSudhir GoswamiNo ratings yet

- Time: 3 Hours Full Marks: 70Document3 pagesTime: 3 Hours Full Marks: 70pikluNo ratings yet

- r05410207 Vlsi DesignDocument7 pagesr05410207 Vlsi Design9010469071No ratings yet

- Rr320501-Advanced Computer ArchitectureDocument4 pagesRr320501-Advanced Computer ArchitectureSRINIVASA RAO GANTANo ratings yet

- BT BP AcDocument1 pageBT BP AcsubbuNo ratings yet

- 12D86103 Materials For NanotechnologyDocument1 page12D86103 Materials For NanotechnologysubbuNo ratings yet

- 12D86102 Microelectronic Technology & IC FabricationDocument1 page12D86102 Microelectronic Technology & IC FabricationsubbuNo ratings yet

- 12D86101 Advanced Computing MethodsDocument1 page12D86101 Advanced Computing MethodssubbuNo ratings yet

- 12D75104b Advanced Instrumentation SystemsDocument1 page12D75104b Advanced Instrumentation SystemssubbuNo ratings yet

- 12D20102 Advanced Structural AnalysisDocument2 pages12D20102 Advanced Structural AnalysissubbuNo ratings yet

- 12d20105a Experimental Stress AnalysisDocument1 page12d20105a Experimental Stress AnalysissubbuNo ratings yet

- Jntuworld: (Common To Vlsies, Esvlsi & Vlsiesd)Document1 pageJntuworld: (Common To Vlsies, Esvlsi & Vlsiesd)subbuNo ratings yet

- 12D20105c Low Cost Housing TechniquesDocument1 page12D20105c Low Cost Housing TechniquessubbuNo ratings yet

- 12d20106a Prestressed ConcreteDocument1 page12d20106a Prestressed ConcretesubbuNo ratings yet

- 9d58106a Advances in DatabasesDocument1 page9d58106a Advances in DatabasessubbuNo ratings yet

- 9D61103 Computer Communication NetworksDocument1 page9D61103 Computer Communication NetworkssubbuNo ratings yet

- 9D58203 Advanced Computer NetworksDocument1 page9D58203 Advanced Computer NetworkssubbuNo ratings yet

- 9D57106c ASIC DesignDocument1 page9D57106c ASIC DesignsubbuNo ratings yet

- 9D57102 Analog IC DesignDocument1 page9D57102 Analog IC DesignsubbuNo ratings yet

- 9D57105 Hardware Software Co-DesignDocument1 page9D57105 Hardware Software Co-DesignsubbuNo ratings yet