Professional Documents

Culture Documents

LIC Lab Manual

Uploaded by

oniza shaikhOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LIC Lab Manual

Uploaded by

oniza shaikhCopyright:

Available Formats

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Pin Details of IC 741:

Logic Symbol of IC 741:

Specifications for IC 741

Supply Voltage ±22 V

Input Voltage ±15 V

Power Dissipation = 500 mW

Operating Temperature Range -55˚C to 25˚C

Electrical Characteristics

S. No Characteristics Minimum Maximum

1 Input bias current 50nA 80 nA

2 Input Voltage range ±12 V ±15 V

3 Supply Current 1.7mA 2.8A

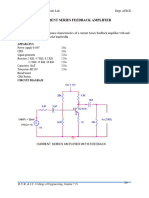

Circuit Diagram of Inverting Amplifier:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

1

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design Procedure:

ACL = 1; R1 = 1KΩ

ACL = Vo / Vi = - Rf / R1

Rf = ACL × R1 = 1KΩ

Tabulation:

Input Voltage (Vin) Output Voltage VO in Volts

S. No

in Volts Theoretical Value Practical Value

EXP. NO :1

DATE : LINEAR OPERATIONAL AMPLIFIER CIRCUITS

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

2

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

----------------------------------------------------------------------------------------------

Aim:

To design, construct and test the following linear operational amplifier circuits

(1) Inverting amplifier (2) Non-inverting amplifier

(3) Voltage follower (4) Summing Amplifier

(5) Integrator (6) Differentiator

(7) Subtractor

Components Required:

S. No Component Name Range Type Quantity

1 Op-amp

2 Power Supply

3 Resistor

4 Capacitor

5 Voltmeter

6 Breadboard

7 Signal generator

Theory:

Inverting Amplifier:

The inverting amplifier is the most widely used in all the op-amp

circuits. The output voltage VO is fed back to inverting input terminal through the R f - R1

network where Rf is the feedback resistor. The input signal Vi is applied to the inverting

input terminal through R1 and non-inverting input terminal of op-amp is grounded.

VO = (Rf / R1) Vi

ACL = Vo / Vi = - Rf / R1

The Negative sign indicates a phase shift of 180˚ between input (Vi) and Output (Vo).

Non-Inverting Amplifier:

The non inverting amplifier circuit amplifies without inverting the

input signal. In this circuit, the input is applied to the non inverting input terminal and

inverting input terminal is grounded such a circuit is called non inverting amplifier. It is

also having a negative feedback system as output is fed back to the inverting input

terminal.

VO = (1+ (Rf / R1) Vi

ACL = Vo / Vi = 1+ (Rf / R1)

Circuit Diagram of Inverting Amplifier:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

3

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design Procedure:

ACL = 2; R1 = 1KΩ

ACL = Vo / Vi = 1+ (Rf / R1) = 2

Rf = (ACL-1) × R1 = 1KΩ

Tabulation:

Input Voltage (Vin) Output Voltage VO in Volts

S. No

in Volts Theoretical Value Practical Value

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

4

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Voltage Follower:

In this circuit, the output voltage is equal to the input voltage both

in magnitude and phase i.e. output follows the input. So, the circuit is called voltage

follower. Input is applied to non inverting input and the output is directly connected to

inverting input.

VO = Vi

Procedure:

1. Make the connections as per the circuit diagram.

2. Vary the input voltage using regulated DC power supply then measure and

tabulate the corresponding output voltage.

3. Compare theoretical Output with the actual output obtained from the circuit.

Circuit Diagram for Voltage Follower:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

5

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design Procedure:

VO = Vi

Tabulation:

Input Voltage (Vin) Output Voltage VO in Volts

S. No

in Volts Theoretical Value Practical Value

Summing Amplifier (summer):

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

6

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

The operational amplifier is used to design a circuit whose output is

equal to sum of the several input signals. Such a circuit is known as summer. It has two

configurations as (1) Inverting Summer amplifier (2) Non – inverting summing amplifier.

(1) Inverting summing amplifier, the input is given to the inverting input terminal of op-

amp. The circuit output is the inverted sum.

VO = [(Rf / R1) V1 + (Rf / R2) V2

(2) Non inverting summing amplifier, the input is given to the non inverting input

terminal of operational amplifier. The output of the circuit is non inverted sum.

Circuit Diagram for Summing Amplifier:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

7

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design Procedure:

VO = [-(Rf / R1) V1 + (Rf / R2) V2]

R1= R2 = Rf

R1= R2 = Rf = 1KΩ

VO = - [V1 + V2]

Tabulation:

Input Voltage (Vin)

Output Voltage VO in Volts

S. No in Volts

V1 V2 Theoretical Value Practical Value

6

Difference Amplifier (Subtractor):

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

8

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

A circuit that amplifies the difference between the two signals is

called difference amplifier. This type of amplifiers is mostly used in instrumentation

circuit.

VO = (Rf / R1) (V1-V2)

The main purpose of the difference amplifier stage is to provide high gain to the

difference mode signal and cancel the common mode signal i.e., it should have high

CMRR.

Differentiator:

One of the simplest of the op-amp circuits that contain capacitor is the

differentiating amplifier or differentiator. As the name Differentiator suggests, the circuit

performs the mathematical operation of differentiation. That is, the output waveform is

the derivative of input waveform. But by using the differentiator at high frequencies, it

may becomes unstable and break into oscillation. The impedance at input also decreases

with increase in frequency; thereby making the circuit sensitive to high frequency noise.

Analysis of Practical Differentiator:

As the input current of op-amp is zero, there is no current input at

node B. Hence it is at the ground potential. From the concept of virtual ground, node A is

also at the ground potential and hence VB = VA = 0V.

Circuit Diagram for Difference Amplifier:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

9

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design Procedure:

R1= R2 = 1KΩ

R3 = Rf = 4.7 KΩ

VO = (Rf / R1) [V1 - V2]

Tabulation:

Input Voltage (Vin)

Output Voltage VO in Volts

S. No in Volts

V1 V2 Theoretical Value Practical Value

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

10

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

For the current I, we can write,

V -V

I = in A ----------------- V = 0

Z A

1

V

I = in Where Z = R in series with C

Z 1 1 1

1

So in Laplace domain we can write,

1 1+ sR C

Z =R + = 1 1

1 1 sC sC

1 1

sC Vin (s)

I = 1

1+ sR C

1 1

Now the current I is,

1

V -V V

I = A O =- O

1 R R

f f

V (s)

In Laplace, I =- O

1 R

f

d (V - V ) dV

and I =C A O =-C O

2 f dt f dt

Taling Laplace Transform we get,

I = - sC Vo (s)

2 f

Applying KCL at node A,

I = I +I

1 2

sC Vin (s) V (s)

1 =- O - sC Vo (s)

1+ sR C R f

1 1 f

-sR C V (s)

f 1 in

V (s) =

O

[1+ s Cf R f ] [1+ s C1 R1 ]

If C R = C R then

f f 1 1

-sR f C1Vin(s)

V (s) =

O 2

1+ s C1 R1

The time constant R C is much greater than R C or R C and hence

f 1 1 1 f f

the equation becomes

V (s) = - sR C V (s)

O f 1 in

dVin (t) d

VO (t) = - R f C1 ------------ as s=

dt dt

The output voltage is the R C times the differentiation of the input.

f 1

Circuit Diagram for Differentiator:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

11

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design:

dVi 1

V =-R C R = 1.6KΩ R = 1KΩ f =1KHz =

O f 1 dt f 1 2πR C

f 1

1 R ×R

C =

1 2πf R

= 0.16μf ; R eq = 1 f = 615Ω

f R +R

1 f

Model Graph:

Integrator:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

12

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

One of the simple op-amp circuits that also contain the capacitor is known as

integrator. As the name integrator suggests, the circuit performs the mathematical

operation of integration. That is, the output waveform is the integration of input

waveform.

Analysis of Practical Integrator:

As the input of op-amp is zero, the node B still at ground potential. Hence the

node A is also at the ground potential from the concept of virtual ground. So, VA = 0.

(V -V )

I = in A ----------------- V = 0

R A

1

V

I = in

R

1

d (V - V )

Similarly I =-C A O

1 f dt

dV

=- C A

f dt

V -V

And I = A O

2 R

f

V

=- O

R

f

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

13

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Tabular Column: Differentiator

Input Voltage (Vi) in Output Voltage (Vo)

S.NO Time period in ms

volts in volts

Tabular Column: Integrator

Input Voltage (Vi) in Output Voltage (Vo)

S.NO Time period in ms

volts in volts

Procedure for Differentiator and Integrator:

1. Make the Connections as per the circuit diagram.

2. Set the 1 KHz square wave input using function generator and obtain the output

waveform on the CRO.

3. Determine and tabulate the amplitude, time period of the output waveform.

4. Draw the graph for output.

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

14

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

At node A, applying KCL

I =I +I

1 2

V dV V

in = - C O - O

R f dt R

1 f .

Taking Laplace transform of above Equation,

V (s)

V (s) / R = - s C V (s) - O

in 1 f O R

f

1

= - V (s) [s C + ]

O f R

f

[1+ s C R ]

= - V (s) f f

O R

f

R

V (s) = - f V (s)

O R [1+ s R C ] in

1 f f

1

V (s) = - V (s)

O R in

sR C + 1

1 f R

f

When R is very large than R / R can be neglected and hence circuit behaves like

f 1 f

an ideal integrator as

1

V (s) = - V (s)

O sR C in

1 f

1

VO (t) = - ∫ Vin (t) dt --------- as 1/s = ∫ dt

sR1 Cf

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

15

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Circuit Diagram for Integrator:

Design: R1 = 1K, C=1µF and f = 1KHZ

T = 1/f

f=1/2∏ R1Cf

VO = Vin ×T / (R1×C1) = 1.6K

R eq = R1*Rf / (R1 +Rf) = 1.6×10 6/2.6×103 = 615Ω

Model Graph:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

16

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the linear operational amplifier circuits were designed, constructed and its

performance was tested using op-amp IC 741.

Circuit Diagram for Astable Multivibrator Using Op-amp:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

17

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design:

R2

R = R = R = 6.8KΩ C = 0.01μf β = = 0.5

1 2 R1 + R2

1+β 1

T = 2RC ln = 0.15ms Frequency(f) = = 6.7KHz

1-β T

Model Graph:

EXP. NO :2

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

18

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

DATE : MULTIVIBRATOR CIRCUITS USING OPERATIONAL AMPLIFIER

---------------------------------------------------------------------------------------------------

Aim:

To design, construct and test the performance of astable and monostable

multivibrators using operational amplifier.

Components Required:

S. No Component Name Range Type Quantity

1 Op-amp

2 Power Supply

3 Resistor

4 Capacitor

5 Voltmeter

6 Breadboard

7 Signal generator

Theory:

Astable Multivibrator:

Astable Multivibrator is a square wave generator. A simple op-amp

square wave generator is also called a free running generator. The principle of

generation of square wave output is to force an op-amp to operate in saturation region.

β = R2 / (R1+R2) of output is feedback to the positive input terminal. Thus the reference

voltage VR is β VO and may takes value as +β Vsat or -β Vsat. The output is also feedback

to the negative input terminal. After interchanging by means of the low pass RC

combination whenever input at negative input terminal slightly exceeds reference

voltage then switching takes place resulting in square wave output in astable

multivibrator both states are quasi states.

Procedure:

1. Make the connections as per the circuit diagram.

2. Switch on the regulated power supply and observe the output in CRO.

3. Calculate the output frequency and verify it with the theoretical frequency

obtained from the design steps.

4. Draw the graph for output.

Circuit Diagram for Monostable Multivibrator Using Op-amp:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

19

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Model Graph:

Monostable Multivibrator:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

20

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

In monostable multivibrator the diode D 1 is connected across

the capacitor(C). The diode clamps the capacitor voltage to 0.7V. When the output is at

+Vsat, narrow negative triggering pulse Vt is applied to non inverting terminal through

diode D2. Let us assume the output voltage VO is at +Vsat in its stable state. The diode D1

conducts and the voltage across the capacitor(C) is VC gets clamped to 0.7V. The voltage

at non inverting input terminal is controlled by potentiometer divides of R1R2 to β VO. i.e.

+ β Vsat in stable state. If Vt is a negative trigger of amplitude so that effective voltage at

this terminal is less than 0.7V (+ β Vsat + (-Vt) then the output of the op-amp changes its

state from +Vsat to -Vsat. The diode is now reverse biased and the capacitor starts

charging exponentially to -Vsat through resistance R. The time constant of charging is

zero.

Procedure:

1. Make the connections as per the circuit diagram.

2. Using the function generator Apply the trigger input to the non inverting

input terminal of op-amp.

3. Measure the output from CRO.

4. Characteristics of Input, output versus time are drawn from the readings

observed in CRO.

Tabular Column: Astable Multivibrator

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

21

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Capacitor

Output Voltage

S.NO Voltage (VC) in Time in ms Time in ms

(VO) in volts

volts

Tabular Column: Monostable Multivibrator

Time in ms

Input Voltage Output Voltage

S.NO

(Vi) in volts (VO) in volts

TON TOFF

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

22

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the astable and monostable multivibrator circuits were designed and tested

the performance using operational amplifier.

Circuit Diagram for Zero Crossing Detector:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

23

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Model Graph:

EXP. NO :3

DATE : APPLICATIONS OF COMPARATOR CIRCUITS

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

24

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

---------------------------------------------------------------------------------------------------

Aim:

To design, construct and test the performance of following applications of

comparator circuits using operational amplifier.

(1) Zero crossing detector (2) Window detectors (3) Schmitt Trigger

Components Required:

S. No Component Name Range Type Quantity

1 Op-amp

2 Power Supply

3 Resistor

4 Voltmeter

5 Breadboard

6 Connecting Wires

Theory:

Zero Crossing Detector:

The basic comparator can be used as a zero crossing detector. It answers the

questions: Is the input signal greater than or less than zero? A typical circuit for

inverting zero crossing detector is shown in figure with Vref = 0V. During the +ve half

cycle, the input voltage is positive i.e., above the reference voltage. Hence the output

voltage is - Vsat. During the –ve half cycle, the input voltage Vin is negative, i.e., below

the reference voltage. The output voltage is the +Vsat. Thus the output voltage switches

between -Vsat to +Vsat whenever the input signal crosses the zero level.

Window detector:

Window detector is a circuit which is used to mark the instant at which an

unknown input is between two threshold levels. The window detector circuit is shown in

the figure to display three level detections with indicator. Three indicators available in

the circuit are LED 3 for high input (Vi >10V), LED 2 for safe input (5V < Vi < 10V) and

LED 1 for low input (Vi <5V).

Procedure:

1. Make the connections as per the circuit diagram.

2. Set the input signal (Say 1V, 1 KHz) using signal generator.

3. Observe the input and output waveforms on the CRO.

4. Plot the graph for Vi versus time and VO versus time.

Circuit Diagram for Window Detector:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

25

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Tabular Column:

Input Voltage OUTPUT DETECTIONS

S.No

(Vi) LED 1 LED 2 LED 3

1 Vi <5V ON OFF OFF

2 5V < Vi < 10V OFF ON OFF

3 Vi >10V OFF OFF ON

Schmitt Trigger:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

26

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

In Schmitt trigger circuit, the input voltage is applied to the negative

terminal of op-amp and resistor R is chosen equal to R 1||R2 to compensate the input bias

current. The input Vin trigger the output VO, every time it exceeds a certain voltage level

and these voltage levels are called upper threshold voltage and lower threshold voltage.

The hysteresis width is the difference between these two voltage levels.

Design:

R R

= V + 2 (Vsat - V ) - 2 (Vsat + V )

V

UT ref ref

V =V

LT ref ref

R1 +R2 R1 +R2

V =0 V R =100KΩ R = 10KΩ Vsat = 1V

ref 2 1

R

= V + 2 (Vsat - V ) = +0.9

V

UT ref ref

R1 +R2

R

- 2 (Vsat + V ) = -0.9

V =V

LT ref ref

R1 +R2

V = - V = 0.9 = -0.9

UT LT

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

27

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Circuit Diagram for Schmitt Trigger:

Tabular Column:

Input Voltage Output Voltage Threshold Voltage in Volts

S.No

(Vi) in volts (VO) in volts VUT VLT

Model Graph:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

28

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Threshold Voltage:

The threshold voltages are calculated as follows for the output VO = +Vsat, the

input voltage at the positive terminal is called as upper threshold voltage and given by

VUT = Vref + [{R2 / (R1+R2)} {+Vsat - Vref}].

As long as Vi is less than VUT, the output remains at +V sat and when Vi is slightly

greater than VUT, the output switches to -Vsat and remains at same level till Vi>VUT.

For the output VO = -Vsat, the input voltage at the +ve terminal is called lower

threshold voltage is given by,

VLT = Vref – [{R2 / (R1+R2)} {+Vsat - Vref}]

As long as Vi is less than VLT, the output remains at -Vsat and when Vi is slightly

greater than VLT, the output switches to +Vsat and remains at that level till Vi>VLT.

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the applications of comparator circuits were designed, constructed and

tested the performance using operational amplifier.

Circuit Diagram for 2nd order Butterworth Active Low Pass Filter:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

29

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design of Low Pass Filter:

1. Select fH = 3 KHz

2. Set R2 = R3 = R and C2 = C3 = C =0.01μf (C is always ≤ 1μf).

3. Calculate R from f H = 1 / 2∏RC

R = 1 / 2∏ f H C = 5.3KΩ = R2 = R3

R

4. For Butterworth response AF = 1+ f = 1.586 ; R = (1.586 -1) R1

f

R1

5. Choose R1=10 KΩ then Rf = 5.86 KΩ

Model Graph:

EXP. NO :4

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

30

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

DATE : ACTIVE FILTERS USING OP-AMP

---------------------------------------------------------------------------------------------------

Aim:

To design, construct and obtain the frequency response of following active filters

using operational amplifiers

(1) Low pass filter (2) High pass filter (3) Band pass filter (4) Band Stop filter

Components Required:

S. No Component Name Range Type Quantity

1 Op-amp

2 Power Supply

3 Resistor

4 Capacitor

5 Voltmeter

6 Breadboard

7 Signal Generator

Theory:

Low Pass Filter:

The practical response of the filter must be very close to an ideal one. In

case of low pass filter, it is always desirable that the gain rolls off very fast after the cut

off frequency, in the stop band. In case of first order filter, it rolls off at a rate of 20 dB/

decade. In case of second order filter the gain rolls of at a rate of 40dB / decade. Thus

the slope of the frequency response after f=fH is -40dB / decade, for a second order low

pass filter. The first order filter can be converted to second order type by using an

additional RC network. The gain of the second order filter is determined by R 1 and Rf.

The fH is designed by R2, C2, R3, and C3 as follows.

1

f = . For a second order low pass Butterworth filter,

H 2π R R C C

2 3 2 3

the voltage gain magnitude equation is

Vo AF Rf

=

Vin 4 Where AF = 1+ Pass band gain of the filter

f

1+

f H R1

1

f = --High Cutoff frequency in Hz and F=Input Frequency (Hz)

H 2π R R C C

2 3 2 3

Circuit Diagram for 2nd order Butterworth Active High Pass Filter:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

31

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design of High Pass Filter:

1. Select fL = 3 KHz

2. Set R2 = R3 = R and C2 = C3 = C =0.01μf (C is always ≤ 1μf).

3. Calculate R from f L = 1 / 2∏RC

R = 1 / 2∏ f L C = 5.3KΩ = R2 = R3

R

4. For Butterworth response AF = 1+ f = 1.586 ; R = (1.586 -1) R1

f

R1

5. Choose R1=10 KΩ then Rf = 5.86 KΩ

Model Graph:

Procedure:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

32

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

1. Make the connections as per the circuit diagram.

2. Vary the frequency of input signal and note the corresponding output

voltage.

3. Calculate the gain and draw the graph.

4. Find the cut off frequency.

Tabular Column: Low Pass Filter

Vin =

Output Voltage (VO) Gain = 20 log

S.No Frequency in Hz

in Volts (VO/Vin) dB.

Circuit Diagram for 2nd order Butterworth Wide Band Pass Filter:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

33

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design of Wide Band Pass Filter:

1. Select f L = 3 KHz and f H = 10 KHz.

2. Choose C1 = C2 = 0.01μf.

3. f L = 1 / 2∏ R2 C2 then R2 =1 / 2∏ f L C2 = 5.3KΩ

4. f H = 1 / 2∏ R1 C1 then R1 =1 / 2∏ f H C1 = 1.6KΩ

5. Band Width= f H - f L

MODEL GRAPH:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

34

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

High Pass Filter:

A second order high pass filter can be obtained from a second order low

pass filter simply by interchanging the frequency determining resistors and capacitors.

The Voltage gain magnitude of the second order high pass filter is given by

Vo AF

=

Vin 4

f

1+ L

f

Where AF = 1.586 – Pass band gain; fL = Low cutoff frequency and f= frequency of the

input signal

1

f =

L 2π R R C C

2 3 2 3

Since second order low pass and high pass filters are alike except that the positions of

resistors and capacitors are being interchanged, the design and frequency scaling

procedures are same for high pass filter as those for the low pass filter.

Tabular Column: High Pass Filter

Vin =

Output Voltage (VO) Gain = 20 log

S.No Frequency in Hz

in Volts (VO/Vin) dB.

Circuit Diagram for 2nd order Butterworth Wide Band Stop Filter:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

35

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design of Wide Band Stop Filter:

1. Select f L = 10 KHz and f H = 3 KHz.

2. Choose C1 = C2 = 0.01μf.

3. f L = 1 / 2∏ R2 C2 then R2 =1 / 2∏ f L C2 = 1.6KΩ

4. f H = 1 / 2∏ R1 C1 then R1 =1 / 2∏ f H C1 = 5.3KΩ

Model Graph:

Band Pass Filter:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

36

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Band Pass Filter is a frequency selective circuit that passes signal of

specified band of frequency and alternates the frequencies outside the band. There are

two types of band pass filter namely wide band pass and narrow band pass. A wide band

pass filter can be formed by cascading a high pass and low pass filter sections with f H>fL

where function is the corner frequency of low pass and f L is high pass filter. A band pass

filter has the pass band between two cut off frequencies fH – fL.

Procedure:

1. Make the connections as per the circuit diagram.

2. The input voltage is set to the constant value say 2V.

3. Vary the frequency of input signal and note the corresponding output

voltage.

4. Calculate the gain and draw the graph.

5. Find the cut off frequencies.

Tabular Column: Band Pass Filter

Vin =

Output Voltage (VO) Gain = 20 log

S.No Frequency in Hz

in Volts (VO/Vin) dB.

Band Stop Filter:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

37

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Band stop filter attenuates frequencies in the stop band and passes them outside

the band. The other names given for Band stop filter are Band – reject filter and Band –

elimination filter. The band stop filter can be classified as wide band stop and narrow

band stop filters. In lab class, we are going to design a Wide Band Stop filter.

Wide Band Stop filter:

A wide band stop filter consists of a low pass filter, a high pass filter and a

summing amplifier. The lower cut off frequency f L of the high pass filter must be greater

than the higher cutoff frequency f H of the low pass filter. It is to be noted that the pass

band gain of both the high pass and low pass filters must be equal.

Tabular Column: Band Stop Filter

Vin =

Output Voltage (VO) Gain = 20 log

S.No Frequency in Hz

in Volts (VO/Vin) dB.

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

38

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the active filter circuits were designed constructed and tested the

performance using operational amplifier and cut off frequencies were found.

Circuit Diagram for Astable Multivibrator Using IC 555:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

39

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design:

RA = 1K, RB = 2.2 K and C = 0.01μf

1 1.45

f = =

O T (R A + 2 RB )C = 26.85 KHz

R A + RB

% Duty Cycle = ×100 = 59.25%

R A + 2 RB

Model Graph:

EXP. NO :5

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

40

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

DATE : MULTIVIBRATOR CIRCUITS USING IC 555 TIMER

----------------------------------------------------------------------------------------------

Aim:

To design, construct and obtain the frequency response and test performance of

astable and monostable multivibrator using IC 555 timer.

Components Required:

S. No Component Name Range Type Quantity

1 Timer IC

2 Power Supply

3 Resistor

4 Capacitor

5 Voltmeter

6 Breadboard

7 Signal Generator

Theory:

Astable Multivibrator:

Comparing with monostable operation timing resistor is split into

two sections RA and RB. Pin 7, discharging transistor Q1 is connected to the junction of RA

and RB. When the power supply VCC is connected, the external timing capacitor C charges

towards VCC with the time constant (RA+RB) C. During this time output (pin 3) is high as

Reset R=0, S=1 and this combination makes Q’ = 0 which has unclamped timing

capacitor C.

When the capacitor voltage equals 2/3 VCC, upper comparator triggers the control

flip-flop so that Q’ = 1. This turns make transistor Q1 ON and capacitor C starts

discharging towards ground through RB and a transistor Q1 with a time constant RBC and

current also flowing through RA. Resistor RA and RB must be large enough to limit this

current and prevent damage to discharge transistor Q1. From the figure, we can observe

that the capacitor is periodically charged and discharged between 2/3 VCC and 1/3 VCC

respectively. The required between the capacitor charges from 1/3 VCC to 2/3 VCC is given

by (Output High)

t C = 0.69 (R A+R B) C = TON

The time during which the capacitor discharges from 2/3 VCC to 1/3 VCC is equal to

(Output Low)

t d =0.69 (R B) C = TOFF

Circuit Diagram for Monostable Multivibrator Using IC 555:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

41

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design:

Pulse Width (TP) = 1.1 R C = 1.1×100×10 3×100×10 -6 = 11 Seconds

Model Graph:

The total period of the waveform is,

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

42

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

T=t + t = 0.69(R + 2 R )C ---------- T = TON + TOFF

C d A B

The frequency of Oscillation is,

1 1.45

f = =

O T (R A + 2 RB )C

The duty cycle is the ratio of the time t C during which the output is high to the total

period T. It is given by

t

% Duty Cycle = C ×100

T

R A + RB

= ×100

R A + 2 RB

Monostable Multivibrator:

A 555 timer is connected for monostable operation and its

functional diagram. In the stand by state, FF holds transistor Q1 ON, thus clamping the

external trigger timing capacitor C to ground. The output remains at the ground potential

i.e low. As the trigger passes through VCC/3, FF is set Q’=0. This makes the transistor Q1

OFF and the short circuit across the timing capacitor C is relaxed. As Q’ is low, output

goes high i.e equal to VCC. The timing cycle now begins. Since C is unclamped, Voltage

across it exponentially through R towards VCC with a time constant RC. After a time

period T, the capacitor voltage is slightly greater than (2/3) VCC and the upper

comparator resets the FF that is R1=0, S=0. This makes Q’=1 transistor Q1 goes on there

by discharging the capacitor C rapidly to ground potential. The output returns to the

stand by state on ground potential. It is evident from that the timing interval is

independent of supply voltage. It may also be noted that once triggered, the output

remain in HIGH state until time T.

TP = 1.1 R C Seconds

Procedure:

1. Make the connections as per the circuit diagram.

2. Switch ON the Dual power supply observe the output on CRO.

3. Calculate the output frequency from CRO and verify it with frequency

calculated theoretically.

4. Follow the above steps for both Astable and Monostable Multivibrator.

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

43

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Tabular Column: Astable Multivibrator:

Capacitor Time in ms

Output Voltage Frequency in

S.No Voltage (VC) in Time in ms

(VO) in volts TON TOFF Hz

volts

Tabular Column: Monostable Multivibrator

Capacitor

Output Voltage Frequency in

S.No Voltage (VC) in Time in sec Time in sec

(VO) in volts Hz

volts

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

44

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the multivibrator circuits using 555 timer were designed constructed and

tested the performance using 555 timer.

Circuit Diagram for RC Phase Shift Oscillator:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

45

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design:

f = 1 KHz, C = 0.01μf (Std. Value), R1 = 2.2K and Rf = 29 R1 = 29×2.2K = 63.8K

1 1

f= R = 2π f C 6 = 6.5KΩ

2π R C 6

Rf 63.8K Rf

A ≥ 29 = ≥ 29 = = 29 (Condition ≥ 29 was satisfied)

R1 2.2K R1

Tabular Column:

Output Voltage Designed Observed

S.No Time in ms

(VO) in Volts Frequency Frequency

Model Graph:

EXP. NO :6

DATE : OSCILLATORS USING OPERATIONAL AMPLIFIER

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

46

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

----------------------------------------------------------------------------------------------

Aim:

To design, construct and test the performance of RC phase shift oscillator and

Wien bridge oscillator using operational amplifiers.

Components Required:

S. No Component Name Range Type Quantity

1 Op-amp

2 Power Supply

3 Resistor

4 Capacitor

5 Voltmeter

6 Breadboard

7 Signal Generator

Theory:

RC Phase Shift Oscillator:

1 1

β= ; Condition for Oscillation = A β ≥ 1 A β ≥1 A ≥ β A ≥ 29

29

RC phase shift oscillator which uses a common emitter single stage amplifier and

phase shifting network consists of the identical RC sections. The output of the feedback

network gets loaded to the low output impedance of transistor. Hence an emitter follows

input stage before the common emitter amplifier stage can be used to avoid the problem

of the low input impedance. A phase shifting network is feedback network, so output of

the amplifier is given as an input to the feedback is given as an input to the amplifier.

Practically the resistance Rf of the inverting amplifier is designed by, by making current

through it, much larger than input bias current of the op-amp. Let the current through Rf

is I1 then,

I1 = 100 Ib (max)

Without amplitude stabilization, the output of the oscillator oscillates between the levels

±Vsat. VO = +VO (sat); Rf = - VO (sat) / I1 -- [+VO (sat) can be assumed 1Volt < VCC]

1 R

Now, ACL ≥

29

R f ≥ 29 .Design the value of R1 from gain requirement. To

1

prevent loading of the amplifier because RC networks, it is necessary that R1 ≥ 10 R.

1

R = R1 / 10; Now C= gives required value of capacitor.

2π f R 6

Circuit Diagram for Wien Bridge Oscillator:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

47

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Design:

f = 5 KHz, Rf = 10K, R1=3.3K and C = 0.01μf (Std. Value)

1 1

f= R = 2π f C = 3.2K (Use Std. Value 3.3K)

2π R C

Rf 10K

A ≥ 3 = 1+ R ≥ 3 = 1+ ≥ 3 A=4(Barkhausen criterion was satisfied (A≥3))

1 3.3K

Tabular Column:

Output Voltage Designed Observed

S.No Time in ms

(VO) in Volts Frequency Frequency

Model Graph:

Wien Bridge Oscillator:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

48

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

A basic Wien bridge is used in this stage as amplifier. The output of amplifier is

applied between terminal 1 and 3, which is input of feedback network. While amplifier

input is applied from diagonal terminals 2 and 4, which is the output from the feedback

network. Thus two arms of the bridge namely R 1C1 in series and R2C2 in parallel are

called frequency sensitive arms. Because of components of these two arms decides the

frequency of oscillation. Let us find out the gain of the feedback network. As seen earlier

input Vin to the feedback network is between 1 and 3 while output V f of the feedback

network is between 2 and 4. Such a feedback network called lead-lag network. This is

because at very low frequency it acts like a lead while at very high frequency it acts like

a lag. Another important advantage of Wien bridge oscillator on varying the two

capacitors simultaneously by mounting them on the common shaft, different frequency

range can be provided. To satisfy Barkhausen criterion that A β ≥ 1. It is necessary that

the gain of the non inverting op-amp amplifier must be minimum 3.

R Rf

ACL ≥ 3 1+ f ≥ 3 ≥2

R1 R1

1

The frequency of Oscillation is given by f =

2π R C

Procedure:

1. Make the connections as per the circuit diagram.

2. Supply Voltage is set as 12V using Dual power supply.

3. Calculate output voltage and time (ms) for both RC phase shift oscillator

and Wien bridge oscillator.

4. Draw the graph between output voltage and time.

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the RC phase shift oscillator and Wien bridge oscillator using operational

were designed, constructed and performance was verified.

Circuit Diagram for Weighted Resistor DAC:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

49

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Circuit Diagram for R-2R Ladder DAC:

Model Graph:

EXP. NO :7

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

50

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

DATE : DIGITAL TO ANALOG CONVERTERS USING OP-AMP

----------------------------------------------------------------------------------------------

Aim:

To design and construct a digital input into analog output converters using

operational amplifier.

Components Required:

S. No Component Name Range Type Quantity

1 Op-amp

2 Power Supply

3 Resistor

4 Voltmeter

5 Breadboard

6 Connecting Wires

Theory:

Weighted Resistor DAC:

The weighted resistor DAC consists of a summing amplifier with binary weighted

resistor network as shown in the circuit diagram. When the binary input is ‘1’ then it

connects the resistance to the reference voltage (-VR). If the input is ‘0’ resistor

connected to the ground. The output of the op-amp is given as

I = I + I +.......+ In

0 1 2

V V V

I = R d + R d +...........+ nR dn

0 2R 1 2 2 2 R

2 R

V -1 -2 -n

I = R (d 2 + d 2 +........+ dn 2 )

0 R 1 2

The output voltage,

R

V =I R =V f (d 2-1 + d 2-2 +........+ d 2-n )

0 0 f R R 1 2 n

The circuit uses a negative reference voltage. We observe positive staircase for

analog output voltage. It can be observed that,

1. The op-amp functions as a current to voltage converter.

2. Although the op-amp is connected in inverting mode, it can also be

possible to connect in non-inverting mode.

3. The polarity of the reference voltage is selected in accordance with the

position of the switch. (Resistor Value)

R – 2R Ladder Network:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

51

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

The binary weighted resistor type DAC needs wide range of resistors. It can be

avoided by using R – 2R ladder type DAC. It uses only two values of resistors. It is

highly suited for IC technology. The circuit diagram of R – 2R ladder DAC is shown in

figure.

If the binary input data is 0001, then the output VO is equal to VR/16.

Tabular Column:

Binary Data Analog Output in Volts

S.No

D3 D2 D1 D0 R – 2R Ladder DAC Weighted DAC

1 0 0 0 0

2 0 0 0 1

3 0 0 1 0

4 0 0 1 1

5 0 1 0 0

6 0 1 0 1

7 0 1 1 0

8 0 1 1 1

9 1 0 0 0

10 1 0 0 1

11 1 0 1 0

12 1 0 1 1

13 1 1 0 0

14 1 1 0 1

15 1 1 1 0

16 1 1 1

Procedure:

1. Make the connections as per the circuit diagram.

2. Apply the four bit binary data to the resistive network and obtain the equivalent

analog output.

3. Draw the graph between digital input versus analog output

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

52

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the Digital to Analog Converter circuits were designed, constructed and

verified its performance using operational amplifier.

Circuit Diagram for Low Voltage Regulation Using IC 723:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

53

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Tabular Column:

Load Regulation (Vin = 10V) Line Regulation (RL = 5KΩ)

S.No Output Voltage (VO) in Input Voltage Output Voltage

RL in KΩ

Volts (Vin) in Volts (VO) in Volts

Model graph:

EXP. NO :8

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

54

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

DATE : STUDY OF VOLTAGE REGULATOR USING IC LM 723

----------------------------------------------------------------------------------------------

Aim:

To design, construct and test the performance of low voltage and high voltage

regulation using IC LM 723.

Components Required:

S. No Component Name Range Type Quantity

1 Regulator IC

2 Power Supply

3 Resistor

4 Capacitor

5 Voltmeter

6 Breadboard

Theory:

Initially the output voltage is high capacitor starts charging towards V C through RA

and RB. As soon as capacitor higher than flip-flop and output switches low. Now capacitor

starts discharging through RB and transistor Q1. When the voltage across C equal to

VEVCC, lower than comparator output triggers the flip-flop and discharged between

(2/3)*VCC and VEVCC. The time duration which the capacitor charges VEVCC to (2/3)*VCC is

equal to the time output. With the advent of micro electronics, it is to incorporate the

complete circuit. This gives low cost high reliability, reduction in size and excellent

performance. Examples of monolithic regulators are 78XX / 79XX and 723 general

purpose regulators.

Line Regulation is defined as the % change in output voltage for a change in input

voltage. It is usually expressed in milli-volts or as a % of the output voltage.

Load Regulation is defined as the % change in output voltage for a change in load

current and is also expressed in milli-volts or as a % of the output voltage.

Procedure:

1. Make the connections as per the circuit diagram.

2. Set the input voltage Vin and calculate the output voltage by varying load

resistance for load regulation.

3. Set the load resistance RL=5K and calculate the output voltage by varying

input voltage for line regulation.

4. Plot the graph between Vout versus load resistance for load regulation and

Vout versus Vin for line regulation.

Circuit Diagram for High Voltage Regulation using IC 723:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

55

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Tabular Column:

Load Regulation (Vin = 10V) Line Regulation (RL = 5KΩ)

S.No Output Voltage (VO) in Input Voltage Output Voltage

RL in KΩ

Volts (Vin) in Volts (VO) in Volts

Model graph:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

56

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the Low voltage and High voltage regulation using LM 723 was performed

and its line and load regulation characteristics were drawn.

Circuit Diagram of Sample and Hold:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

57

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Logic Diagram of Sample and Hold IC:

Pin Details of Sample and Hold IC:

EXP. NO :9

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

58

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

DATE : SAMPLE AND HOLD CIRCUITS

----------------------------------------------------------------------------------------------

Aim:

To design, construct a Sample and Hold circuit and verify its performance with LF

398 IC.

Components required:

S. No Component Name Range Type Quantity

1 Sample and Hold IC

2 Power Supply

3 Resistor

4 Capacitor

5 Voltmeter

6 Breadboard

Theory:

In sample and The LF398 is a monolithic sample-and-hold circuit which utilizes

high-voltage on-implant JFET technology to obtain ultra-high DC accuracy with fast

acquisition of signal and low droop rate. Operating as a unity gain follower, DC gain

accuracy is 0.002% typical and acquisition time is as low as 6 ms to 0.01%.

Model Graph:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

59

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

A bipolar input stage is used to achieve low offset voltage and wide bandwidth.

Input offset adjust is accomplished with a single pin and does not degrade input offset

drift. The wide bandwidth allows the LF398 to be included inside the feedback loop of 1

MHz op amps without having stability problems. Input impedance of 1010W allows high

source impedances to be used without degrading accuracy. P-channel junction FET’s are

combined with bipolar devices in the output amplifier to give droop rates as low as 5 mV

per minute with a 1 mF hold capacitor. The JFET’s have much lower noise than MOS

devices used in previous designs and do not exhibit high temperature instabilities.

The overall design guarantees no feed through from input to output in the hold

mode even for input signals equal to the supply voltages. Logic inputs are fully

differential with low input current, allowing direct connection to TTL, PMOS, and CMOS;

differential threshold is 1.4 V. The LF398 will operate from ±5 V to ±18 V supplies. It is

available in 8-pin plastic DIP and 14-pin plastic SO packages.

FEATURES

Operates from ±5 V to ±18 V supplies

Less than 10 μs acquisition time

TTL, PMOS, CMOS compatible logic input

0.5 mV typical hold step at CH = 0.01 μF

Low input offset

0.002% gain accuracy

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

60

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Low output noise in hold mode

Input characteristics do not change during hold mode

High supply rejection ratio in sample or hold

Wide bandwidth

Procedure:

1. Make the connection as per the circuit diagram.

2. Apply the analog input to the sample and Hold Circuit and determine the

parameters of sample and Hold operation.

3. Draw the graph by using parameters obtained.

Performance Parameters of S/H Circuits:

Acquisition Time (t ):

ac

It is the time required for the holding capacitor CH to charge up to a level

close to the input voltage during sampling. It depends on three factors:

• RC time constant

• Maximum output current of op-amp

• Slew rate of op-amp

Aperture Time (t ap)

Because of propagation delays through the driver and switch, VO will keep

tracking Vi some time after the inception of the hold command. This is the aperture time.

To get the precise timing, it is necessary to advance hold command by this amount.

Aperture Uncertainty (Δ t ap):

It is the variation in aperture time from sample to sample. Due to aperture

uncertainty it is difficult to compensate aperture time by advancing hold Command.

Hold Mode settling time (t S):

After the application of hold command, it takes a certain amount of time

for VO to settle within a specified error band, such as 1%, 0.1% or 0.01%.

Hold Step:

The change in output voltage is referred as Hold step = ΔVO= ΔQ / CH

Voltage Droop:

The leakage current causes voltage of the capacitor to drop down is known as droop.

Feedthrough:

In the Hold mode, because of stray capacitance across the switch, there is

a small amount of ac coupling between VO and Vi. This ac coupling causes output voltage

to vary with variation in the input voltage. This is referred as Feedthrough.

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

61

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the Low voltage and High voltage regulation using LM 723 was performed

and its line and load regulation characteristics were drawn.

Circuit Diagram for Analog Divider:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

62

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

10(Z2 - Z1 )

Divider Output = V = + Y1

O

X1 - X2

Circuit Diagram for Analog Square Rooter:

Square Rooter Output = V = 10(Z - Z ) + X

O 2 1 2

EXP. NO : 10

DATE :

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

63

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

ANALOG MULTIPLIER AS DIVIDER, SQUARER AND SQUARE ROOTER

---------------------------------------------------------------------------------------------

Aim:

To design, construct and test a analog Multiplier as divider, squarer and square

rooter.

Components required:

S. No Component Name Range Type Quantity

1 Multiplier IC

2 Power Supply

3 Resistor

4 Voltmeter

5 Breadboard

6 Connecting Wires

Theory:

The AD534 is a monolithic laser trimmed four-quadrant multiplier divider having

accuracy specifications previously found only in expensive hybrid or modular products. A

maximum multiplication error of ±0.25% is guaranteed for the AD534L without any

external trimming. Excellent supply rejection, low temperature coefficients and long term

stability of the on-chip thin film resistors and buried Zener reference preserve accuracy

even under adverse conditions of use. It is the first multiplier to offer fully differential,

high impedance operation on all inputs, including the Z-input, a feature which greatly

increases its flexibility and ease of use. The scale factor is pre-trimmed to the standard

value of 10.00 V; by means of an external resistor, this can be reduced to values as low

as 3 V. The wide spectrum of applications and the availability of several grades

commend this multiplier as the first choice for all new designs. The AD534 is the first

general purpose multiplier capable of providing gains up to X100, frequently eliminating

the need for separate instrumentation amplifiers to precondition the inputs. The AD534

can be very effectively employed as a variable gain differential input amplifier with high

common-mode rejection. The gain option is available in all modes, and will be found to

simplify the implementation of many function-fitting algorithms such as those used to

generate sine and tangent. The utility of this feature is enhanced by the inherent low

noise of the AD534: 90 mV, RMS (depending on the gain), a factor of 10 lower than

previous monolithic multipliers. Drift and feed through are also substantially reduced

over earlier designs.

Circuit Diagram for Analog Squarer:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

64

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

SF = Noise Spectral Density = 10V

A = open loop gain of output amplifier, typically 70 dB at DC

(X1 - X2 ) (Y1 - Y2 )

Vout = A - (Z - Z )

1 2

SF

sub (X1 = Y1 ) and (X2 = Y2 ), then

(X - X )2

Vout = A 1 2 - (Z - Z )

1 2

SF

FUNCTIONAL DESCRIPTION

BLOCK DIAGRAM OF AD 534

The functional block diagram of the AD534 is shown in figure. Inputs are

converted to differential currents by three identical voltages to current converters, each

trimmed for zero offset. The product of the X and Y currents is generated by a multiplier

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

65

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

cell using Gilbert’s trans-linear technique. An on-chip “Buried Zener” provides a highly

stable reference, which is laser trimmed to provide an overall scale factor of 10 V. The

difference between XY/SF and Z is then applied to the high gain output amplifier. This

permits various closed loop configurations and dramatically reduces nonlinearities due to

the input amplifiers, a dominant source of distortion in earlier designs. The effectiveness

of the new scheme can be judged from the fact that under typical conditions as a

multiplier the nonlinearity on the Y input, with X at full scale (±10 V), is ±0.005% of FS;

even at its worst point, which occurs when X = ±6.4 V, it is typically only ±0.05% of FS

Nonlinearity for signals applied to the X input, on the other hand, is determined almost

entirely by the multiplier element and is parabolic in form. This error is a major factor in

determining the overall accuracy of the unit and hence is closely related to the device

grade. The generalized transfer function for the AD534 is given by:

(X1 - X2 ) (Y1 - Y2 )

Vout = A - (Z - Z )

1 2

SF

Where A = open loop gain of output amplifier, typically 70 dB at DC

X, Y, Z = input voltages (full scale = ±SF, peak =±1.25 SF)

SF = scale factor, pre-trimmed to 10.00 V but adjustable by the user down to 3 V.

In most cases the open loop gain can be regarded as infinite, and SF will be 10 V. The

operation performed by the AD534, can then be described in terms of equation:

(X1 - X2)(Y1 -Y2) = 10V (Z1 - Z2)

The user may adjust SF for values between 10.00 V and 3 V by connecting an

external resistor in series with a potentiometer between SF and –VS. The approximate

value of the total resistance for a given value of SF is given by the relationship:

SF

R SF = 5.4K

10 - SF

Tabular Column:

DIVIDER

APPLICATIONS INPUTS Output

USING AD 534

MULTIPLIER X1 X2 Y1 Y2 Z1 Z2 VO

DIVIDER

SQUARER

APPLICATIONS INPUTS Output

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

66

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

USING AD 534

X1 X2 Y1 Y2 Z1 Z2 VO

MULTIPLIER

SQUARER

SQUARE ROOTER

APPLICATIONS INPUTS Output

USING AD 534

MULTIPLIER X1 X2 Y1 Y2 Z1 Z2 VO

SQUARE ROOTER

Due to device tolerances, allowance should be made to vary RSF; by ±25% using

the potentiometer. Considerable reduction in bias currents, noise and drift can be

achieved by decreasing SF. This has the overall effect of increasing signal gain without

the customary increase in noise. Note that the peak input signal is always limited to 1.25

SF (i.e., ±5 V for SF = 4 V) so the overall transfer function will show a maximum gain of

1.25. The performance with small input signals, however, is improved by using a lower

SF since the dynamic range of the inputs is now fully utilized. Bandwidth is unaffected by

the use of this option. Supply voltages of ±15 V are generally assumed. However,

satisfactory operation is possible down to ±8 V. Since all inputs maintain a constant

peak input capability of ±1.25 SF some feedback attenuation will be necessary to

achieve output voltage swings in excess of ±12 V when using higher supply voltages.

OPERATION AS A MULTIPLIER

Diagram shows the basic connection for multiplication. Note that the circuit will

meet all specifications without trimming. In some cases the user may wish to reduce ac

feed through to a minimum by applying an external trim voltage (±30 mV range

required) to the X or Y input. Figure 19 shows the typical ac feed through with this

adjustment mode. Note that the Y input is a factor of 10 lower than the X input and

should be used in applications where null suppression is critical. The high impedance Z 2

terminal of the AD534 may be used to sum an additional signal into the output. In this

mode the output amplifier behaves as a voltage follower with a 1 MHz small signal

bandwidth and a 20 V/ms slew rate. This terminal should always be referenced to the

ground point of the driven system, particularly if this is remote. Likewise, the differential

inputs should be referenced to their respective ground potentials to realize the full

accuracy of the AD534.

OPERATION AS A DIVIDER

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

67

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

The Figure shows the connection required for division. Unlike earlier products, the

AD534 provides differential operation on both numerator and denominator, allowing the

ratio of two floating variables to be generated. Further flexibility results from access to a

high impedance summing input to Y1. As with all dividers based on the use of a multiplier

in a feedback loop, the bandwidth is proportional to the denominator magnitude. Without

additional trimming, the accuracy of the AD534K and L is sufficient to maintain a 1%

error over a 10 V to 1 V denominator range. This range may be extended to 100:1 by

simply reducing the X offset with an externally generated trim voltage (range required is

±3.5 mV max) applied to the unused X input (see Figure 1). To trim, apply a ramp of

+100 mV to +V at 100 Hz to both X1 and Z1 (if X2 is used for offset adjustment,

otherwise reverse the signal polarity) and adjust the trim voltage to minimize the

variation in the output. Since the output will be near +10 V, it should be ac-coupled for

this adjustment.

The increase in noise level and reduction in bandwidth preclude operation much

beyond a ratio of 100 to 1. As with the multiplier connection, overall gain can be

introduced by inserting a simple attenuator between the output and Y2 terminal. This

option and the differential-ratio capability of the AD534 are utilized in the percentage-

computer applications. This configuration generates an output proportional to the

percentage deviation of one variable (A) with respect to a reference variable (B), with a

scale of one volt per percent.

OPERATION AS A SQUARE ROOTER

The operation of the AD534 in the square root mode is shown in Figure. The

diode prevents a latching condition which could occur if the input momentarily changes

polarity. As shown, the output is always positive; it may be changed to a negative output

by reversing the diode direction and interchanging the X inputs. Since the signal input is

differential, all combinations of input and output polarities can be realized, but operation

is restricted to the one quadrant associated with each combination of inputs. In contrast

to earlier devices, which were intolerant of capacitive loads in the square root modes,

the AD534 is stable with all loads up to at least 1000 pF. For critical applications, a small

adjustment to the Z input offset will improve accuracy for inputs below 1 V.

OPERATION AS A SQUARER

Operation as a squarer is achieved in the same fashion as the multiplier except

that the X and Y inputs are used in parallel. The differential inputs can be used to

determine the output polarity (positive for X1 = Y1 and X2 = Y2, negative if either one of

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

68

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

the inputs is reversed). Accuracy in the squaring mode is typically a factor of 2 better

than in the multiplying mode, the largest errors occurring with small values of output for

input below 1 V. If the application depends on accurate operation for inputs that are

always less than ±3 V, the use of a reduced value of SF is recommended as described in

the Functional Description section. Alternatively, a feedback attenuator may be used to

raise the output level. This is put to use in the difference-of-squares application to

compensate for the factor of 2, loss involved in generating the sum term. The difference-

of-squares function is also used as the basis for a novel RMS-to-dc converter. The

averaging filter is a true integrator, and the loop seeks to zero its input. For this to

occur, (VIN)2 – (VOUT)2 = 0 (for signals whose period is well below the averaging time-

constant). Hence VOUT is forced to equal the RMS value of V IN. The absolute accuracy of

this technique is very high; at medium frequencies, and for signals near full scale, it is

determined almost entirely by the ratio of the resistors in the inverting amplifier. The

multiplier scaling voltage affects only open loop gain. The data shown is typical of

performance that can be achieved with an AD534K, but even using an AD534J, this

technique can readily provide better than 1% accuracy over a wide frequency range,

even for crest-factors in excess of 10.

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

69

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Max. Marks

Description

Marks Secured

Preparation 30

Performance 40

Viva Voce 10

Record 20

Total 100

Staff Signature

Result:

Thus the Analog multiplier as divider, squarer and square rooter circuits were

designed, constructed and tested using analog multiplier IC - AD 534.

Pin Diagram of AD 573 IC:

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

70

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Tabular Column:

MSB Equivalent Digital Output LSB

Analog Input

in Volts DB DB DB DB DB DB DB DB DB DB

9 8 7 6 5 4 3 2 1 0

EXP. NO : 11

DATE : SUCCESSIVE APPROXIMATION ANALOG TO DIGITAL CONVERTER

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

71

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

----------------------------------------------------------------------------------------------

Aim:

To design, construct and test the performance of successive approximation

analog to digital converter – AD 573 IC.

Components Required:

S. No Component Name Range Type Quantity

Analog to Digital

1

Converter IC

2 Power Supply

3 Resistor

4 Breadboard

5 Connecting Wires

Theory:

FUNCTIONAL DESCRIPTION

A block diagram of the AD573 is shown in Figure 1. The positive CONVERT pulse

must be at least 500 ns wide. DR goes high within 1.5 ms after the leading edge of the

convert pulse indicating that the internal logic has been reset. The negative edge of the

CONVERT pulse initiates the conversion. The internal 10-bit current output DAC is

sequenced by the integrated injection logic (I2L) successive approximation register (SAR)

from its most significant bit to least significant bit to provide an output current which

accurately balances the input signal current through the 5 kW resistor. The comparator

determines whether the addition of each successively weighted bit current causes the

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

72

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

DAC current sum to be greater or less than the input current; if the sum is more, the bit

is turned off. After testing all bits, the SAR contains a 10-bit binary code which

accurately represents the input signal to within 1/2 LSB (0.05% of full scale).

The SAR drives DR Low to indicate that the conversion is complete and that the

data is available to the output buffers. HBE and LBE can then be activated to enable the

upper 8-bit and lower 2-bit buffers as desired. HBE and LBE should be brought high prior

to the next conversion to place the output buffers in the high impedance state. The

temperature compensated buried Zener reference provides the primary voltage

reference to the DAC and ensures excellent stability with both time and temperature.

The bipolar offset input controls a switch which allows the positive bipolar offset current

(exactly equal to the value of the MSB less 1/2 LSB) to be injected into the summing (+)

node of the comparator to offset the DAC output. Thus the nominal 0 V to +10 V

Unipolar input range becomes a –5 V to +5 V range. The 5 kW thin-film input resistor is

trimmed so that with a full-scale input signal, an input current will be generated which

exactly matches the DAC output with all bits on.

UNIPOLAR CONNECTION

The AD573 contains all the active components required to perform a complete

A/D conversion. Thus, for many applications, all that is necessary is connection of the

power supplies (+5 V and –12 V to –15 V), the analog input and the convert pulse.

However, there are some features and special connections which should be considered

for achieving optimum performance. The functional pin out is shown in Figure 2. The

standard Unipolar 0 V to +10 V range is obtained by shorting the bipolar offset control

pin (Pin 16) to digital common (Pin 17).

Full-Scale Calibration

The 5 kW thin-film input resistors is laser trimmed to produce a current which

matches the full-scale current of the internal DAC—plus about 0.3%—when an analog

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

73

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

input voltage of 9.990 volts (10 volts – 1 LSB) is applied at the input. The input resistor

is trimmed in this way so that if a fine trimming potentiometer is inserted in series with

the input signal, the input current at the full-scale input voltage can be trimmed down to

match the DAC full-scale current as precisely as desired. However, for many applications

the nominal 9.99 volt full scale can be achieved to sufficient accuracy by simply inserting

a 15 W resistor in series with the analog input to Pin 14. Typical full-scale calibration

error will then be within ±2 LSB or ±0.2%. If more precise calibration is desired, a 50 W

trimmer should be used instead. Set the analog input at 9.990 volts, and set the trimmer

so that the output code is just at the transition between 11111111 10 and 11111111 11.

Each LSB will then have a weight of 9.766 mV. If a nominal full scale of 10.24 volts is

desired (which makes the LSB have a weight of exactly 10.00 mV), a 100 W resistor and

a 100 W trimmer (or a 200 W trimmer with good resolution) should be used. Of course,

larger full-scale ranges can be arranged by using a larger input resistor, but linearity and

full-scale temperature coefficient may be compromised if the external resistor becomes a

sizeable percentage of 5 kW. Figure 3 illustrates the connections required for full-scale

calibration.

Unipolar Offset Calibration

Since the Unipolar Offset is less than ±1 LSB for all versions of the AD573, most

applications will not require trimming. Figure 4 illustrates two trimming methods which

can be used if greater accuracy is necessary. Figure 4a shows how the converter zero

may be offset by up to ±3 bits to correct the device initial offset and/or input signal

offsets. As shown, the circuit gives approximately symmetrical adjustment in unipolar

mode.

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

74

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

Figure 5 shows the nominal transfer curve near zero for an AD573 in Unipolar

mode. The code transitions are at the edges of the nominal bit weights. In some

applications it will be preferable to offset the code transitions so that they fall between

the nominal bit weights, as shown in the offset characteristics. This offset can easily be

accomplished as shown in Figure 4b. At balance (after a conversion) approximately 2 mA

flows into the Analog Common terminal.

A 2.7 W resistor in series with this terminal will result in approximately the

desired 1/2 bit offset of the transfer characteristics. The nominal 2 mA Analog Common

current is not closely controlled in manufacture. If high accuracy is required, a 5 W

potentiometer (connected as a rheostat) can be used as R1. Additional negative offset

range may be obtained by using larger values of R1. Of course, if the zero transition

point is changed, the full-scale transition point will also move. Thus, if an offset of 1/2

LSB is introduced; full-scale trimming as described on the previous page should be done

with an analog input of 9.985 volts.

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

75

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

BIPOLAR CONNECTION

To obtain the bipolar –5 V to +5 V range with an offset binary output code, the

bipolar offset control pin is left open. A –5.000 volt signal will give a 10-bit code of

00000000 00; an input of 0.000 volts results in an output code of 10000000 00 and

+4.99 volts at the input yields the 11111111 11 code. The nominal transfer curve is

shown in Figure 6.

Note that, in the bipolar mode, the code transitions are offset 1/2 LSB such that

an input voltage of 0 volts ±5 mV yields the code representing zero (10000000 00).

Each output code is then centered on its nominal input voltage.

Full-Scale Calibration

Full-Scale Calibration is accomplished in the same manner as in unipolar

operation except the full scale input voltage is +4.985 volts.

Negative Full-Scale Calibration

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

76

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

The circuit in Figure 4a can also be used in bipolar operation to offset the input

voltage (nominally –5 V) which results in the 00000000 00 code. R2 should be omitted

to obtain a symmetrical range. The bipolar offset control input is not directly TTL

compatible but a TTL interface for logic control can be constructed as shown in Figure 7.

SAMPLE-HOLD AMPLIFIER CONNECTION TO THE AD573

Many situations in high speed acquisition systems or digitizing rapidly changing

signals require a sample-hold amplifier (SHA) in front of the A/D converter. The SHA can

acquire and hold a signal faster than the converter can perform a conversion. A SHA can

also be used to accurately define the exact point in time at which the signal is sampled.

For the AD573, a SHA can also serve as a high input impedance buffer. Figure 8 shows

the AD573 connected to the AD582 monolithic SHA for high speed signal acquisition. In

this configuration, the AD582 will acquire a 10 volt signal in less than 10 ms with a

droop rate less than 100 mV/ms.

DR goes high after the conversion is initiated to indicate that reset of the SAR is

complete. In Figure 8 it is also used to put the AD582 into the hold mode while the

AD573 begins its conversion cycle. (The AD582 settles to final value well in advance of

the first comparator decision inside the AD573). DR goes low when the conversion is

complete placing the AD582 back in the sample mode. Configured as shown in Figure 8,

the next conversion can be initiated after a 10 ms delay to allow for signal acquisition by

the AD582. Observe carefully the ground, supply, and bypass capacitor connections

between the two devices. This will minimize ground noise and interference during the

conversion cycle.

LIC LAB MANUAL P.SUNDARAVADIVEL & B.SAKTHIKUMAR - AP/ECE

77

VIDYAA VIKAS COLLEGE OF ENGINEERING AND TECHNOLOGU, TIRUCHENGODE

GROUNDING CONSIDERATIONS