Professional Documents

Culture Documents

LCD v2017 2 DAC R2R PDF

Uploaded by

Cesar CabreraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LCD v2017 2 DAC R2R PDF

Uploaded by

Cesar CabreraCopyright:

Available Formats

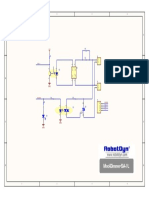

A B C D E F G H J K

0 VDD 0

VPP_MCLR

U1

VPP_MCLR 1 MCLR AVDD 40

RB0 2 AN0/VREF+/CN2/RB0 AVSS 39

VDD 3 38

RB1 AN1/VREF-/CN3/RB1 AN9/RB9 LCD_RS

J1 RB2 4 AN2/SS1/LVDIN/CN4/RB2 AN10/RB10 37 LCD_RW

5 36 VDD

1 RB3

6

AN3/CN5/RB3 AN11/RB11

35

LCD_E J2

1 2 RB4 AN4/CN6/RB4 AN121/RB12 LCD16x2 1

VDD 7 34

3 RB5 AN5/CN7/RB5 EMUC2/OC1/RDO LCD_D4

RB6_PGC 8 PGC/EMUC/AN6/OCFA/RB6 EMUD2/OC2/RD1 33 LCD_D5

4 RB7_PGD

RB7_PGD 9 PGD/EMUD/AN7/RB7 VDD 32

5 RB6_PGC VDD

10 AN8/RB8 VSS 31

6

11 VDD RF0 30 RF0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

12 VSS RF1 29 RF1

SIL6

OSC1 13 OSC1/CLKIN U2RX/CN17/RF4 28 RF4

OSC2 14 OSC2/CLKO/RC15 U2TX/CN18/RF5 27 RF5

15 EMUD1/SOSC1/T2CK/U1ATX/CN1/RC13 U1RX/SDI1/SDA/RF2 26 RF2 R11

16 25 47

2 17

EMUC1/SOSCO/T1CK/U1ARX/CN0/RC14 EMUD3/U1TX/SDO/SCL/RF3

24

RF3 2

INT0/RA11 EMUC3/SCK1/RF6 RF6

18 IC2/INT2/RD9 IC1/INT1/RD8 23

LCD_D7 19 RD3 RD2 22 LCD_D6

VDD

20 VSS VDD 21

Vpot

LCD_D4

LCD_D5

LCD_D6

LCD_D7

LCD_RS

LCD_E

LCD_RW

VDD DSPIC30F4013

3 3

Vpot

VDD

R1

OSC1

OSC2

10k VDD

3

R2 2 45% 1

VPP_MCLR X1

1k

1

4 10k 4

B1 C1 RV1

12MHz

100nF

C2 C3

3

15pF 15pF

5 5

RB6_PGC

RB7_PGD

RF0

RF1

RF2

RF3

RF4

RF5

RF6

RB0

RB1

RB2

RB3

RB4

RB5

6 6

R3 R4 R5 R6 R7 R8 R9 R10 R19

330 330 330 330 330 330 330

330

20k

R20 R21 R22 R23 R24 R25

20k 20k 20k 20k 20k 20k

D0 D1 D2 D3 D4 D5 D6 D7

1

LED LED LED LED LED LED LED LED

R12 R13 R14 R15 R16 R17 R18

Señal de salida

7 20k 10k 10k 10k 10k 10k 10k 7

2

8 8

FILE NAME: DSPIC30F4013 DATE:

DESIGN TITLE: ESQUEMATICO 23/05/2017

9 9

PAGE:

PATH: ESQUEMATICO.pdrj 1 of 1

BY: Juan Vega M. REV: 0.2 TIME: 11:31:28 a. m.

A B C D E F G H J K

You might also like

- Esquematico Dspic30f4013 2017 2Document1 pageEsquematico Dspic30f4013 2017 2Cesar CabreraNo ratings yet

- WO 5800 - 1N 1.0 User Guide PDFDocument164 pagesWO 5800 - 1N 1.0 User Guide PDFMauricio Pelé50% (2)

- MD2278 Microstepping Driver SpecsDocument3 pagesMD2278 Microstepping Driver Specshoangmanh1989No ratings yet

- DsPIC Elmer 166 en USDocument78 pagesDsPIC Elmer 166 en USnawzat100% (2)

- Conexion Motor Pap PDFDocument70 pagesConexion Motor Pap PDFKaterine FreireNo ratings yet

- Mod Dimmer 5A 2LDocument1 pageMod Dimmer 5A 2LRazwan ali saeedNo ratings yet

- Features Description: Single Phase, Multifunction Energy Meter ICDocument30 pagesFeatures Description: Single Phase, Multifunction Energy Meter ICRohit SivakumarNo ratings yet

- Schematic 0G 00005677 Mod Dimmer 5A 1L PDFDocument1 pageSchematic 0G 00005677 Mod Dimmer 5A 1L PDFvictor maurizioNo ratings yet

- TimersDocument22 pagesTimersghulam mustafaNo ratings yet

- Fmdd50d40nom (2D45M)Document2 pagesFmdd50d40nom (2D45M)AnkuNo ratings yet

- Nrf24l01 Tutorial 1 Pic18Document9 pagesNrf24l01 Tutorial 1 Pic18Silvanei Fonseca LeandroNo ratings yet

- PDFDocument202 pagesPDFAnand KalNo ratings yet

- Programming DsPIC in CDocument86 pagesProgramming DsPIC in CHassaan Shah100% (1)

- Fuentes Conmutadas LNKDocument19 pagesFuentes Conmutadas LNKSergio EstradaNo ratings yet

- DISEÑO DE UN PROTOTIPO DE UN ROBOT ASPIRADORA CON COMPONENTES OPEN SOURCEDocument102 pagesDISEÑO DE UN PROTOTIPO DE UN ROBOT ASPIRADORA CON COMPONENTES OPEN SOURCEMckenna Group100% (1)

- Arduino and 7 Segment LEDDocument5 pagesArduino and 7 Segment LEDAnonymous h2VaB0No ratings yet

- Catalogo Transformadores de IgnicionDocument20 pagesCatalogo Transformadores de Ignicionfrank torresNo ratings yet

- MCT-222 Embedded Systems: Finite State MachinesDocument39 pagesMCT-222 Embedded Systems: Finite State MachinesUsman TariqNo ratings yet

- Develop and Operate Your LoRaWAN IoT NodesDocument224 pagesDevelop and Operate Your LoRaWAN IoT NodesEsmo ImmoNo ratings yet

- Build an ICSP programmer for small PIC microcontrollersDocument14 pagesBuild an ICSP programmer for small PIC microcontrollersJOYCE100% (1)

- Tv3207-Zc02-01a Ob2263 Ice3b0565 SCH PDFDocument1 pageTv3207-Zc02-01a Ob2263 Ice3b0565 SCH PDFshafiuddin7326No ratings yet

- RoboKids 2 PDFDocument83 pagesRoboKids 2 PDFEmi NurkholifNo ratings yet

- BP080WX7-100 20130805 201702209800Document22 pagesBP080WX7-100 20130805 201702209800godzalli44No ratings yet

- Makeblock Walle: Food Living Outside Play Technology WorkshopDocument28 pagesMakeblock Walle: Food Living Outside Play Technology Workshopmichipce4291No ratings yet

- 24W04Document2 pages24W04maldomattNo ratings yet

- iF111S iF121S iF211S iF221S: Instruction ManualDocument20 pagesiF111S iF121S iF211S iF221S: Instruction ManualMiguel PerezNo ratings yet

- AVR DAC 328 TutorialDocument5 pagesAVR DAC 328 Tutorialsutekidane7435No ratings yet

- F405-WTE Manual PDFDocument5 pagesF405-WTE Manual PDFBlockFace08No ratings yet

- Proces rm010 - en PDocument148 pagesProces rm010 - en PmarklmendozaNo ratings yet

- dsPIC Language Tools Libraries PDFDocument404 pagesdsPIC Language Tools Libraries PDFpeter26194100% (3)

- Modification of The Lexmark E260 For Direct Laser Printing of Printed Circuit Boards - MCU Version - 13 Steps (With Pictures)Document29 pagesModification of The Lexmark E260 For Direct Laser Printing of Printed Circuit Boards - MCU Version - 13 Steps (With Pictures)Joel Antonio Lopez LopezNo ratings yet

- Ethernet Module ENC28J60 Arduino PDFDocument5 pagesEthernet Module ENC28J60 Arduino PDFArdian Ramadita SugaraNo ratings yet

- Unity and MySQLDocument30 pagesUnity and MySQLRobertoBrNo ratings yet

- MCT-222 Embedded Systems Lecture 5: AAPCS Parameter PassingDocument22 pagesMCT-222 Embedded Systems Lecture 5: AAPCS Parameter PassingUsman TariqNo ratings yet

- Fall in Love With I2C LCD Displays PDFDocument7 pagesFall in Love With I2C LCD Displays PDFbluesky_1976No ratings yet

- Mikrobasic ProDocument29 pagesMikrobasic ProZul JoeyNo ratings yet

- PSW1500W/PSW2000W Instruction ManualDocument20 pagesPSW1500W/PSW2000W Instruction ManualIng Kevin DÍazNo ratings yet

- CodeVisionAVR User Manual PDFDocument836 pagesCodeVisionAVR User Manual PDFSugeng HariadiNo ratings yet

- C Programming in Atmel Studio 7Document12 pagesC Programming in Atmel Studio 7M. A. BoroumandNo ratings yet

- AN4 EPM240 Board PDFDocument7 pagesAN4 EPM240 Board PDFbenoit lemayNo ratings yet

- ATmega16 ADC Conversion to Digital ValuesDocument7 pagesATmega16 ADC Conversion to Digital ValuesGaurav Shinde100% (1)

- Eralytics RCS 2.0 200Document104 pagesEralytics RCS 2.0 200samNo ratings yet

- ModBusVIEWoTCP User ManualDocument29 pagesModBusVIEWoTCP User ManualvthassoNo ratings yet

- SparkFun ESP8266 Thing Development WorkshopDocument75 pagesSparkFun ESP8266 Thing Development WorkshopalanNo ratings yet

- VL53L0X Distance Sensor User Manual enDocument12 pagesVL53L0X Distance Sensor User Manual enMarcelo D.No ratings yet

- ADAS (Roadscope 7 and Optian 7) 2017Document4 pagesADAS (Roadscope 7 and Optian 7) 2017Patricio Fernando Muñoz MorenoNo ratings yet

- HBS86 HDDocument7 pagesHBS86 HDLuis Flores0% (1)

- ATTINY13 Servo CTRLDocument1 pageATTINY13 Servo CTRLPusaka WigiNo ratings yet

- Roborobo Usb To Serial Gender Usb Driver Install Manual: Created by Jy, Translated by Eun Woo Kim Roborobo 2009-11-11Document4 pagesRoborobo Usb To Serial Gender Usb Driver Install Manual: Created by Jy, Translated by Eun Woo Kim Roborobo 2009-11-11Richard Alberth Poma GomezNo ratings yet

- Embedded C and Atmel AvrDocument427 pagesEmbedded C and Atmel AvrtronguyenNo ratings yet

- LCD v2017 2 DAC R2R PDFDocument1 pageLCD v2017 2 DAC R2R PDFjorge ernesto100% (1)

- PiclesKit SCHDocument2 pagesPiclesKit SCHUlisses RodriguesNo ratings yet

- Oprog PDFDocument8 pagesOprog PDFdario100% (3)

- REPEATER IDER ISD25xx - Repeater Ider Isd2590 16f877aDocument1 pageREPEATER IDER ISD25xx - Repeater Ider Isd2590 16f877amanuel contrerasNo ratings yet

- J10 To J14 2-Pin Male Headers - J10, J11 Shorted by Jumper When Programming - J12, J13, J14 Shorted During Board TestingDocument1 pageJ10 To J14 2-Pin Male Headers - J10, J11 Shorted by Jumper When Programming - J12, J13, J14 Shorted During Board TestingRenzoNo ratings yet

- Schematic Capture - D - Recent Project in Desktop - Embedded Project - Coin Box - Coinbox - PDSPRJ PDFDocument1 pageSchematic Capture - D - Recent Project in Desktop - Embedded Project - Coin Box - Coinbox - PDSPRJ PDFsathish100% (2)

- Acepic Pro Schematic V5.1Document7 pagesAcepic Pro Schematic V5.1Cristian KrutzerNo ratings yet

- An optimized title for a PIC18F4431 microcontroller schematicDocument1 pageAn optimized title for a PIC18F4431 microcontroller schematicnguyendtk5No ratings yet

- Pic16f628a BordDocument1 pagePic16f628a BordcabrestoNo ratings yet

- Ti-Spc-Psi-Protct-6070 (9 08) PDFDocument49 pagesTi-Spc-Psi-Protct-6070 (9 08) PDFsrdeetrdsbc100% (2)

- PSU CalculatorDocument10 pagesPSU CalculatorVíctor RojasNo ratings yet

- Solar Operated Railway Crack Detector (Report)Document96 pagesSolar Operated Railway Crack Detector (Report)Shibi Siddharth0% (1)

- Western Maryland RailwayDocument36 pagesWestern Maryland RailwaywmfanNo ratings yet

- SM Sakai Sv505-1Document410 pagesSM Sakai Sv505-1LU YO88% (8)

- Report For Action: Date: April 16, 2019 To: City Council From: City Manager Wards: AllDocument20 pagesReport For Action: Date: April 16, 2019 To: City Council From: City Manager Wards: AllToronto StarNo ratings yet

- Archives: Skeleton in Rafters of Kleinfeltersville Hotel, 1902Document1 pageArchives: Skeleton in Rafters of Kleinfeltersville Hotel, 1902Andrea GillhoolleyNo ratings yet

- Training Facilities On Pakistan RailwaysDocument7 pagesTraining Facilities On Pakistan RailwaysMaqsood A. KhanNo ratings yet

- 2024 - Current Affairs Saltamami 2023 (Boimate - Com)Document56 pages2024 - Current Affairs Saltamami 2023 (Boimate - Com)ilove9/11helloNo ratings yet

- Enquiry - Indianrail.gov - in Ntes SpecialTrains - JSPDocument1 pageEnquiry - Indianrail.gov - in Ntes SpecialTrains - JSPca_akrNo ratings yet

- Heart of The Whau - Part 2 Whau To AvondaleDocument30 pagesHeart of The Whau - Part 2 Whau To AvondaleStorm GeromeNo ratings yet

- Master Builder June2014 - 1Document40 pagesMaster Builder June2014 - 1lazybookwarmNo ratings yet

- e Drejta e PunesDocument4 pagese Drejta e PunesJon AhmetiNo ratings yet

- Rail Technology Management PerspectivesDocument43 pagesRail Technology Management PerspectivespercyNo ratings yet

- Exploring Penang on a BudgetDocument8 pagesExploring Penang on a BudgetIza AhmadNo ratings yet

- 116 Pavilion Road STS - 19 - CTMPDocument26 pages116 Pavilion Road STS - 19 - CTMPmarkomarkomarkomarkoNo ratings yet

- Design of Pedestrian Walkway at Vytilla JunctionDocument47 pagesDesign of Pedestrian Walkway at Vytilla JunctionAkhil BabuNo ratings yet

- Munications For Railway Applications K5t8u Iji8fDocument135 pagesMunications For Railway Applications K5t8u Iji8fAlfrecron Oneone100% (1)

- Other Peoples Money 1000032620Document245 pagesOther Peoples Money 1000032620Bolex75% (4)

- CG Industrial Product OverviewDocument12 pagesCG Industrial Product Overviewvanessa quispeNo ratings yet

- Utkarsh India Limited - Best Swaged Pole Manufacturer in IndiaDocument8 pagesUtkarsh India Limited - Best Swaged Pole Manufacturer in IndiaUtkarsh India LTD.No ratings yet

- Top attractions in North Goa including beaches, churches and fortsDocument43 pagesTop attractions in North Goa including beaches, churches and fortsManish542No ratings yet

- Method Statement CONVOYDocument5 pagesMethod Statement CONVOYSTEVEN DELAHUNTYNo ratings yet

- North West London Night 071016Document1 pageNorth West London Night 071016Daniel PaiusNo ratings yet

- Penta-Ocean-Kier JV diaphragm wall constructionDocument9 pagesPenta-Ocean-Kier JV diaphragm wall constructionGary LoNo ratings yet

- Peavey Bandit 112 Service ManualDocument18 pagesPeavey Bandit 112 Service ManualNosoytansolo Unabarbabonita67% (3)

- NGHV NotesDocument142 pagesNGHV NotesVignesh Kumar DevendiranNo ratings yet

- Boilers TypesDocument7 pagesBoilers TypesNazakat Ali KhosoNo ratings yet

- 1323341264382-Training ManualDocument21 pages1323341264382-Training ManualgokulvarmarajakNo ratings yet

- TD75型通用固定式带式输送机设计选用手册Document163 pagesTD75型通用固定式带式输送机设计选用手册scribdren0007No ratings yet