Professional Documents

Culture Documents

UART Spec

Uploaded by

Pronadeep Bora0 ratings0% found this document useful (0 votes)

102 views24 pagesOriginal Title

UART_spec

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

102 views24 pagesUART Spec

Uploaded by

Pronadeep BoraCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 24

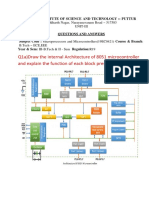

Implementation of a simplified

UART protocol in Xilinx 7

Series FPGA

UART protocol Basics

• Transmitter – Tx

• Receiver – Rx

• Serial communication

• Asynchronous (UART Tx and Rx

Basic block diagram

works @ same Baud Rate)

• Full duplex or Half duplex

• Can operate at different baud rates (4800, 9600, 14400,

19200, 38400, 57600, 115200 etc.)

Standard serial data format

UART Specification

• Simplified model

• Data format

– 1 start bit

– 1 stop bit

– No parity bit

– 8 data bits

• Composed of 3 modules

– Baud Rate Generator

– Transmitter

– Receiver

Baud Rate Generator

• Baud Rate - Number of signal changes per second (as per modem

terminology).

• Bit Rate - Number of bits transmitted per second.

• As far as the conductor wire (signal wire transmission) is concerned, the baud

rate and bps are the same, and we can use the terms interchangeably.

• Basic Idea - Baud Rate Generator module divides the System clock

by a divisor (N) to provide standard baud rate clock ( bclk ).

• Industry Standard System clock frequencies for UART

• 1.8432MHz, 2.4576MHz, 3.072MHz

• But, 7 series FPGA source clock frequency 100 MHz.

• First , it is reqd. to create a clock divider module to convert 100 MHz (10 ns )

to 1.8432 MHz ~ 1.7857 MHz (560 ns)

• Basically , divide the FPGA clock by 27 to get standard UART clock of

1.8432 MHz(approx.)

Baud Rate Generator

• The divisor N can be calculated using the formula

Frequency of System clock (1.8432 Mhz)

N =

Maximum Baud Rate Frequency 38400 X No.of samples per bit (8)x 2

= 3 ( Duty cycle of clkdiv (divided by 3) 33.33% )

Block diagram of Baud Rate Generator

Baud Rate Generator

Baud Rate (bclk ) = 38400

Different Baud rate and sampling frequencies

Timing Diagram Clk div (dvide by 3), bclk, bclk*8

UART Transmitter

• Converts a parallel data word into serial form and appends the Start and

stop bits.

• Composed of

– Transmitted bit counter

– Data shift register

– State machine and support logic

Block Diagram of transmitter

FSM UART transmitter

RTL netlist for Baud Rate Generator and Transmitter

Timing diagram of UART TX

UART Receiver

• To avoid setup and hold time problems and reading some bits at the

wrong time, the received data is sampled eight times during each bit

time

– sampled on the rising edge of bclkx8.

Data sampling points by the UART receiver.

• UART Receiver

– State machine

– De-serializer (SIPO logic) and support logic.

• The main objective -

– To detect the start-bit, then de-serialize the following bit-

stream, detect the stop-bit, and make the data available to

the host.

• No error checking Logic

• 2 counters are used

• ct1 counts the number of bclkx8 clocks

• ct2 counts the number of bits received after the start

The state machine is the Mealy machine

and composed of three states (idle, start_detected, and recv_data)

STA for UART Tx and Rx

• FPGA clock 100Mhz

– create_clock -period 10.000 -name clk_100mhz [get_ports

clk_100mhz]

• UART System clock ~1.8432Mhz

– create_generated_clock -name clk_1point8432mhz -source [get_ports

clk_100mhz] -divide_by 56 [get_pins

bdgen/a1/clk_1point8432mhz_reg/Q]

• Clkdiv (divided by 3 clock)

• create_generated_clock -name clk_div2 -source

[get_pins bdgen/a1/clk_1point8432mhz_reg/Q] -edges

{1 2 3} -edge_shift {560.000 840.000 1680.000}

[get_pins {bdgen/a2/count_mod3_reg[0]/Q}]

• bit0

– create_generated_clock -name bit0 -source [get_pins

{bdgen/a2/count_mod3_reg[1]/Q}] -divide_by 2 [get_pins

{bdgen/a3/count_8bit_reg[0]/Q}]

• bclkx8 clock

– create_generated_clock -name bclkx8 -source [get_pins

{bdgen/a3/count_8bit_reg[0]/Q}] -divide_by 1 [get_pins

bdgen/a3/bclkx8_reg/Q]

• bclk clock

– create_generated_clock -name bclk -source [get_pins

bdgen/a3/bclkx8_reg/Q] -divide_by 8 [get_pins

bdgen/a3/bclk_reg/Q]

• create_clock -period 20.000 -name vclk1

• set_input_delay -clock vclk1 1.000 [all_inputs]

• set_input_delay -clock vclk1 -min 0.500 [all_inputs]

• set_output_delay -clock vclk1 0.2500 [all_outputs]

• set_output_delay -clock vclk1 -min 0.15 [all_outputs]

• set_clock_groups -asynchronous -group clk_100mhz -group vclk1

• set_clock_groups -asynchronous -group clk_1point8432mhz -group vclk1

• set_clock_groups -asynchronous -group clk_div1 -group vclk1

• set_clock_groups -asynchronous -group bit0 -group vclk1

• set_clock_groups -asynchronous -group bclk -group vclk1

• set_clock_groups -asynchronous -group bclkx8 -group vclk1

• set_false_path -from [get_ports rst_asyn_ah]

Half Duplex communication mode!!

Standard Protocol features

• AXI4-Lite interface for register access and data

transfers.

• Transmit and receive FIFOs.

• Configurable number of data bits (5-8) in a

character.

• Configurable parity bit (odd or even or none).

• Interrupt controller logic.

You might also like

- Design of A Micro-Uart For Soc ApplicationDocument12 pagesDesign of A Micro-Uart For Soc ApplicationUtkarsh Jain100% (1)

- Apb DocDocument117 pagesApb DocVikas ZurmureNo ratings yet

- Arm Amba AhbDocument18 pagesArm Amba AhbgeethaNo ratings yet

- Amba 4axi StreamDocument2 pagesAmba 4axi StreamNGUYỄN HOÀNG LINHNo ratings yet

- AHB SignalsDocument2 pagesAHB Signalsavdhesh7No ratings yet

- UART Protocol 00 For BC3MM Module Rev1.0Document12 pagesUART Protocol 00 For BC3MM Module Rev1.0kaaashuNo ratings yet

- Interfacing and Some Common Building Blocks: Coe 111: Advanced Digital DesignDocument35 pagesInterfacing and Some Common Building Blocks: Coe 111: Advanced Digital DesignFrancisNo ratings yet

- A Synthesizable Design of Amba-Axi Protocol For Soc IntegrationDocument8 pagesA Synthesizable Design of Amba-Axi Protocol For Soc IntegrationvjemmanNo ratings yet

- RTL DesignDocument31 pagesRTL DesignBala SubramanianNo ratings yet

- Chapter 7: Register Transfer: ObjectivesDocument7 pagesChapter 7: Register Transfer: ObjectivesSteffany RoqueNo ratings yet

- Project FileDocument131 pagesProject FileshaanjalalNo ratings yet

- Lec20 RTL DesignDocument40 pagesLec20 RTL DesignVrushali patilNo ratings yet

- How To Use The Three AXI Configurations: FPGA and ASIC Technology Comparison - 1Document16 pagesHow To Use The Three AXI Configurations: FPGA and ASIC Technology Comparison - 1vpsampathNo ratings yet

- AXI To AHB BridgeDocument5 pagesAXI To AHB BridgePhilomathi AmbroseNo ratings yet

- 5 - Internal MemoryDocument22 pages5 - Internal Memoryerdvk100% (1)

- Asic Prototyping AldecDocument10 pagesAsic Prototyping AldecKhaled Abou ElseoudNo ratings yet

- AXI Implementation On SoCDocument5 pagesAXI Implementation On SoCvijaykumarn12No ratings yet

- Timing in Digital Circuits - NotesDocument9 pagesTiming in Digital Circuits - NotesKowshick GuruNo ratings yet

- APBDocument29 pagesAPBsuneeldvNo ratings yet

- Block Diagram of Intel Atom ProcessorDocument23 pagesBlock Diagram of Intel Atom Processorfestio94No ratings yet

- ASIC TimingDocument54 pagesASIC TimingKrishna MohanNo ratings yet

- PWMDocument57 pagesPWMAhmed Mortuza Saleque SaikotNo ratings yet

- Implementing A Source Synchronous Interface v2.0Document47 pagesImplementing A Source Synchronous Interface v2.0Gautham PopuriNo ratings yet

- BGK MPMC Unit-3 Q and ADocument21 pagesBGK MPMC Unit-3 Q and AMallesh ArjaNo ratings yet

- Bus System & Data TransferDocument5 pagesBus System & Data Transferlmehta16No ratings yet

- FPGA Selection for Analog Signal Conversion and Ethernet Data TransferDocument6 pagesFPGA Selection for Analog Signal Conversion and Ethernet Data TransferGurinder Pal SinghNo ratings yet

- 5468.amba Axi Ahb ApbDocument2 pages5468.amba Axi Ahb ApbLohith CoreelNo ratings yet

- How To Use The Three AXI ConfigurationsDocument14 pagesHow To Use The Three AXI ConfigurationsKiran Kumar ParlapalliNo ratings yet

- Zynq 7020Document4 pagesZynq 7020NGUYỄN HOÀNG LINHNo ratings yet

- Three Main Components of a Computer SystemDocument36 pagesThree Main Components of a Computer SystemAnshulNo ratings yet

- Single Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGADocument4 pagesSingle Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGAInternational Organization of Scientific Research (IOSR)No ratings yet

- Testability Architecture and Flow for EOCHL and Embedded IPsDocument24 pagesTestability Architecture and Flow for EOCHL and Embedded IPssenthilkumarNo ratings yet

- SOC TestingDocument27 pagesSOC TestingMaria AllenNo ratings yet

- Organization: Basic Computer Organization and DesignDocument29 pagesOrganization: Basic Computer Organization and DesignGemechisNo ratings yet

- Design and Implementation of UartDocument21 pagesDesign and Implementation of Uartbhanu455No ratings yet

- BS PDFDocument31 pagesBS PDFRohith RajNo ratings yet

- Ahb-Lite To Apb Protocol: BY Shraddha Devaiya EC - 018 Anand Therattil EC - 092Document29 pagesAhb-Lite To Apb Protocol: BY Shraddha Devaiya EC - 018 Anand Therattil EC - 092AnandNo ratings yet

- 2-3 SSUSB DevCon LinkLayer ViningDocument54 pages2-3 SSUSB DevCon LinkLayer ViningHardik TrivediNo ratings yet

- Xge Mac SpecDocument24 pagesXge Mac Spechackdrag100% (1)

- DDR SDR Sdram ComparisionDocument12 pagesDDR SDR Sdram ComparisionSrinivas CherukuNo ratings yet

- System On Chip Architecture Design Lecture21Document17 pagesSystem On Chip Architecture Design Lecture21Thi NguyenNo ratings yet

- FPGA Design MethodologiesDocument9 pagesFPGA Design MethodologiesSambhav VermanNo ratings yet

- Spyglass-Cdc: Industry Most Comprehensive, Practical, and Powerful CDC SolutionDocument2 pagesSpyglass-Cdc: Industry Most Comprehensive, Practical, and Powerful CDC SolutionRamakrishnaRao SoogooriNo ratings yet

- 03-Verilog Modules and Ports-MergedDocument170 pages03-Verilog Modules and Ports-MergedqwertyNo ratings yet

- I 2 CDocument16 pagesI 2 CelumalaianithaNo ratings yet

- AHB Lite SpecificationDocument72 pagesAHB Lite SpecificationSuyog Avinash ChutkeNo ratings yet

- AHBDocument59 pagesAHBGautham Lukkur Venugopal50% (2)

- Computer Buses and InterfacesDocument34 pagesComputer Buses and InterfacesSholeh FirmansyahNo ratings yet

- ArchitectureDocument21 pagesArchitecturepriyankaNo ratings yet

- Partitioning An ASICDocument6 pagesPartitioning An ASICSwtz ZraonicsNo ratings yet

- Complex Clocking Situations 010904Document54 pagesComplex Clocking Situations 010904maniNo ratings yet

- 03b - FIE - Parcial #3 PLD - Resumen 04c 09Document36 pages03b - FIE - Parcial #3 PLD - Resumen 04c 09amilcar93No ratings yet

- UARTDocument24 pagesUARTPronadeep BoraNo ratings yet

- UART Module Generates Serial Communication SignalsDocument21 pagesUART Module Generates Serial Communication SignalsSusie MaestreNo ratings yet

- UART Design and ImplementationDocument28 pagesUART Design and ImplementationpreetiNo ratings yet

- MC9S08QE128RMDocument346 pagesMC9S08QE128RMSergio ContrerasNo ratings yet

- UARTDocument26 pagesUARTflyingdreams100% (2)

- Introduction To MSP430 MicrocontrollersDocument32 pagesIntroduction To MSP430 MicrocontrollersAlejandro OrtizNo ratings yet

- 8b - 10b Encoding - WikipediaDocument8 pages8b - 10b Encoding - WikipediaPronadeep BoraNo ratings yet

- JESD204C primer introduces new high-speed serial link standardDocument3 pagesJESD204C primer introduces new high-speed serial link standardPronadeep BoraNo ratings yet

- What Is JESD204 and Why Should We Pay Attention To ItDocument3 pagesWhat Is JESD204 and Why Should We Pay Attention To ItPronadeep BoraNo ratings yet

- SerDes - WikipediaDocument3 pagesSerDes - WikipediaPronadeep BoraNo ratings yet

- Demystifying Deterministic Latency Within JESD204B Converters - Electronic DesignDocument11 pagesDemystifying Deterministic Latency Within JESD204B Converters - Electronic DesignPronadeep BoraNo ratings yet

- 2quickly Implement JESD204BDocument4 pages2quickly Implement JESD204BPronadeep BoraNo ratings yet

- AMBA AHB AXI Interview Questions Verification Guide PDFDocument2 pagesAMBA AHB AXI Interview Questions Verification Guide PDFPronadeep BoraNo ratings yet

- SMDP - Project - Final - Proposal - NIT - N - Draft PDFDocument17 pagesSMDP - Project - Final - Proposal - NIT - N - Draft PDFPronadeep BoraNo ratings yet

- EDN - Understanding Layers in The JESD204B Specification - A High Speed ADC Perspective, Part 2 - EDNDocument8 pagesEDN - Understanding Layers in The JESD204B Specification - A High Speed ADC Perspective, Part 2 - EDNPronadeep BoraNo ratings yet

- UARTDocument24 pagesUARTPronadeep BoraNo ratings yet

- AMBA AHB Protocol PresentationDocument45 pagesAMBA AHB Protocol Presentationachanta1291% (11)

- Amukh Expre CertifDocument1 pageAmukh Expre CertifPronadeep BoraNo ratings yet

- Asynchronous FIFO Basics for Safe Clock Domain CrossingDocument40 pagesAsynchronous FIFO Basics for Safe Clock Domain CrossingPronadeep Bora100% (1)

- Difference Between AHB and AXI - Difference BetweenDocument2 pagesDifference Between AHB and AXI - Difference BetweenPronadeep BoraNo ratings yet

- Valid Documents List PDFDocument2 pagesValid Documents List PDFAnoop DubeyNo ratings yet

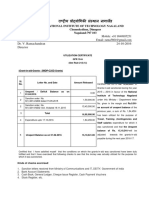

- Utilization Certificate - SMDP-1Document1 pageUtilization Certificate - SMDP-1Pronadeep BoraNo ratings yet

- AQMS NitnDocument11 pagesAQMS NitnPronadeep BoraNo ratings yet

- AXI vs AHB: Understanding the Differences Between the Two Popular ARM Bus ProtocolsDocument3 pagesAXI vs AHB: Understanding the Differences Between the Two Popular ARM Bus ProtocolsPronadeep Bora100% (2)

- V2 - Proforma For Submitting 6 MONTHLY REPORTDocument9 pagesV2 - Proforma For Submitting 6 MONTHLY REPORTPronadeep BoraNo ratings yet

- SMDP C2SDSixmonthlyProgressFinalDocument4 pagesSMDP C2SDSixmonthlyProgressFinalPronadeep BoraNo ratings yet

- Asynchronous FIFO Basics for Safe Clock Domain CrossingDocument40 pagesAsynchronous FIFO Basics for Safe Clock Domain CrossingPronadeep Bora100% (1)

- Current Project StatusDocument1 pageCurrent Project StatusPronadeep BoraNo ratings yet

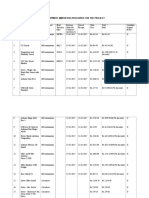

- Six Monthly Progress-Annexures (Tables)Document6 pagesSix Monthly Progress-Annexures (Tables)Pronadeep BoraNo ratings yet

- WHMS NitnDocument14 pagesWHMS NitnPronadeep BoraNo ratings yet

- Element14equipments PDFDocument1 pageElement14equipments PDFPronadeep BoraNo ratings yet

- Quotations For Components Required For SMDP ProjectDocument2 pagesQuotations For Components Required For SMDP ProjectPronadeep BoraNo ratings yet

- Six Monthly Progress-FormatDocument3 pagesSix Monthly Progress-FormatPronadeep BoraNo ratings yet

- Nit Nagaland - Pmod - Quote - DG - CoreelDocument1 pageNit Nagaland - Pmod - Quote - DG - CoreelPronadeep BoraNo ratings yet

- Digilent LABSeupimentsDocument1 pageDigilent LABSeupimentsPronadeep BoraNo ratings yet

- Apache Traffic Server - HTTP Proxy Server On The Edge PresentationDocument7 pagesApache Traffic Server - HTTP Proxy Server On The Edge Presentationchn5800inNo ratings yet

- Ifm VES004 Software For Diagnostic Electronics e 15 NDocument2 pagesIfm VES004 Software For Diagnostic Electronics e 15 Nodi odianNo ratings yet

- ITSMS Service Catalog TemplateDocument13 pagesITSMS Service Catalog TemplateMustafa AnisNo ratings yet

- Configuring MicroSCADA For Modbus Master ProtocolDocument44 pagesConfiguring MicroSCADA For Modbus Master ProtocolВиталий ГудзовскийNo ratings yet

- Server Board s1200sp BriefDocument4 pagesServer Board s1200sp BriefadisNo ratings yet

- Full Adder Using Half AdderDocument4 pagesFull Adder Using Half AdderNiraj ShettyNo ratings yet

- Remote Support Infrastructure at SAP: A Brief OverviewDocument8 pagesRemote Support Infrastructure at SAP: A Brief OverviewJeffeers PrietoNo ratings yet

- Modes and formats for end term examsDocument3 pagesModes and formats for end term examsmadhu jhaNo ratings yet

- CBLM FormatDocument49 pagesCBLM FormatGheenzo Moreno100% (1)

- Computer Organization: Virtual MemoryDocument26 pagesComputer Organization: Virtual Memorychuks felix michaelNo ratings yet

- ActivityNo1 AboutOSDocument17 pagesActivityNo1 AboutOSsheena RomNo ratings yet

- Week 3 - ClayNet - Static RoutingDocument8 pagesWeek 3 - ClayNet - Static RoutingvihNo ratings yet

- Step 1 - LAN Networks ConfigurationDocument10 pagesStep 1 - LAN Networks ConfigurationabduasdfNo ratings yet

- School ICT Equipment InventoryDocument8 pagesSchool ICT Equipment InventoryLea YaonaNo ratings yet

- Quick DrawDocument1 pageQuick DrawRam RangNo ratings yet

- Spring 2023 - CS001 - 1Document3 pagesSpring 2023 - CS001 - 1XeroxNo ratings yet

- Session - I Microprocessors-The Solution in Search of ProblemsDocument75 pagesSession - I Microprocessors-The Solution in Search of ProblemsSarunkumar BalathNo ratings yet

- Subnetting ProblemsDocument10 pagesSubnetting ProblemsnonamedagNo ratings yet

- Ipv6 Cheat SheetDocument2 pagesIpv6 Cheat SheetKarlNo ratings yet

- Uc3 Aula 1 Manual Novo Virtual Box 6.1Document242 pagesUc3 Aula 1 Manual Novo Virtual Box 6.1Prof. Tercio RibeiroNo ratings yet

- infoPLC Net ErrorCodes 2015-02-05Document556 pagesinfoPLC Net ErrorCodes 2015-02-05Ivan Cordero ValerianoNo ratings yet

- Interrupts: How To Do 2 Things at The Same TimeDocument22 pagesInterrupts: How To Do 2 Things at The Same TimePaul CockshottNo ratings yet

- Ciena Switch ScriptDocument2 pagesCiena Switch ScriptSahil PatilNo ratings yet

- Error Flow ControlDocument48 pagesError Flow ControlMohd ShifanNo ratings yet

- TIBCO Spotfire - SupportDocument5 pagesTIBCO Spotfire - SupportrajisgoodNo ratings yet

- Gainward Gts 250Document2 pagesGainward Gts 250Vittorio PolveriniNo ratings yet

- C# Background Worker TutorialDocument12 pagesC# Background Worker TutorialKRAZA2092No ratings yet

- Harman Kardon AVR 635/AVR 435 Firmware/Software Upgrade InstructionsDocument2 pagesHarman Kardon AVR 635/AVR 435 Firmware/Software Upgrade InstructionsChristopher HerronNo ratings yet

- Net FlowDocument35 pagesNet FlowBabu GothNo ratings yet

- EP2C621D16GMDocument83 pagesEP2C621D16GMtolvanen.suloNo ratings yet