Professional Documents

Culture Documents

Si 5344

Uploaded by

Steve Jeon0 ratings0% found this document useful (0 votes)

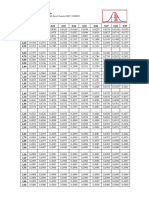

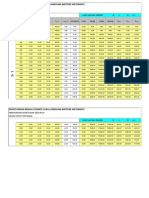

35 views17 pagesThis document contains 465 register writes for configuring a Silicon Labs Si5344 Rev D clock generator chip. It was generated by a Silicon Labs ClockBuilder Pro export tool and includes preamble, configuration, and post-write control registers to fully configure the device. The registers control various settings and parameters of the chip like output frequencies, power levels, and calibration controls.

Original Description:

Original Title

si5344

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document contains 465 register writes for configuring a Silicon Labs Si5344 Rev D clock generator chip. It was generated by a Silicon Labs ClockBuilder Pro export tool and includes preamble, configuration, and post-write control registers to fully configure the device. The registers control various settings and parameters of the chip like output frequencies, power levels, and calibration controls.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

35 views17 pagesSi 5344

Uploaded by

Steve JeonThis document contains 465 register writes for configuring a Silicon Labs Si5344 Rev D clock generator chip. It was generated by a Silicon Labs ClockBuilder Pro export tool and includes preamble, configuration, and post-write control registers to fully configure the device. The registers control various settings and parameters of the chip like output frequencies, power levels, and calibration controls.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 17

1 /*

2 * Si5344 Rev D Configuration Register Export Header File

3 *

4 * This file represents a series of Silicon Labs Si5344 Rev D

5 * register writes that can be performed to load a single configuration

6 * on a device. It was created by a Silicon Labs ClockBuilder Pro

7 * export tool.

8 *

9 * Part: Si5344 Rev D

10 * Design ID:

11 * Includes Pre/Post Download Control Register Writes: Yes

12 * Created By: ClockBuilder Pro v2.34.1

[2019-05-31]

13 * Timestamp: 2019-08-26 10:47:11 GMT-07:00

14 *

15 * A complete design report corresponding to this export is included at the end

16 * of this header file.

17 *

18 */

19

20 #ifndef SI5344_REVD_REG_CONFIG_HEADER

21 #define SI5344_REVD_REG_CONFIG_HEADER

22

23 #define SI5344_REVD_REG_CONFIG_NUM_REGS 465

24

25 typedef struct

26 {

27 unsigned int address; /* 16-bit register address */

28 unsigned char value; /* 8-bit register data */

29

30 } si5344_revd_register_t;

31

32 si5344_revd_register_t const si5344_revd_registers[SI5344_REVD_REG_CONFIG_NUM_REGS] =

33 {

34

35 /* Start configuration preamble */

36 { 0x0B24, 0xC0 },

37 { 0x0B25, 0x00 },

38 { 0x0540, 0x01 },

39 /* End configuration preamble */

40

41 /* Delay 300 msec */

42 /* Delay is worst case time for device to complete any calibration */

43 /* that is running due to device state change previous to this script */

44 /* being processed. */

45

46 /* Start configuration registers */

47 { 0x0006, 0x00 },

48 { 0x0007, 0x00 },

49 { 0x0008, 0x00 },

50 { 0x000B, 0x68 },

51 { 0x0016, 0x02 },

52 { 0x0017, 0xDC },

53 { 0x0018, 0xCC },

54 { 0x0019, 0xDD },

55 { 0x001A, 0xDF },

56 { 0x002B, 0x02 },

57 { 0x002C, 0x03 },

58 { 0x002D, 0x05 },

59 { 0x002E, 0x3A },

60 { 0x002F, 0x00 },

61 { 0x0030, 0x3A },

62 { 0x0031, 0x00 },

63 { 0x0032, 0x00 },

64 { 0x0033, 0x00 },

65 { 0x0034, 0x00 },

66 { 0x0035, 0x00 },

67 { 0x0036, 0x3A },

68 { 0x0037, 0x00 },

69 { 0x0038, 0x3A },

70 { 0x0039, 0x00 },

71 { 0x003A, 0x00 },

72 { 0x003B, 0x00 },

73 { 0x003C, 0x00 },

74 { 0x003D, 0x00 },

75 { 0x003F, 0x33 },

76 { 0x0040, 0x04 },

77 { 0x0041, 0x0B },

78 { 0x0042, 0x0B },

79 { 0x0043, 0x00 },

80 { 0x0044, 0x00 },

81 { 0x0045, 0x0C },

82 { 0x0046, 0x64 },

83 { 0x0047, 0x64 },

84 { 0x0048, 0x00 },

85 { 0x0049, 0x00 },

86 { 0x004A, 0x64 },

87 { 0x004B, 0x64 },

88 { 0x004C, 0x00 },

89 { 0x004D, 0x00 },

90 { 0x004E, 0x55 },

91 { 0x004F, 0x00 },

92 { 0x0050, 0x0F },

93 { 0x0051, 0x03 },

94 { 0x0052, 0x03 },

95 { 0x0053, 0x00 },

96 { 0x0054, 0x00 },

97 { 0x0055, 0x03 },

98 { 0x0056, 0x03 },

99 { 0x0057, 0x00 },

100 { 0x0058, 0x00 },

101 { 0x0059, 0x05 },

102 { 0x005A, 0x7B },

103 { 0x005B, 0x09 },

104 { 0x005C, 0xED },

105 { 0x005D, 0x00 },

106 { 0x005E, 0x7B },

107 { 0x005F, 0x09 },

108 { 0x0060, 0xED },

109 { 0x0061, 0x00 },

110 { 0x0062, 0x00 },

111 { 0x0063, 0x00 },

112 { 0x0064, 0x00 },

113 { 0x0065, 0x00 },

114 { 0x0066, 0x00 },

115 { 0x0067, 0x00 },

116 { 0x0068, 0x00 },

117 { 0x0069, 0x00 },

118 { 0x0092, 0x02 },

119 { 0x0093, 0x70 },

120 { 0x0095, 0x00 },

121 { 0x0096, 0x80 },

122 { 0x0098, 0x60 },

123 { 0x009A, 0x02 },

124 { 0x009B, 0x40 },

125 { 0x009D, 0x00 },

126 { 0x009E, 0x40 },

127 { 0x00A0, 0x20 },

128 { 0x00A2, 0x00 },

129 { 0x00A9, 0x80 },

130 { 0x00AA, 0xC1 },

131 { 0x00AB, 0x00 },

132 { 0x00AC, 0x00 },

133 { 0x00E5, 0x21 },

134 { 0x00EA, 0x15 },

135 { 0x00EB, 0xC0 },

136 { 0x00EC, 0x00 },

137 { 0x00ED, 0x00 },

138 { 0x0102, 0x01 },

139 { 0x0112, 0x06 },

140 { 0x0113, 0x09 },

141 { 0x0114, 0x3E },

142 { 0x0115, 0x18 },

143 { 0x0117, 0x06 },

144 { 0x0118, 0x09 },

145 { 0x0119, 0x3E },

146 { 0x011A, 0x18 },

147 { 0x0126, 0x06 },

148 { 0x0127, 0x09 },

149 { 0x0128, 0x3E },

150 { 0x0129, 0x18 },

151 { 0x012B, 0x01 },

152 { 0x012C, 0x09 },

153 { 0x012D, 0x3B },

154 { 0x012E, 0x28 },

155 { 0x013F, 0x00 },

156 { 0x0140, 0x00 },

157 { 0x0141, 0x40 },

158 { 0x0142, 0xFF },

159 { 0x0206, 0x00 },

160 { 0x0208, 0x0D },

161 { 0x0209, 0x00 },

162 { 0x020A, 0x00 },

163 { 0x020B, 0x00 },

164 { 0x020C, 0x00 },

165 { 0x020D, 0x00 },

166 { 0x020E, 0x01 },

167 { 0x020F, 0x00 },

168 { 0x0210, 0x00 },

169 { 0x0211, 0x00 },

170 { 0x0212, 0x0D },

171 { 0x0213, 0x00 },

172 { 0x0214, 0x00 },

173 { 0x0215, 0x00 },

174 { 0x0216, 0x00 },

175 { 0x0217, 0x00 },

176 { 0x0218, 0x01 },

177 { 0x0219, 0x00 },

178 { 0x021A, 0x00 },

179 { 0x021B, 0x00 },

180 { 0x021C, 0x00 },

181 { 0x021D, 0x00 },

182 { 0x021E, 0x00 },

183 { 0x021F, 0x00 },

184 { 0x0220, 0x00 },

185 { 0x0221, 0x00 },

186 { 0x0222, 0x00 },

187 { 0x0223, 0x00 },

188 { 0x0224, 0x00 },

189 { 0x0225, 0x00 },

190 { 0x0226, 0x00 },

191 { 0x0227, 0x00 },

192 { 0x0228, 0x00 },

193 { 0x0229, 0x00 },

194 { 0x022A, 0x00 },

195 { 0x022B, 0x00 },

196 { 0x022C, 0x00 },

197 { 0x022D, 0x00 },

198 { 0x022E, 0x00 },

199 { 0x022F, 0x00 },

200 { 0x0231, 0x0B },

201 { 0x0232, 0x0B },

202 { 0x0233, 0x0B },

203 { 0x0234, 0x0B },

204 { 0x0235, 0x00 },

205 { 0x0236, 0x00 },

206 { 0x0237, 0x60 },

207 { 0x0238, 0x14 },

208 { 0x0239, 0x90 },

209 { 0x023A, 0x00 },

210 { 0x023B, 0x00 },

211 { 0x023C, 0x00 },

212 { 0x023D, 0x00 },

213 { 0x023E, 0x90 },

214 { 0x0250, 0x00 },

215 { 0x0251, 0x00 },

216 { 0x0252, 0x00 },

217 { 0x0253, 0x00 },

218 { 0x0254, 0x00 },

219 { 0x0255, 0x00 },

220 { 0x025C, 0x00 },

221 { 0x025D, 0x00 },

222 { 0x025E, 0x00 },

223 { 0x025F, 0x00 },

224 { 0x0260, 0x00 },

225 { 0x0261, 0x00 },

226 { 0x026B, 0x00 },

227 { 0x026C, 0x00 },

228 { 0x026D, 0x00 },

229 { 0x026E, 0x00 },

230 { 0x026F, 0x00 },

231 { 0x0270, 0x00 },

232 { 0x0271, 0x00 },

233 { 0x0272, 0x00 },

234 { 0x028A, 0x00 },

235 { 0x028B, 0x00 },

236 { 0x028C, 0x00 },

237 { 0x028D, 0x00 },

238 { 0x028E, 0x00 },

239 { 0x028F, 0x00 },

240 { 0x0290, 0x00 },

241 { 0x0291, 0x00 },

242 { 0x0294, 0xA0 },

243 { 0x0296, 0x00 },

244 { 0x0297, 0x02 },

245 { 0x0299, 0x02 },

246 { 0x029D, 0x0A },

247 { 0x029E, 0x07 },

248 { 0x029F, 0x00 },

249 { 0x02A9, 0x99 },

250 { 0x02AA, 0x09 },

251 { 0x02AB, 0x00 },

252 { 0x02B7, 0xFF },

253 { 0x0302, 0x00 },

254 { 0x0303, 0x00 },

255 { 0x0304, 0x00 },

256 { 0x0305, 0xC4 },

257 { 0x0306, 0x10 },

258 { 0x0307, 0x00 },

259 { 0x0308, 0x00 },

260 { 0x0309, 0x00 },

261 { 0x030A, 0x00 },

262 { 0x030B, 0xC8 },

263 { 0x030C, 0x00 },

264 { 0x030D, 0x00 },

265 { 0x030E, 0x00 },

266 { 0x030F, 0x00 },

267 { 0x0310, 0x00 },

268 { 0x0311, 0x00 },

269 { 0x0312, 0x00 },

270 { 0x0313, 0x00 },

271 { 0x0314, 0x00 },

272 { 0x0315, 0x00 },

273 { 0x0316, 0x00 },

274 { 0x0317, 0x00 },

275 { 0x0318, 0x00 },

276 { 0x0319, 0x00 },

277 { 0x031A, 0x00 },

278 { 0x031B, 0x00 },

279 { 0x031C, 0x00 },

280 { 0x031D, 0x00 },

281 { 0x031E, 0x00 },

282 { 0x031F, 0x00 },

283 { 0x0320, 0x00 },

284 { 0x0321, 0x00 },

285 { 0x0322, 0x00 },

286 { 0x0323, 0x00 },

287 { 0x0324, 0x00 },

288 { 0x0325, 0x00 },

289 { 0x0326, 0x00 },

290 { 0x0327, 0x00 },

291 { 0x0328, 0x00 },

292 { 0x0329, 0x00 },

293 { 0x032A, 0x00 },

294 { 0x032B, 0x00 },

295 { 0x032C, 0x00 },

296 { 0x032D, 0x00 },

297 { 0x0338, 0x00 },

298 { 0x0339, 0x1E },

299 { 0x033B, 0x21 },

300 { 0x033C, 0x1C },

301 { 0x033D, 0x00 },

302 { 0x033E, 0x00 },

303 { 0x033F, 0x00 },

304 { 0x0340, 0x00 },

305 { 0x0341, 0x00 },

306 { 0x0342, 0x00 },

307 { 0x0343, 0x00 },

308 { 0x0344, 0x00 },

309 { 0x0345, 0x00 },

310 { 0x0346, 0x00 },

311 { 0x0347, 0x00 },

312 { 0x0348, 0x00 },

313 { 0x0349, 0x00 },

314 { 0x034A, 0x00 },

315 { 0x034B, 0x00 },

316 { 0x034C, 0x00 },

317 { 0x034D, 0x00 },

318 { 0x034E, 0x00 },

319 { 0x034F, 0x00 },

320 { 0x0350, 0x00 },

321 { 0x0351, 0x00 },

322 { 0x0352, 0x00 },

323 { 0x0359, 0x00 },

324 { 0x035A, 0x00 },

325 { 0x035B, 0x00 },

326 { 0x035C, 0x00 },

327 { 0x035D, 0x00 },

328 { 0x035E, 0x00 },

329 { 0x035F, 0x00 },

330 { 0x0360, 0x00 },

331 { 0x0487, 0x00 },

332 { 0x0508, 0x14 },

333 { 0x0509, 0x23 },

334 { 0x050A, 0x0C },

335 { 0x050B, 0x0B },

336 { 0x050C, 0x03 },

337 { 0x050D, 0x3F },

338 { 0x050E, 0x16 },

339 { 0x050F, 0x29 },

340 { 0x0510, 0x0A },

341 { 0x0511, 0x09 },

342 { 0x0512, 0x03 },

343 { 0x0513, 0x3F },

344 { 0x0515, 0x00 },

345 { 0x0516, 0x00 },

346 { 0x0517, 0x80 },

347 { 0x0518, 0x0E },

348 { 0x0519, 0x83 },

349 { 0x051A, 0x03 },

350 { 0x051B, 0x00 },

351 { 0x051C, 0x00 },

352 { 0x051D, 0x00 },

353 { 0x051E, 0x00 },

354 { 0x051F, 0xA0 },

355 { 0x0521, 0x3B },

356 { 0x052A, 0x01 },

357 { 0x052B, 0x01 },

358 { 0x052C, 0x87 },

359 { 0x052D, 0x03 },

360 { 0x052E, 0x19 },

361 { 0x052F, 0x19 },

362 { 0x0531, 0x00 },

363 { 0x0532, 0x63 },

364 { 0x0533, 0x03 },

365 { 0x0534, 0x00 },

366 { 0x0535, 0x00 },

367 { 0x0536, 0x04 },

368 { 0x0537, 0x00 },

369 { 0x0538, 0x00 },

370 { 0x0539, 0x00 },

371 { 0x053A, 0x02 },

372 { 0x053B, 0x03 },

373 { 0x053C, 0x00 },

374 { 0x053D, 0x11 },

375 { 0x053E, 0x06 },

376 { 0x0589, 0x0D },

377 { 0x058A, 0x00 },

378 { 0x059B, 0xFA },

379 { 0x059D, 0x14 },

380 { 0x059E, 0x25 },

381 { 0x059F, 0x0C },

382 { 0x05A0, 0x0B },

383 { 0x05A1, 0x03 },

384 { 0x05A2, 0x3F },

385 { 0x05A6, 0x0B },

386 { 0x0802, 0x35 },

387 { 0x0803, 0x05 },

388 { 0x0804, 0x00 },

389 { 0x0805, 0x00 },

390 { 0x0806, 0x00 },

391 { 0x0807, 0x00 },

392 { 0x0808, 0x00 },

393 { 0x0809, 0x00 },

394 { 0x080A, 0x00 },

395 { 0x080B, 0x00 },

396 { 0x080C, 0x00 },

397 { 0x080D, 0x00 },

398 { 0x080E, 0x00 },

399 { 0x080F, 0x00 },

400 { 0x0810, 0x00 },

401 { 0x0811, 0x00 },

402 { 0x0812, 0x00 },

403 { 0x0813, 0x00 },

404 { 0x0814, 0x00 },

405 { 0x0815, 0x00 },

406 { 0x0816, 0x00 },

407 { 0x0817, 0x00 },

408 { 0x0818, 0x00 },

409 { 0x0819, 0x00 },

410 { 0x081A, 0x00 },

411 { 0x081B, 0x00 },

412 { 0x081C, 0x00 },

413 { 0x081D, 0x00 },

414 { 0x081E, 0x00 },

415 { 0x081F, 0x00 },

416 { 0x0820, 0x00 },

417 { 0x0821, 0x00 },

418 { 0x0822, 0x00 },

419 { 0x0823, 0x00 },

420 { 0x0824, 0x00 },

421 { 0x0825, 0x00 },

422 { 0x0826, 0x00 },

423 { 0x0827, 0x00 },

424 { 0x0828, 0x00 },

425 { 0x0829, 0x00 },

426 { 0x082A, 0x00 },

427 { 0x082B, 0x00 },

428 { 0x082C, 0x00 },

429 { 0x082D, 0x00 },

430 { 0x082E, 0x00 },

431 { 0x082F, 0x00 },

432 { 0x0830, 0x00 },

433 { 0x0831, 0x00 },

434 { 0x0832, 0x00 },

435 { 0x0833, 0x00 },

436 { 0x0834, 0x00 },

437 { 0x0835, 0x00 },

438 { 0x0836, 0x00 },

439 { 0x0837, 0x00 },

440 { 0x0838, 0x00 },

441 { 0x0839, 0x00 },

442 { 0x083A, 0x00 },

443 { 0x083B, 0x00 },

444 { 0x083C, 0x00 },

445 { 0x083D, 0x00 },

446 { 0x083E, 0x00 },

447 { 0x083F, 0x00 },

448 { 0x0840, 0x00 },

449 { 0x0841, 0x00 },

450 { 0x0842, 0x00 },

451 { 0x0843, 0x00 },

452 { 0x0844, 0x00 },

453 { 0x0845, 0x00 },

454 { 0x0846, 0x00 },

455 { 0x0847, 0x00 },

456 { 0x0848, 0x00 },

457 { 0x0849, 0x00 },

458 { 0x084A, 0x00 },

459 { 0x084B, 0x00 },

460 { 0x084C, 0x00 },

461 { 0x084D, 0x00 },

462 { 0x084E, 0x00 },

463 { 0x084F, 0x00 },

464 { 0x0850, 0x00 },

465 { 0x0851, 0x00 },

466 { 0x0852, 0x00 },

467 { 0x0853, 0x00 },

468 { 0x0854, 0x00 },

469 { 0x0855, 0x00 },

470 { 0x0856, 0x00 },

471 { 0x0857, 0x00 },

472 { 0x0858, 0x00 },

473 { 0x0859, 0x00 },

474 { 0x085A, 0x00 },

475 { 0x085B, 0x00 },

476 { 0x085C, 0x00 },

477 { 0x085D, 0x00 },

478 { 0x085E, 0x00 },

479 { 0x085F, 0x00 },

480 { 0x0860, 0x00 },

481 { 0x0861, 0x00 },

482 { 0x090E, 0x02 },

483 { 0x0943, 0x00 },

484 { 0x0949, 0x03 },

485 { 0x094A, 0x03 },

486 { 0x094E, 0x49 },

487 { 0x094F, 0x02 },

488 { 0x095E, 0x00 },

489 { 0x0A02, 0x00 },

490 { 0x0A03, 0x01 },

491 { 0x0A04, 0x00 },

492 { 0x0A05, 0x01 },

493 { 0x0A14, 0x00 },

494 { 0x0A1A, 0x00 },

495 { 0x0A20, 0x00 },

496 { 0x0A26, 0x00 },

497 { 0x0B44, 0x0F },

498 { 0x0B46, 0x00 },

499 { 0x0B47, 0x0C },

500 { 0x0B48, 0x0C },

501 { 0x0B4A, 0x0E },

502 { 0x0B57, 0xF0 },

503 { 0x0B58, 0x00 },

504 /* End configuration registers */

505

506 /* Start configuration postamble */

507 { 0x0514, 0x01 },

508 { 0x001C, 0x01 },

509 { 0x0540, 0x00 },

510 { 0x0B24, 0xC3 },

511 { 0x0B25, 0x02 },

512 /* End configuration postamble */

513

514 };

515

516 /*

517 * Design Report

518 *

519 * Overview

520 * ========

521 * Part: Si5344AB Rev D

522 * Project File: C:\Proj\Document\ENG\Si5344\Si5344-25m-322m_10ge_v1.slabtimeproj

523 * Design ID: <none>

524 * Created By: ClockBuilder Pro v2.34.1 [2019-05-31]

525 * Timestamp: 2019-08-26 10:47:11 GMT-07:00

526 *

527 * Design Rule Check

528 * =================

529 * Errors:

530 * - No errors

531 *

532 * Warnings:

533 * - IN0: LOS threshold “set for me” mode is recommended when hitless switching is

enabled [1]

534 * - IN1: LOS threshold “set for me” mode is recommended when hitless switching is

enabled [1]

535 *

536 * Footnotes:

537 * [1] Assert and de-assert thresholds are critical to optimum hitless switching

performance. When “set for me” is checked on the LOS page, LOS thresholds will be

calculated and updated based on your design’s frequency plan.

538 *

539 * Device Grade

540 * ============

541 * Maximum Output Frequency: 322.265625 MHz

542 * Frequency Synthesis Mode: Fractional

543 * Frequency Plan Grade: B

544 * Minimum Base OPN: Si5344B*

545 *

546 * Base Output Clock Supported Frequency Synthesis Modes

547 * OPN Grade Frequency Range (Typical Jitter)

548 * --------- ------------------- --------------------------------------------

549 * Si5344A 100 Hz to 1.028 GHz Integer (< 100 fs) and fractional (< 150 fs)

550 * Si5344B* 100 Hz to 350 MHz "

551 * Si5344C 100 Hz to 1.028 GHz Integer only (< 100 fs)

552 * Si5344D 100 Hz to 350 MHz "

553 *

554 * * Based on your calculated frequency plan, a Si5344B grade device is

555 * sufficient for your design. For more in-system configuration flexibility

556 * (higher frequencies and/or to enable fractional synthesis), consider

557 * selecting device grade Si5344A when specifying an ordering part number (OPN)

558 * for your application. See the datasheet Ordering Guide for more information.

559 *

560 * Design

561 * ======

562 * Host Interface:

563 * I/O Power Supply: VDD (Core)

564 * SPI Mode: 4-Wire

565 * I2C Address Range: 104d to 107d / 0x68 to 0x6B (selected via A0/A1 pins)

566 *

567 * XA/XB:

568 * 54 MHz (XTAL - Crystal)

569 *

570 * Inputs:

571 * IN0: 25 MHz

572 * Standard

573 * IN1: 25 MHz

574 * Standard

575 * IN2: Unused

576 * IN3: Unused

577 *

578 * Outputs:

579 * OUT0: 322.265625 MHz

580 * Enabled, LVDS 1.8 V

581 * OUT1: 322.265625 MHz

582 * Enabled, LVDS 1.8 V

583 * OUT2: 322.265625 MHz

584 * Enabled, LVDS 1.8 V

585 * OUT3: Unused

586 *

587 * Frequency Plan

588 * ==============

589 * Fvco = 13.831640625 GHz

590 * Fpfd = 1.9230769230769230... MHz [ 1 + 12/13 MHz ]

591 * Fms0 = 644.53125 MHz

592 *

593 * P dividers:

594 * P0 = 13

595 * P1 = 13

596 * P2 = Unused

597 * P3 = Unused

598 * Pxaxb = 1

599 *

600 * MXAXB = 256.1414930555555555... [ 256 + 163/1152 ]

601 * M = 1438.490625

602 * N dividers:

603 * N0:

604 * Value: 21.46

605 * OUT0: 322.265625 MHz [ 322 + 17/64 MHz ]

606 * OUT1: 322.265625 MHz [ 322 + 17/64 MHz ]

607 * OUT2: 322.265625 MHz [ 322 + 17/64 MHz ]

608 * N1:

609 * Unused

610 * N2:

611 * Unused

612 * N3:

613 * Unused

614 *

615 * R dividers:

616 * R0 = 2

617 * R1 = 2

618 * R2 = 2

619 * R3 = Unused

620 *

621 * Nominal Bandwidth:

622 * Desired: 80.000 Hz

623 * Actual: 94.787 Hz

624 * Coefficients:

625 * BW0: 20

626 * BW1: 35

627 * BW2: 12

628 * BW3: 11

629 * BW4: 3

630 * BW5: 63

631 * Fastlock Bandwidth:

632 * Desired: 4.000 kHz

633 * Actual: 379.325 Hz

634 * Coefficients:

635 * BW0: 22

636 * BW1: 41

637 * BW2: 10

638 * BW3: 9

639 * BW4: 3

640 * BW5: 63

641 * Holdover Bandwidth:

642 * N/A (Ramped Exit from Holdover)

643 *

644 * Dividers listed above show effective values. These values are translated to register

settings by ClockBuilder Pro. For the actual register values, see below. Refer to the

Family Reference Manual for information on registers related to frequency plan.

645 *

646 * Digitally Controlled Oscillator (DCO)

647 * =====================================

648 * Mode: FINC/FDEC

649 *

650 * Fvco * Nx_DEN

651 * Fout = --------------------------

652 * (Nx_NUM ± n*Nx_FSTEPW) * R

653 *

654 * N0: DCO Enabled

655 *

656 * Fvco: 13.831640625 GHz

657 * N0_NUM: 72007811072

658 * N0_DEN: 3355443200

659 * N0_FSTEPW: 7201

660 *

661 * Desired Step Size: 0.1 ppm

662 * Actual Step Size: 0.100003049848... ppm

663 * Range: 150 ppm

664 *

665 * OUT0

666 * R0: 2

667 * Initial Freq: 322.265625 MHz

668 * Step Size: 32.227545361366... Hz

669 * Min Freq: 322.217323155001... MHz

670 * Max Freq: 322.313941328503... MHz

671 *

672 * OUT1

673 * R1: 2

674 * Initial Freq: 322.265625 MHz

675 * Step Size: 32.227545361366... Hz

676 * Min Freq: 322.217323155001... MHz

677 * Max Freq: 322.313941328503... MHz

678 *

679 * OUT2

680 * R2: 2

681 * Initial Freq: 322.265625 MHz

682 * Step Size: 32.227545361366... Hz

683 * Min Freq: 322.217323155001... MHz

684 * Max Freq: 322.313941328503... MHz

685 *

686 * N1: DCO Disabled

687 *

688 * N2: DCO Disabled

689 *

690 * N3: DCO Disabled

691 *

692 * Estimated Power & Junction Temperature

693 * ======================================

694 * Assumptions:

695 *

696 * Revision: D

697 * VDD: 1.8 V

698 * Ta: 25 °C

699 * Theta-JA: 18.4 °C/W

700 * Airflow: 2 m/s

701 *

702 * Total Power: 697 mW, On Chip Power: 679 mW, Tj: 37 °C

703 *

704 * Frequency Format Voltage Current Power

705 * -------------- ------ -------- -------- --------

706 * VDD 1.8 V 124.4 mA 224 mW

707 * VDDA 3.3 V 116.4 mA 384 mW

708 * VDDO0 322.265625 MHz LVDS 1.8 V 16.4 mA 30 mW

709 * VDDO1 322.265625 MHz LVDS 1.8 V 16.4 mA 30 mW

710 * VDDO2 322.265625 MHz LVDS 1.8 V 16.4 mA 30 mW

711 * VDDO3 Unused

712 * -------- --------

713 * Total 290.2 mA 697 mW

714 *

715 * Note:

716 *

717 * -Tj is junction temperature. Tj must be less than 125 °C (on Si5344 Revision D) for

device to comply with datasheet specifications. Tj = Ta + Theta_JA*On_Chip_Power.

718 * -Overall power includes on-chip power dissipation and adds differential load power

dissipation to estimate total power requirements.

719 * -Above are estimates only: power and temperature should be measured on your PCB.

720 * -Selection of appropriate Theta-JA is required for most accurate estimate. Ideally,

select 'User Specified Theta-JA' and enter a Theta-JA value based on the thermal

properties of your PCB.

721 *

722 * Settings

723 * ========

724 *

725 * Location Setting Name Decimal Value Hex Value

726 * ------------ --------------------- ----------------- -----------------

727 * 0x0006[23:0] TOOL_VERSION 0 0x000000

728 * 0x000B[6:0] I2C_ADDR 104 0x68

729 * 0x0016[1] LOL_ON_HOLD 1 0x1

730 * 0x0017[0] SYSINCAL_INTR_MSK 0 0x0

731 * 0x0017[1] LOSXAXB_INTR_MSK 0 0x0

732 * 0x0017[5] SMB_TMOUT_INTR_MSK 0 0x0

733 * 0x0018[3:0] LOS_INTR_MSK 12 0xC

734 * 0x0018[7:4] OOF_INTR_MSK 12 0xC

735 * 0x0019[1] LOL_INTR_MSK 0 0x0

736 * 0x0019[5] HOLD_INTR_MSK 0 0x0

737 * 0x001A[5] CAL_INTR_MSK 0 0x0

738 * 0x002B[3] SPI_3WIRE 0 0x0

739 * 0x002B[5] AUTO_NDIV_UPDATE 0 0x0

740 * 0x002C[3:0] LOS_EN 3 0x3

741 * 0x002C[4] LOSXAXB_DIS 0 0x0

742 * 0x002D[1:0] LOS0_VAL_TIME 1 0x1

743 * 0x002D[3:2] LOS1_VAL_TIME 1 0x1

744 * 0x002D[5:4] LOS2_VAL_TIME 0 0x0

745 * 0x002D[7:6] LOS3_VAL_TIME 0 0x0

746 * 0x002E[15:0] LOS0_TRG_THR 58 0x003A

747 * 0x0030[15:0] LOS1_TRG_THR 58 0x003A

748 * 0x0032[15:0] LOS2_TRG_THR 0 0x0000

749 * 0x0034[15:0] LOS3_TRG_THR 0 0x0000

750 * 0x0036[15:0] LOS0_CLR_THR 58 0x003A

751 * 0x0038[15:0] LOS1_CLR_THR 58 0x003A

752 * 0x003A[15:0] LOS2_CLR_THR 0 0x0000

753 * 0x003C[15:0] LOS3_CLR_THR 0 0x0000

754 * 0x003F[3:0] OOF_EN 3 0x3

755 * 0x003F[7:4] FAST_OOF_EN 3 0x3

756 * 0x0040[2:0] OOF_REF_SEL 4 0x4

757 * 0x0041[4:0] OOF0_DIV_SEL 11 0x0B

758 * 0x0042[4:0] OOF1_DIV_SEL 11 0x0B

759 * 0x0043[4:0] OOF2_DIV_SEL 0 0x00

760 * 0x0044[4:0] OOF3_DIV_SEL 0 0x00

761 * 0x0045[4:0] OOFXO_DIV_SEL 12 0x0C

762 * 0x0046[7:0] OOF0_SET_THR 100 0x64

763 * 0x0047[7:0] OOF1_SET_THR 100 0x64

764 * 0x0048[7:0] OOF2_SET_THR 0 0x00

765 * 0x0049[7:0] OOF3_SET_THR 0 0x00

766 * 0x004A[7:0] OOF0_CLR_THR 100 0x64

767 * 0x004B[7:0] OOF1_CLR_THR 100 0x64

768 * 0x004C[7:0] OOF2_CLR_THR 0 0x00

769 * 0x004D[7:0] OOF3_CLR_THR 0 0x00

770 * 0x004E[2:0] OOF0_DETWIN_SEL 5 0x5

771 * 0x004E[6:4] OOF1_DETWIN_SEL 5 0x5

772 * 0x004F[2:0] OOF2_DETWIN_SEL 0 0x0

773 * 0x004F[6:4] OOF3_DETWIN_SEL 0 0x0

774 * 0x0050[3:0] OOF_ON_LOS 15 0xF

775 * 0x0051[3:0] FAST_OOF0_SET_THR 3 0x3

776 * 0x0052[3:0] FAST_OOF1_SET_THR 3 0x3

777 * 0x0053[3:0] FAST_OOF2_SET_THR 0 0x0

778 * 0x0054[3:0] FAST_OOF3_SET_THR 0 0x0

779 * 0x0055[3:0] FAST_OOF0_CLR_THR 3 0x3

780 * 0x0056[3:0] FAST_OOF1_CLR_THR 3 0x3

781 * 0x0057[3:0] FAST_OOF2_CLR_THR 0 0x0

782 * 0x0058[3:0] FAST_OOF3_CLR_THR 0 0x0

783 * 0x0059[1:0] FAST_OOF0_DETWIN_SEL 1 0x1

784 * 0x0059[3:2] FAST_OOF1_DETWIN_SEL 1 0x1

785 * 0x0059[5:4] FAST_OOF2_DETWIN_SEL 0 0x0

786 * 0x0059[7:6] FAST_OOF3_DETWIN_SEL 0 0x0

787 * 0x005A[25:0] OOF0_RATIO_REF 15534459 0x0ED097B

788 * 0x005E[25:0] OOF1_RATIO_REF 15534459 0x0ED097B

789 * 0x0062[25:0] OOF2_RATIO_REF 0 0x0000000

790 * 0x0066[25:0] OOF3_RATIO_REF 0 0x0000000

791 * 0x0092[1] LOL_FST_EN 1 0x1

792 * 0x0093[7:4] LOL_FST_DETWIN_SEL 7 0x7

793 * 0x0095[3:2] LOL_FST_VALWIN_SEL 0 0x0

794 * 0x0096[7:4] LOL_FST_SET_THR_SEL 8 0x8

795 * 0x0098[7:4] LOL_FST_CLR_THR_SEL 6 0x6

796 * 0x009A[1] LOL_SLOW_EN_PLL 1 0x1

797 * 0x009B[7:4] LOL_SLW_DETWIN_SEL 4 0x4

798 * 0x009D[3:2] LOL_SLW_VALWIN_SEL 0 0x0

799 * 0x009E[7:4] LOL_SLW_SET_THR 4 0x4

800 * 0x00A0[7:4] LOL_SLW_CLR_THR 2 0x2

801 * 0x00A2[1] LOL_TIMER_EN 0 0x0

802 * 0x00A9[28:0] LOL_CLR_DELAY_DIV256 49536 0x0000C180

803 * 0x00E5[5] FASTLOCK_EXTEND_EN 1 0x1

804 * 0x00EA[28:0] FASTLOCK_EXTEND 49173 0x0000C015

805 * 0x0102[0] OUTALL_DISABLE_LOW 1 0x1

806 * 0x0112[0] OUT0_PDN 0 0x0

807 * 0x0112[1] OUT0_OE 1 0x1

808 * 0x0112[2] OUT0_RDIV_FORCE2 1 0x1

809 * 0x0113[2:0] OUT0_FORMAT 1 0x1

810 * 0x0113[3] OUT0_SYNC_EN 1 0x1

811 * 0x0113[5:4] OUT0_DIS_STATE 0 0x0

812 * 0x0113[7:6] OUT0_CMOS_DRV 0 0x0

813 * 0x0114[3:0] OUT0_CM 14 0xE

814 * 0x0114[6:4] OUT0_AMPL 3 0x3

815 * 0x0115[2:0] OUT0_MUX_SEL 0 0x0

816 * 0x0115[5:4] OUT0_VDD_SEL 1 0x1

817 * 0x0115[3] OUT0_VDD_SEL_EN 1 0x1

818 * 0x0115[7:6] OUT0_INV 0 0x0

819 * 0x0117[0] OUT1_PDN 0 0x0

820 * 0x0117[1] OUT1_OE 1 0x1

821 * 0x0117[2] OUT1_RDIV_FORCE2 1 0x1

822 * 0x0118[2:0] OUT1_FORMAT 1 0x1

823 * 0x0118[3] OUT1_SYNC_EN 1 0x1

824 * 0x0118[5:4] OUT1_DIS_STATE 0 0x0

825 * 0x0118[7:6] OUT1_CMOS_DRV 0 0x0

826 * 0x0119[3:0] OUT1_CM 14 0xE

827 * 0x0119[6:4] OUT1_AMPL 3 0x3

828 * 0x011A[2:0] OUT1_MUX_SEL 0 0x0

829 * 0x011A[5:4] OUT1_VDD_SEL 1 0x1

830 * 0x011A[3] OUT1_VDD_SEL_EN 1 0x1

831 * 0x011A[7:6] OUT1_INV 0 0x0

832 * 0x0126[0] OUT2_PDN 0 0x0

833 * 0x0126[1] OUT2_OE 1 0x1

834 * 0x0126[2] OUT2_RDIV_FORCE2 1 0x1

835 * 0x0127[2:0] OUT2_FORMAT 1 0x1

836 * 0x0127[3] OUT2_SYNC_EN 1 0x1

837 * 0x0127[5:4] OUT2_DIS_STATE 0 0x0

838 * 0x0127[7:6] OUT2_CMOS_DRV 0 0x0

839 * 0x0128[3:0] OUT2_CM 14 0xE

840 * 0x0128[6:4] OUT2_AMPL 3 0x3

841 * 0x0129[2:0] OUT2_MUX_SEL 0 0x0

842 * 0x0129[5:4] OUT2_VDD_SEL 1 0x1

843 * 0x0129[3] OUT2_VDD_SEL_EN 1 0x1

844 * 0x0129[7:6] OUT2_INV 0 0x0

845 * 0x012B[0] OUT3_PDN 1 0x1

846 * 0x012B[1] OUT3_OE 0 0x0

847 * 0x012B[2] OUT3_RDIV_FORCE2 0 0x0

848 * 0x012C[2:0] OUT3_FORMAT 1 0x1

849 * 0x012C[3] OUT3_SYNC_EN 1 0x1

850 * 0x012C[5:4] OUT3_DIS_STATE 0 0x0

851 * 0x012C[7:6] OUT3_CMOS_DRV 0 0x0

852 * 0x012D[3:0] OUT3_CM 11 0xB

853 * 0x012D[6:4] OUT3_AMPL 3 0x3

854 * 0x012E[2:0] OUT3_MUX_SEL 0 0x0

855 * 0x012E[5:4] OUT3_VDD_SEL 2 0x2

856 * 0x012E[3] OUT3_VDD_SEL_EN 1 0x1

857 * 0x012E[7:6] OUT3_INV 0 0x0

858 * 0x013F[11:0] OUTX_ALWAYS_ON 0 0x000

859 * 0x0141[1] OUT_DIS_MSK 0 0x0

860 * 0x0141[5] OUT_DIS_LOL_MSK 0 0x0

861 * 0x0141[6] OUT_DIS_LOSXAXB_MSK 1 0x1

862 * 0x0141[7] OUT_DIS_MSK_LOS_PFD 0 0x0

863 * 0x0142[1] OUT_DIS_MSK_LOL 1 0x1

864 * 0x0142[5] OUT_DIS_MSK_HOLD 1 0x1

865 * 0x0206[1:0] PXAXB 0 0x0

866 * 0x0208[47:0] P0_NUM 13 0x00000000000D

867 * 0x020E[31:0] P0_DEN 1 0x00000001

868 * 0x0212[47:0] P1_NUM 13 0x00000000000D

869 * 0x0218[31:0] P1_DEN 1 0x00000001

870 * 0x021C[47:0] P2_NUM 0 0x000000000000

871 * 0x0222[31:0] P2_DEN 0 0x00000000

872 * 0x0226[47:0] P3_NUM 0 0x000000000000

873 * 0x022C[31:0] P3_DEN 0 0x00000000

874 * 0x0231[3:0] P0_FRACN_MODE 11 0xB

875 * 0x0231[4] P0_FRACN_EN 0 0x0

876 * 0x0232[3:0] P1_FRACN_MODE 11 0xB

877 * 0x0232[4] P1_FRACN_EN 0 0x0

878 * 0x0233[3:0] P2_FRACN_MODE 11 0xB

879 * 0x0233[4] P2_FRACN_EN 0 0x0

880 * 0x0234[3:0] P3_FRACN_MODE 11 0xB

881 * 0x0234[4] P3_FRACN_EN 0 0x0

882 * 0x0235[43:0] MXAXB_NUM 618817126400 0x09014600000

883 * 0x023B[31:0] MXAXB_DEN 2415919104 0x90000000

884 * 0x0250[23:0] R0_REG 0 0x000000

885 * 0x0253[23:0] R1_REG 0 0x000000

886 * 0x025C[23:0] R2_REG 0 0x000000

887 * 0x025F[23:0] R3_REG 0 0x000000

888 * 0x026B[7:0] DESIGN_ID0 0 0x00

889 * 0x026C[7:0] DESIGN_ID1 0 0x00

890 * 0x026D[7:0] DESIGN_ID2 0 0x00

891 * 0x026E[7:0] DESIGN_ID3 0 0x00

892 * 0x026F[7:0] DESIGN_ID4 0 0x00

893 * 0x0270[7:0] DESIGN_ID5 0 0x00

894 * 0x0271[7:0] DESIGN_ID6 0 0x00

895 * 0x0272[7:0] DESIGN_ID7 0 0x00

896 * 0x028A[4:0] OOF0_TRG_THR_EXT 0 0x00

897 * 0x028B[4:0] OOF1_TRG_THR_EXT 0 0x00

898 * 0x028C[4:0] OOF2_TRG_THR_EXT 0 0x00

899 * 0x028D[4:0] OOF3_TRG_THR_EXT 0 0x00

900 * 0x028E[4:0] OOF0_CLR_THR_EXT 0 0x00

901 * 0x028F[4:0] OOF1_CLR_THR_EXT 0 0x00

902 * 0x0290[4:0] OOF2_CLR_THR_EXT 0 0x00

903 * 0x0291[4:0] OOF3_CLR_THR_EXT 0 0x00

904 * 0x0294[7:4] FASTLOCK_EXTEND_SCL 10 0xA

905 * 0x0296[1] LOL_SLW_VALWIN_SELX 0 0x0

906 * 0x0297[1] FASTLOCK_DLY_ONSW_EN 1 0x1

907 * 0x0299[1] FASTLOCK_DLY_ONLOL_EN 1 0x1

908 * 0x029D[19:0] FASTLOCK_DLY_ONLOL 1802 0x0070A

909 * 0x02A9[19:0] FASTLOCK_DLY_ONSW 2457 0x00999

910 * 0x02B7[3:2] LOL_NOSIG_TIME 3 0x3

911 * 0x0302[43:0] N0_NUM 72007811072 0x010C4000000

912 * 0x0308[31:0] N0_DEN 3355443200 0xC8000000

913 * 0x030C[0] N0_UPDATE 0 0x0

914 * 0x030D[43:0] N1_NUM 0 0x00000000000

915 * 0x0313[31:0] N1_DEN 0 0x00000000

916 * 0x0317[0] N1_UPDATE 0 0x0

917 * 0x0318[43:0] N2_NUM 0 0x00000000000

918 * 0x031E[31:0] N2_DEN 0 0x00000000

919 * 0x0322[0] N2_UPDATE 0 0x0

920 * 0x0323[43:0] N3_NUM 0 0x00000000000

921 * 0x0329[31:0] N3_DEN 0 0x00000000

922 * 0x032D[0] N3_UPDATE 0 0x0

923 * 0x0338[1] N_UPDATE 0 0x0

924 * 0x0339[4:0] N_FSTEP_MSK 30 0x1E

925 * 0x033B[43:0] N0_FSTEPW 7201 0x00000001C21

926 * 0x0341[43:0] N1_FSTEPW 0 0x00000000000

927 * 0x0347[43:0] N2_FSTEPW 0 0x00000000000

928 * 0x034D[43:0] N3_FSTEPW 0 0x00000000000

929 * 0x0359[15:0] N0_DELAY 0 0x0000

930 * 0x035B[15:0] N1_DELAY 0 0x0000

931 * 0x035D[15:0] N2_DELAY 0 0x0000

932 * 0x035F[15:0] N3_DELAY 0 0x0000

933 * 0x0487[0] ZDM_EN 0 0x0

934 * 0x0487[2:1] ZDM_IN_SEL 0 0x0

935 * 0x0487[4] ZDM_AUTOSW_EN 0 0x0

936 * 0x0508[5:0] BW0_PLL 20 0x14

937 * 0x0509[5:0] BW1_PLL 35 0x23

938 * 0x050A[5:0] BW2_PLL 12 0x0C

939 * 0x050B[5:0] BW3_PLL 11 0x0B

940 * 0x050C[5:0] BW4_PLL 3 0x03

941 * 0x050D[5:0] BW5_PLL 63 0x3F

942 * 0x050E[5:0] FASTLOCK_BW0_PLL 22 0x16

943 * 0x050F[5:0] FASTLOCK_BW1_PLL 41 0x29

944 * 0x0510[5:0] FASTLOCK_BW2_PLL 10 0x0A

945 * 0x0511[5:0] FASTLOCK_BW3_PLL 9 0x09

946 * 0x0512[5:0] FASTLOCK_BW4_PLL 3 0x03

947 * 0x0513[5:0] FASTLOCK_BW5_PLL 63 0x3F

948 * 0x0515[55:0] M_NUM 3861418868736 0x0003830E800000

949 * 0x051C[31:0] M_DEN 2684354560 0xA0000000

950 * 0x0521[3:0] M_FRAC_MODE 11 0xB

951 * 0x0521[4] M_FRAC_EN 1 0x1

952 * 0x0521[5] PLL_OUT_RATE_SEL 1 0x1

953 * 0x052A[0] IN_SEL_REGCTRL 1 0x1

954 * 0x052A[3:1] IN_SEL 0 0x0

955 * 0x052B[0] FASTLOCK_AUTO_EN 1 0x1

956 * 0x052B[1] FASTLOCK_MAN 0 0x0

957 * 0x052C[0] HOLD_EN 1 0x1

958 * 0x052C[3] HOLD_RAMP_BYP 0 0x0

959 * 0x052C[4] HOLDEXIT_BW_SEL1 0 0x0

960 * 0x052C[7:5] RAMP_STEP_INTERVAL 4 0x4

961 * 0x052D[1] HOLD_RAMPBYP_NOHIST 1 0x1

962 * 0x052E[4:0] HOLD_HIST_LEN 25 0x19

963 * 0x052F[4:0] HOLD_HIST_DELAY 25 0x19

964 * 0x0531[4:0] HOLD_REF_COUNT_FRC 0 0x00

965 * 0x0532[23:0] HOLD_15M_CYC_COUNT 867 0x000363

966 * 0x0535[0] FORCE_HOLD 0 0x0

967 * 0x0536[1:0] CLK_SWITCH_MODE 0 0x0

968 * 0x0536[2] HSW_EN 1 0x1

969 * 0x0537[3:0] IN_LOS_MSK 0 0x0

970 * 0x0537[7:4] IN_OOF_MSK 0 0x0

971 * 0x0538[2:0] IN0_PRIORITY 0 0x0

972 * 0x0538[6:4] IN1_PRIORITY 0 0x0

973 * 0x0539[2:0] IN2_PRIORITY 0 0x0

974 * 0x0539[6:4] IN3_PRIORITY 0 0x0

975 * 0x053A[1:0] HSW_MODE 2 0x2

976 * 0x053A[3:2] HSW_PHMEAS_CTRL 0 0x0

977 * 0x053B[9:0] HSW_PHMEAS_THR 3 0x003

978 * 0x053D[4:0] HSW_COARSE_PM_LEN 17 0x11

979 * 0x053E[4:0] HSW_COARSE_PM_DLY 6 0x06

980 * 0x0589[12:0] PFD_EN_DELAY 13 0x000D

981 * 0x059B[1] INIT_LP_CLOSE_HO 1 0x1

982 * 0x059B[4] HOLD_PRESERVE_HIST 1 0x1

983 * 0x059B[5] HOLD_FRZ_WITH_INTONLY 1 0x1

984 * 0x059B[6] HOLDEXIT_BW_SEL0 1 0x1

985 * 0x059B[7] HOLDEXIT_STD_BO 1 0x1

986 * 0x059D[5:0] HOLDEXIT_BW0 20 0x14

987 * 0x059E[5:0] HOLDEXIT_BW1 37 0x25

988 * 0x059F[5:0] HOLDEXIT_BW2 12 0x0C

989 * 0x05A0[5:0] HOLDEXIT_BW3 11 0x0B

990 * 0x05A1[5:0] HOLDEXIT_BW4 3 0x03

991 * 0x05A2[5:0] HOLDEXIT_BW5 63 0x3F

992 * 0x05A6[2:0] RAMP_STEP_SIZE 3 0x3

993 * 0x05A6[3] RAMP_SWITCH_EN 1 0x1

994 * 0x0802[15:0] FIXREGSA0 1333 0x0535

995 * 0x0804[7:0] FIXREGSD0 0 0x00

996 * 0x0805[15:0] FIXREGSA1 0 0x0000

997 * 0x0807[7:0] FIXREGSD1 0 0x00

998 * 0x0808[15:0] FIXREGSA2 0 0x0000

999 * 0x080A[7:0] FIXREGSD2 0 0x00

1000 * 0x080B[15:0] FIXREGSA3 0 0x0000

1001 * 0x080D[7:0] FIXREGSD3 0 0x00

1002 * 0x080E[15:0] FIXREGSA4 0 0x0000

1003 * 0x0810[7:0] FIXREGSD4 0 0x00

1004 * 0x0811[15:0] FIXREGSA5 0 0x0000

1005 * 0x0813[7:0] FIXREGSD5 0 0x00

1006 * 0x0814[15:0] FIXREGSA6 0 0x0000

1007 * 0x0816[7:0] FIXREGSD6 0 0x00

1008 * 0x0817[15:0] FIXREGSA7 0 0x0000

1009 * 0x0819[7:0] FIXREGSD7 0 0x00

1010 * 0x081A[15:0] FIXREGSA8 0 0x0000

1011 * 0x081C[7:0] FIXREGSD8 0 0x00

1012 * 0x081D[15:0] FIXREGSA9 0 0x0000

1013 * 0x081F[7:0] FIXREGSD9 0 0x00

1014 * 0x0820[15:0] FIXREGSA10 0 0x0000

1015 * 0x0822[7:0] FIXREGSD10 0 0x00

1016 * 0x0823[15:0] FIXREGSA11 0 0x0000

1017 * 0x0825[7:0] FIXREGSD11 0 0x00

1018 * 0x0826[15:0] FIXREGSA12 0 0x0000

1019 * 0x0828[7:0] FIXREGSD12 0 0x00

1020 * 0x0829[15:0] FIXREGSA13 0 0x0000

1021 * 0x082B[7:0] FIXREGSD13 0 0x00

1022 * 0x082C[15:0] FIXREGSA14 0 0x0000

1023 * 0x082E[7:0] FIXREGSD14 0 0x00

1024 * 0x082F[15:0] FIXREGSA15 0 0x0000

1025 * 0x0831[7:0] FIXREGSD15 0 0x00

1026 * 0x0832[15:0] FIXREGSA16 0 0x0000

1027 * 0x0834[7:0] FIXREGSD16 0 0x00

1028 * 0x0835[15:0] FIXREGSA17 0 0x0000

1029 * 0x0837[7:0] FIXREGSD17 0 0x00

1030 * 0x0838[15:0] FIXREGSA18 0 0x0000

1031 * 0x083A[7:0] FIXREGSD18 0 0x00

1032 * 0x083B[15:0] FIXREGSA19 0 0x0000

1033 * 0x083D[7:0] FIXREGSD19 0 0x00

1034 * 0x083E[15:0] FIXREGSA20 0 0x0000

1035 * 0x0840[7:0] FIXREGSD20 0 0x00

1036 * 0x0841[15:0] FIXREGSA21 0 0x0000

1037 * 0x0843[7:0] FIXREGSD21 0 0x00

1038 * 0x0844[15:0] FIXREGSA22 0 0x0000

1039 * 0x0846[7:0] FIXREGSD22 0 0x00

1040 * 0x0847[15:0] FIXREGSA23 0 0x0000

1041 * 0x0849[7:0] FIXREGSD23 0 0x00

1042 * 0x084A[15:0] FIXREGSA24 0 0x0000

1043 * 0x084C[7:0] FIXREGSD24 0 0x00

1044 * 0x084D[15:0] FIXREGSA25 0 0x0000

1045 * 0x084F[7:0] FIXREGSD25 0 0x00

1046 * 0x0850[15:0] FIXREGSA26 0 0x0000

1047 * 0x0852[7:0] FIXREGSD26 0 0x00

1048 * 0x0853[15:0] FIXREGSA27 0 0x0000

1049 * 0x0855[7:0] FIXREGSD27 0 0x00

1050 * 0x0856[15:0] FIXREGSA28 0 0x0000

1051 * 0x0858[7:0] FIXREGSD28 0 0x00

1052 * 0x0859[15:0] FIXREGSA29 0 0x0000

1053 * 0x085B[7:0] FIXREGSD29 0 0x00

1054 * 0x085C[15:0] FIXREGSA30 0 0x0000

1055 * 0x085E[7:0] FIXREGSD30 0 0x00

1056 * 0x085F[15:0] FIXREGSA31 0 0x0000

1057 * 0x0861[7:0] FIXREGSD31 0 0x00

1058 * 0x090E[0] XAXB_EXTCLK_EN 0 0x0

1059 * 0x0943[0] IO_VDD_SEL 0 0x0

1060 * 0x0949[3:0] IN_EN 3 0x3

1061 * 0x0949[7:4] IN_PULSED_CMOS_EN 0 0x0

1062 * 0x094A[3:0] INX_TO_PFD_EN 3 0x3

1063 * 0x094E[11:0] REFCLK_HYS_SEL 585 0x249

1064 * 0x095E[0] MXAXB_INTEGER 0 0x0

1065 * 0x0A02[4:0] N_ADD_0P5 0 0x00

1066 * 0x0A03[4:0] N_CLK_TO_OUTX_EN 1 0x01

1067 * 0x0A04[4:0] N_PIBYP 0 0x00

1068 * 0x0A05[4:0] N_PDNB 1 0x01

1069 * 0x0A14[3] N0_HIGH_FREQ 0 0x0

1070 * 0x0A1A[3] N1_HIGH_FREQ 0 0x0

1071 * 0x0A20[3] N2_HIGH_FREQ 0 0x0

1072 * 0x0A26[3] N3_HIGH_FREQ 0 0x0

1073 * 0x0B44[3:0] PDIV_FRACN_CLK_DIS 15 0xF

1074 * 0x0B44[5] FRACN_CLK_DIS_PLL 0 0x0

1075 * 0x0B46[3:0] LOS_CLK_DIS 0 0x0

1076 * 0x0B47[4:0] OOF_CLK_DIS 12 0x0C

1077 * 0x0B48[4:0] OOF_DIV_CLK_DIS 12 0x0C

1078 * 0x0B4A[4:0] N_CLK_DIS 14 0x0E

1079 * 0x0B57[11:0] VCO_RESET_CALCODE 240 0x0F0

1080 *

1081 *

1082 */

1083

1084 #endif

You might also like

- FpartsDocument3 pagesFpartsCastillo HectorNo ratings yet

- Sampel Data SondirDocument4 pagesSampel Data SondirKalsel 1.1No ratings yet

- SSD ReportDocument7 pagesSSD ReportbadiuNo ratings yet

- FpartsDocument3 pagesFpartsEdgar CaleroNo ratings yet

- FpartsDocument5 pagesFpartsHiago RochaNo ratings yet

- CodeDocument7 pagesCodeMak MédiNo ratings yet

- FpartsDocument3 pagesFpartsJulio Cesar GonzalezNo ratings yet

- Get GoldDocument10 pagesGet Gold0013122819No ratings yet

- Native Alien 48Document2 pagesNative Alien 48Siewski Wojtek KarwackiNo ratings yet

- EliteCryptoHex DemoVersionDocument6 pagesEliteCryptoHex DemoVersionandrianpc8No ratings yet

- Reporte de SSDDocument7 pagesReporte de SSDDaniel Vasquez CuevasNo ratings yet

- FpartsDocument5 pagesFpartsozzyNo ratings yet

- TABELAS Testes de Hipotese PDFDocument3 pagesTABELAS Testes de Hipotese PDFMarcos Moulin da PaschoaNo ratings yet

- Assignment 2 WK 6to7Document6 pagesAssignment 2 WK 6to7Peng GuinNo ratings yet

- 20bce2251 VL2021220503859 Ast04Document8 pages20bce2251 VL2021220503859 Ast04TANMAY MEHROTRANo ratings yet

- Tabela Z Normal Padrão: Observação: Valores Gerados No MS Excel (Função DIST. NORMP) Por Alex GamaDocument2 pagesTabela Z Normal Padrão: Observação: Valores Gerados No MS Excel (Função DIST. NORMP) Por Alex GamaalexgamaqsNo ratings yet

- Speednews6 20 2006Document4 pagesSpeednews6 20 2006speednewsNo ratings yet

- Abjad A-ZDocument4 pagesAbjad A-ZZulkarnainNo ratings yet

- Nessahan - Alita - Obra Completa (2008) PDFDocument825 pagesNessahan - Alita - Obra Completa (2008) PDFcgc2No ratings yet

- PXL PSHR Winning Animation SettingsDocument4 pagesPXL PSHR Winning Animation Settingshello indonesiaNo ratings yet

- Assignment5 VidulGargDocument12 pagesAssignment5 VidulGargvidulgarg1524No ratings yet

- Include Include Include: "Aes.h"Document15 pagesInclude Include Include: "Aes.h"Sanjay SahaiNo ratings yet

- Game CrashDocument5 pagesGame CrashCandra Pungki WibowoNo ratings yet

- Design of Headed Concrete Anchor - 10 10 07Document36 pagesDesign of Headed Concrete Anchor - 10 10 07ALWIN ROJER BINNI VNo ratings yet

- Throath Thickness Table For Forged Outlet Fitting: T + (T 0.7) or Min .6.4 Where, TDocument1 pageThroath Thickness Table For Forged Outlet Fitting: T + (T 0.7) or Min .6.4 Where, TКонстантин ДёминовNo ratings yet

- Tabel PintuDocument1 pageTabel PintuIndri Suryani LubisNo ratings yet

- Anshika SlipsDocument173 pagesAnshika SlipsAbhishek MishraNo ratings yet

- Data Sementara - Sondir Preservasi Jl. Handil Bakti - KM.17Document16 pagesData Sementara - Sondir Preservasi Jl. Handil Bakti - KM.17kertaningNo ratings yet

- RRC 2Document4 pagesRRC 2burdun777No ratings yet

- Tabela - Momentos Fletores, Regime Rígido Plástico PDFDocument2 pagesTabela - Momentos Fletores, Regime Rígido Plástico PDFMauricio Henrique da SilvaNo ratings yet

- UntitledDocument9 pagesUntitledJaqueline DemosNo ratings yet

- Poligonal CerradaDocument11 pagesPoligonal Cerradajesus varelaNo ratings yet

- Tabla de La Distribución Binomial: Página 1Document20 pagesTabla de La Distribución Binomial: Página 1Lidia ReséndizNo ratings yet

- Tabla Binomial PDFDocument20 pagesTabla Binomial PDFrocio pinedoNo ratings yet

- Tabela de BraresDocument1 pageTabela de BraresGETULIO VICENTE VIEIRA MENEZESNo ratings yet

- 7 CPC Pay MatrixDocument1 page7 CPC Pay Matrixramana adepuNo ratings yet

- Safe Gard Performance 2017Document2 pagesSafe Gard Performance 2017LNo ratings yet

- Tabela - Relatório 03Document2 pagesTabela - Relatório 03xxxpeedroxxxNo ratings yet

- Solucion de Problemas de Centros de Gravedad Y Momentos de Inercia de Figuras PlanasDocument1 pageSolucion de Problemas de Centros de Gravedad Y Momentos de Inercia de Figuras Planasvictor mamaniNo ratings yet

- Message 2Document180 pagesMessage 2peroperomatNo ratings yet

- Nhu N Ky Mik/ K ) XKSJ (Kiqj Fo"ofo - Ky ) XKSJ (Kiqj: Izos"k Ijh (KK Ifj - Kke &2013Document34 pagesNhu N Ky Mik/ K ) XKSJ (Kiqj Fo"ofo - Ky ) XKSJ (Kiqj: Izos"k Ijh (KK Ifj - Kke &2013Mukesh BishtNo ratings yet

- Salary ScheduleDocument48 pagesSalary ScheduleEric Soliva SorianoNo ratings yet

- Crash 1156Document8 pagesCrash 1156Максим Сидоренко0% (1)

- Hex ResolutionsDocument5 pagesHex Resolutions"Forced" Unlimited Downloads0% (1)

- AesDocument18 pagesAessüleyman_kabadayıNo ratings yet

- Discount Factor Nilai SekarangDocument10 pagesDiscount Factor Nilai SekarangHendra PerdanaNo ratings yet

- 2307Document2 pages2307Vladan PrigaraNo ratings yet

- 2009-05-16 23.53.12 ErrorDocument9 pages2009-05-16 23.53.12 ErrorFanny FirdausNo ratings yet

- UE3 Auto Report Ini Dump 0001Document374 pagesUE3 Auto Report Ini Dump 0001Grant DePoyNo ratings yet

- Perencanaan Bangunan Gedung X Lokasi: Kota PontianakDocument6 pagesPerencanaan Bangunan Gedung X Lokasi: Kota PontianakRiski InyikNo ratings yet

- Tablice StataDocument13 pagesTablice StataJan MajchrzakNo ratings yet

- Handbook VVKR-A-S 202201Document38 pagesHandbook VVKR-A-S 202201mohamed roubioNo ratings yet

- Chapter 1Document13 pagesChapter 1narasimha100% (2)

- Code Du Travail Utilisation Des MachineDocument9 pagesCode Du Travail Utilisation Des MachineredaNo ratings yet

- Crash LogDocument128 pagesCrash LogiBlogNo ratings yet

- Weld CheckDocument14 pagesWeld CheckmaheshbandhamNo ratings yet

- SSAW PipeDocument15 pagesSSAW PipeAissamNo ratings yet

- TP Debug InfoDocument2,828 pagesTP Debug InfoBorjinov GGNo ratings yet

- Direct Fixation TrackDocument323 pagesDirect Fixation TrackAddiahDr Kofi100% (1)

- 20-21 AS Prelim MsDocument27 pages20-21 AS Prelim Mskathleen hoNo ratings yet

- Electrical Experimenter191712Document84 pagesElectrical Experimenter191712spaske_No ratings yet

- Stockhausen Karlheinz 1972 1989 Four Criteria of Electronic MusicDocument12 pagesStockhausen Karlheinz 1972 1989 Four Criteria of Electronic MusicMax Lange100% (1)

- Hero CollectionDocument33 pagesHero CollectionitounosNo ratings yet

- Eventide Modfactor Factory PresetsDocument3 pagesEventide Modfactor Factory PresetsSrdjan StefanovNo ratings yet

- Problem Set Waves and Wave PropertiesDocument2 pagesProblem Set Waves and Wave PropertiesYohana Glorya TobingNo ratings yet

- JEE Main 2021 Feb 24 Second Shift Question PaperDocument18 pagesJEE Main 2021 Feb 24 Second Shift Question PaperDishant ShahNo ratings yet

- 1729 Enmed310009enDocument4 pages1729 Enmed310009ensurda123No ratings yet

- Student Book Answers - Physics 1 Chapter 2Document5 pagesStudent Book Answers - Physics 1 Chapter 2Mhmd AlrashedNo ratings yet

- Time and Texture in Lutoslawski's Concerto For Orchestra and Ligeti's Chamber Concerto'Document37 pagesTime and Texture in Lutoslawski's Concerto For Orchestra and Ligeti's Chamber Concerto'andrewcosta100% (2)

- Solutions HW 5Document5 pagesSolutions HW 5Abcd EfghNo ratings yet

- Wave Properties v2.0Document28 pagesWave Properties v2.0h a100% (1)

- Physical Sciences Grade 12 Term 2 1Document120 pagesPhysical Sciences Grade 12 Term 2 1Linda Mnisi100% (1)

- bp189413 PDFDocument6 pagesbp189413 PDFBazavan ConstantinNo ratings yet

- D4123Document4 pagesD4123FranklinNo ratings yet

- ECSS-ST-10-03C Draft12.5 4march2011Document41 pagesECSS-ST-10-03C Draft12.5 4march2011anilguptame88100% (1)

- Police Patrol Operation Par. 5Document20 pagesPolice Patrol Operation Par. 5johnpaulacostaNo ratings yet

- Physics Handouts HandoutsDocument7 pagesPhysics Handouts HandoutsLeanne Macayan SantosNo ratings yet

- Zealous Brick Making Machine Main Model Parameters PDFDocument13 pagesZealous Brick Making Machine Main Model Parameters PDFdajl100% (1)

- 4.5 Standing WavesDocument2 pages4.5 Standing WavespixelhoboNo ratings yet

- En 12697-242004 (E)Document8 pagesEn 12697-242004 (E)tantai2004No ratings yet

- GU3303 GU3304Genset Controller Operation ManualDocument44 pagesGU3303 GU3304Genset Controller Operation ManualArc Hie100% (4)

- Statistical Multipath Model Lecture4 PDFDocument16 pagesStatistical Multipath Model Lecture4 PDFkivetiNo ratings yet

- Acuson X700 Ultrasound System: Quick Reference Guide - General Imaging System OverviewDocument32 pagesAcuson X700 Ultrasound System: Quick Reference Guide - General Imaging System OverviewPopescu ValiNo ratings yet

- Electronic Distance Measurement (EDM)Document29 pagesElectronic Distance Measurement (EDM)Kavi MaranNo ratings yet

- Half Car Simulink ModelDocument35 pagesHalf Car Simulink ModelFunkysajan83% (6)

- Digital Waveform Encoding Based On Click Character Op-Codes: AbstractDocument33 pagesDigital Waveform Encoding Based On Click Character Op-Codes: AbstractssfofoNo ratings yet

- Project Report On Electromagnetic WavesDocument10 pagesProject Report On Electromagnetic WavesMadhuj Singhal80% (5)

- As and A Level Physics Core Practical 6 SpeeDocument5 pagesAs and A Level Physics Core Practical 6 SpeeHady JawadNo ratings yet

- Computer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)From EverandComputer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)Rating: 4 out of 5 stars4/5 (4)

- FTTx Networks: Technology Implementation and OperationFrom EverandFTTx Networks: Technology Implementation and OperationRating: 5 out of 5 stars5/5 (1)

- AWS Certified Solutions Architect Study Guide: Associate SAA-C01 ExamFrom EverandAWS Certified Solutions Architect Study Guide: Associate SAA-C01 ExamRating: 4 out of 5 stars4/5 (1)

- ITIL® 4 Create, Deliver and Support (CDS): Your companion to the ITIL 4 Managing Professional CDS certificationFrom EverandITIL® 4 Create, Deliver and Support (CDS): Your companion to the ITIL 4 Managing Professional CDS certificationRating: 5 out of 5 stars5/5 (2)

- Cybersecurity: The Beginner's Guide: A comprehensive guide to getting started in cybersecurityFrom EverandCybersecurity: The Beginner's Guide: A comprehensive guide to getting started in cybersecurityRating: 5 out of 5 stars5/5 (2)

- The Compete Ccna 200-301 Study Guide: Network Engineering EditionFrom EverandThe Compete Ccna 200-301 Study Guide: Network Engineering EditionRating: 5 out of 5 stars5/5 (4)

- Evaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsFrom EverandEvaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsRating: 5 out of 5 stars5/5 (1)

- ITIL® 4 Drive Stakeholder Value (DSV): Your companion to the ITIL 4 Managing Professional DSV certificationFrom EverandITIL® 4 Drive Stakeholder Value (DSV): Your companion to the ITIL 4 Managing Professional DSV certificationNo ratings yet

- Microsoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsFrom EverandMicrosoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsNo ratings yet

- AWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamFrom EverandAWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamNo ratings yet

- Cybersecurity: A Simple Beginner’s Guide to Cybersecurity, Computer Networks and Protecting Oneself from Hacking in the Form of Phishing, Malware, Ransomware, and Social EngineeringFrom EverandCybersecurity: A Simple Beginner’s Guide to Cybersecurity, Computer Networks and Protecting Oneself from Hacking in the Form of Phishing, Malware, Ransomware, and Social EngineeringRating: 5 out of 5 stars5/5 (40)

- Open Radio Access Network (O-RAN) Systems Architecture and DesignFrom EverandOpen Radio Access Network (O-RAN) Systems Architecture and DesignNo ratings yet

- The Windows Command Line Beginner's Guide: Second EditionFrom EverandThe Windows Command Line Beginner's Guide: Second EditionRating: 4 out of 5 stars4/5 (4)

- Microsoft Certified Azure Fundamentals Study Guide: Exam AZ-900From EverandMicrosoft Certified Azure Fundamentals Study Guide: Exam AZ-900No ratings yet

- Network+ Study Guide & Practice ExamsFrom EverandNetwork+ Study Guide & Practice ExamsRating: 4.5 out of 5 stars4.5/5 (5)

- Hacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.From EverandHacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.Rating: 5 out of 5 stars5/5 (2)

- CWNA Certified Wireless Network Administrator Study Guide: Exam CWNA-108From EverandCWNA Certified Wireless Network Administrator Study Guide: Exam CWNA-108No ratings yet

- Set Up Your Own IPsec VPN, OpenVPN and WireGuard Server: Build Your Own VPNFrom EverandSet Up Your Own IPsec VPN, OpenVPN and WireGuard Server: Build Your Own VPNRating: 5 out of 5 stars5/5 (1)

- Amazon Web Services (AWS) Interview Questions and AnswersFrom EverandAmazon Web Services (AWS) Interview Questions and AnswersRating: 4.5 out of 5 stars4.5/5 (3)

- Hacking: A Beginners Guide To Your First Computer Hack; Learn To Crack A Wireless Network, Basic Security Penetration Made Easy and Step By Step Kali LinuxFrom EverandHacking: A Beginners Guide To Your First Computer Hack; Learn To Crack A Wireless Network, Basic Security Penetration Made Easy and Step By Step Kali LinuxRating: 4.5 out of 5 stars4.5/5 (67)

- Computer Networking: The Complete Guide to Understanding Wireless Technology, Network Security, Computer Architecture and Communications Systems (Including Cisco, CCNA and CCENT)From EverandComputer Networking: The Complete Guide to Understanding Wireless Technology, Network Security, Computer Architecture and Communications Systems (Including Cisco, CCNA and CCENT)No ratings yet

- ITIL 4 : Drive Stakeholder Value: Reference and study guideFrom EverandITIL 4 : Drive Stakeholder Value: Reference and study guideNo ratings yet

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideFrom EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideRating: 1 out of 5 stars1/5 (1)