Professional Documents

Culture Documents

Low-Power High-Speed Full Adder For Portable Electronic Applications

Uploaded by

Arvind ChakrapaniOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Low-Power High-Speed Full Adder For Portable Electronic Applications

Uploaded by

Arvind ChakrapaniCopyright:

Available Formats

Low-power high-speed full adder for to a strong-one (Vdd) accordingly.

In this way, the output of the

portable electronic applications NMOS multiplexer is reshaped with an improved output driving

capability.

C.-K. Tung, S.-H. Shieh and C.-H. Cheng

B

A low-power, high-speed full adder (FA), abbreviated as LPHS-FA, is

presented as an elegant way to reduce circuit complexity and improve

the performance thereof. Employing as few as 15 MOSFETs in total, H Co ¢

an LPHS-FA requires 60–73% fewer transistors than other existing

FAs with drivability. For validation purpose, HSPICE simulations Ci

are conducted on all the proposed and referenced FAs based on the

TSMC 0.18-μm CMOS process technology. The LPHS-FA is found H

to provide a 20.4–21.2% power saving, a 12.3–67.0% delay time H¢ Co

reduction and a 35–102% reduction in power delay product compared H¢

with the referenced FAs. In short, an LPHS-FA is presented in a

concise form as a high-performance FA in practical applications.

A A

a b

Introduction: Owing to the rapid growth in portable electronic devices H

with constraint of power, it becomes a critical challenge as well as a

Ci

competitive task to design high performance, small chip area and low

power consumption circuits to enhance product competitiveness for

H¢ So

integrated circuit designers nowadays. The full adder (FA) is regarded

as the most significant and crucial building block in an arithmetic unit

Co¢

of portable devices in today’s highly competitive markets. Therefore it

becomes a hot issue to design a low-power, high-speed FA H

(LPHS-FA) occupying a small chip area. c

As referred to previously, the performance of an arithmetic circuit is

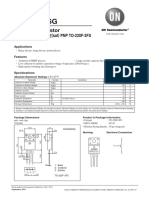

found directly subject to all the FAs employed, stimulating the develop- Fig. 1 Modules in LPHS-FA

ment of a wide variety of FAs for various applications. As suggested in a XOR–XNOR module

[1, 2], a smaller number of transistors are adopted to achieve the aim of b Carry module

c Sum module

chip area reduction, but the accompanying disadvantages are threshold

voltage loss, a low noise margin and a low-output driving capability. In

contrast, a large number of studies have been conducted on features

Ci

elevation [3–6], e.g. low power consumption, high-speed arithmetic

operation, improved output driving capability, full-swing voltage and B So

so forth. Yet, the price paid is that it inevitably requires a greater

number of transistors, a larger chip area and higher circuit complexity. H

A state-of-the-art FA (NEW-HPSC) is designed using a combination

of pass transistor logic (PTL) and static CMOS design techniques to

provide high energy efficiency and improve driving capability [4]. For Co¢

further performance improvement, a hybrid-CMOS FA is proposed in H¢

[5] to achieve better power-delay product (PDP). An energy efficient

CMOS FA is implemented using swing restored complementary Co

A

pass-transistor logic (SR-CPL) and PTL techniques to optimise its

PDP [6].

Thus, this Letter presents a simple structured, high-performance FA

by use of the PTL design technique as an elegant way to advance the Fig. 2 Circuit schematic of proposed LPHS-FA

overall performance of an arithmetic circuit and electronic devices.

In contrast, the sum module, as illustrated in Fig. 1c, is implemented

Circuit design and analysis of proposed LPHS-FA: For performance by a transmission gate (TG)-based multiplier. Both H and H′ are applied

improvement and circuit complexity reduction, Boolean functions of to the multiplexer as the control signals, whereas Ci and C′o are the input

the LPHS-FA are reformulated as signals to perform the logical operation in (1). Taking Ci and C′o as the

input to the multiplexer, the sum module acquires a simple structure

So = H ′ Ci + HCo′ (1) advantage and an improved output driving capability. A good use of

Co = HCi + H A ′

(2) the PTL technique in the circuit design gives rise to a simple configured

and elegant FA.

where H = A ⊕ B and H ′ = A ⊙ B. An LPHS-FA is made up of an Based on the modules depicted in Fig. 1, a simple structured FA with

XOR–XNOR module, a sum module and a carry module. As illustrated reduced complexity and improved performance is designed for a high-

in Fig. 1a, the XOR–XNOR module performs XOR and XNOR logic speed arithmetic circuit. This proposed FA LPHS-FA, as shown in

operations on inputs A and B, and then generates the outputs H and Fig. 2, demonstrates low-power and high-speed advantages, and

H′. Subsequently, H and H′ both are applied to the sum and the carry merely requires 15 MOSFETs to implement.

modules for generation of sum output So and carry output Co.

For the purpose of complexity reduction and output driving capability Results and discussion: For performance validation, simulation com-

enhancement, both the sum and the carry modules are realised with mul- parisons are made among LPHS-FA, NEW-HPSC, hybrid-CMOS and

tiplexers. The carry module, as configured in Fig. 1b, is particularly SR-CPL FAs. All the HSPICE simulations are performed on these

implemented by an NMOS multiplexer. Both H and H′ are applied to FAs based on the TSMC 0.18 μm CMOS process technology. For an

the NMOS multiplexer as the control signals, whereas Ci and A are objective comparison, all the adders are simulated involving identical

the input signals to perform the operation in (2). In the simple structured transistors under the same test conditions.

NMOS multiplexer consisting of two NMOS transistors, the carry signal The FA simulation results at input frequency f = 100 MHz and Vdd =

is propagated in a highly efficient manner, but an accompanying disad- 1.8 V are tabulated in Table 1. It is revealed that an LPHS-FA exhibits a

vantage is the existence of a weak-one signal level, which can be pulled power (Pd) saving of 20.4–21.2%, a delay time (Td) reduction of 12.3–

up to Vdd through an energy storage technique by combination of an 67% and a PDP improvement of 35–102%. An LPHS-FA merely

inverter and a pull-up PMOS transistor. In other words, the weak-one employs 15 MOS transistors, which is 60–73% lower transistor count

signal level at node Co is inverted to ‘0’ at node C′o to enable the than that required in other types of FAs. In this way, a smaller chip

pull-up transistor PMOS, and the signal level at node Co is pulled up area is occupied, leading to a reduced cost for the FA directly. The

ELECTRONICS LETTERS 15th August 2013 Vol. 49 No. 17

LPHS-FA has low power dissipation because of its low transistor count, C.-K. Tung (Ph.D. Program of Electrical and Communications

PTL- and TG-based building blocks and all full-swing nodes structure Engineering, Feng Chia University, Taichung, Taiwan)

without the threshold loss problem. The high-speed feature gained for S.-H. Shieh (Department of Electronic Engineering, National Chin-Yi

the LPHS-FA, thanks to the carry propagation path, has merely one University of Technology, Taichung, Taiwan)

pass transistor delay. Drivability of the LPHS-FA is guaranteed by its

all full-swing nodes structure and positive feedback loop structure at E-mail: ssh@ncut.edu.tw

Co node. In a brief conclusion, a superior performance is demonstrated C.-H. Cheng (Department of Electronic Engineering, Feng Chia

by the LPHS-FA relative to other types of FAs in any case. University, Taichung, Taiwan)

C.-K. Tung: Also with the Department of Electronic Engineering,

Table 1: Simulation results for various FAs with drivability at an National Chin-Yi University of Technology, Taichung, Taiwan

input frequency of 100 MHz

References Transistor count Pd (μW at 1.8 V) Td (ns) PDP (μW × ns) References

[4] 26 6.951 0.299 2.078 1 Bui, H.T., Wang, Y., and Jiang, Y.: ‘Design and analysis of low-power

[5] 24 6.907 0.278 1.920 10-transistor full adders using novel XOR–XNOR gates’, IEEE Trans.

[6] 26 6.910 0.201 1.388 Circuits Syst. II, 2002, 49, (1), pp. 25–30

2 Lin, J.-F., Hwang, Y.-T., Sheu, M.-H., and Ho, C.-C.: ‘A novel high-

This work 15 5.736 0.179 1.026

speed and energy efficient 10-transistor full adder design’, IEEE Trans.

Circuits Syst. I, 2007, 54, (5), pp. 1050–1059

Conclusion: As the core of an arithmetic circuit, that is a key module in 3 Radhakrishnan, D.: ‘Low-voltage low-power CMOS full adder’, IEE

a large number of portable electronic systems, an LPHS-FA is presented Proc., Circuits Devices Syst., 2001, 148, (1), pp. 19–24

in this Letter as a way to simplify the circuit architecture and hence 4 Chang, C.-H., Gu, J., and Zhang, M.: ‘A review of 0.18-um full adder

improve the performance. For performance validation, HSPICE simu- performances for tree structured arithmetic circuits’, IEEE Trans. Very

lations were conducted on FAs implemented with TSMC 0.18 μm Large Scale Integr. (VLSI) Syst., 2005, 13, (6), pp. 686–695

CMOS process technology in aspects of power consumption, delay 5 Goel, S., Kumar, A., and Bayoumi, M.A.: ‘Design of robust,

energy-efficient full adders for deep-submicrometer design using

time and PDP. In contrast to other types of LPFAs with drivability, an

hybrid-CMOS logic style’, IEEE Trans. Very Large Scale Integr.

LPHS-FA is superior to the other ones and can be applied to design (VLSI) Syst., 2006, 14, (12), pp. 1309–1321

related adder-based portable electronic products in practical applications 6 Aguirre-Hernandez, M., and Linares-Aranda, M.: ‘CMOS full-adders for

in today’s competitive markets. energy-efficient arithmetic applications’, IEEE Trans. Very Large Scale

Integr. (VLSI) Syst., 2011, 19, (4), pp. 718–721

© The Institution of Engineering and Technology 2013

16 April 2013

doi: 10.1049/el.2013.0893

ELECTRONICS LETTERS 15th August 2013 Vol. 49 No. 17

You might also like

- Short Circuit CalculationsDocument44 pagesShort Circuit Calculationssasikumar100% (2)

- Solid State Chemistry Practice Papers ComDocument35 pagesSolid State Chemistry Practice Papers Commanutd01100% (1)

- 101 Science EXPERIMENTS WITH PAPERDocument49 pages101 Science EXPERIMENTS WITH PAPERsaisssms9116100% (5)

- Lab 4 – Op Amp Filters Frequency ResponseDocument14 pagesLab 4 – Op Amp Filters Frequency ResponseNataly MedinaNo ratings yet

- AVR AS440 Data SheetDocument4 pagesAVR AS440 Data SheetMazhar Hussain100% (2)

- Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceDocument8 pagesPerformance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceAnonymous kw8Yrp0R5r100% (1)

- Vital - Scientific - Analyzer - Selectra e - Service - Manual PDFDocument225 pagesVital - Scientific - Analyzer - Selectra e - Service - Manual PDFAtul Ramteke100% (1)

- Design of A Scalable Low-Power 1-Bit Hybrid Full Adder For Fast ComputationDocument5 pagesDesign of A Scalable Low-Power 1-Bit Hybrid Full Adder For Fast Computationfakesmilelover07No ratings yet

- ULPFA: A New Efficient Design of A Power-Aware Full AdderDocument9 pagesULPFA: A New Efficient Design of A Power-Aware Full AdderDeepak RajeshNo ratings yet

- The Recycling Folded Cascode A General Enhancement of The Folded Cascode AmplifierDocument8 pagesThe Recycling Folded Cascode A General Enhancement of The Folded Cascode AmplifierAyanabho BanerjeeNo ratings yet

- Design of Robust, Energy-Efficient Full Adders For Deep-Submicrometer Design Using Hybrid-CMOS Logic StyleDocument22 pagesDesign of Robust, Energy-Efficient Full Adders For Deep-Submicrometer Design Using Hybrid-CMOS Logic StyleSachinNo ratings yet

- A 30-Ghz Power-Efficient PLL Frequency Synthesizer For 60-Ghz ApplicationsDocument11 pagesA 30-Ghz Power-Efficient PLL Frequency Synthesizer For 60-Ghz Applicationsmohan sardarNo ratings yet

- Low-Power Hybrid 1-bit Full Adder for Fast ComputationDocument5 pagesLow-Power Hybrid 1-bit Full Adder for Fast ComputationBhaumik ChavdaNo ratings yet

- The Recycling Folded CascodeDocument8 pagesThe Recycling Folded CascodeFelipe BertonNo ratings yet

- Rajagopal 2021Document4 pagesRajagopal 2021Vani YamaniNo ratings yet

- Bandwidth Extension in CMOS With Optimized On-Chip InductorsDocument10 pagesBandwidth Extension in CMOS With Optimized On-Chip InductorsAlex WongNo ratings yet

- CH 33509513Document5 pagesCH 33509513Shakeel RanaNo ratings yet

- 3 - A - Novel - Nine-Level - Inverter - Employing - One - Voltage - Source - and - Reduced - Components - As - High-Frequency - AC - Power - SourceDocument9 pages3 - A - Novel - Nine-Level - Inverter - Employing - One - Voltage - Source - and - Reduced - Components - As - High-Frequency - AC - Power - Sourcer.ebrahimi1993No ratings yet

- Design of A Transformer-Based Reconfigurable Digital Polar Doherty Power Amplifier Fully Integrated in Bulk CMOSDocument13 pagesDesign of A Transformer-Based Reconfigurable Digital Polar Doherty Power Amplifier Fully Integrated in Bulk CMOSreddy balajiNo ratings yet

- Testing Paper CorrectedDocument9 pagesTesting Paper CorrectedSakthiPriyaNo ratings yet

- Finfets PapersDocument5 pagesFinfets PapershariNo ratings yet

- A Novel Multiplexer-Based Low-Power Full AdderDocument4 pagesA Novel Multiplexer-Based Low-Power Full AdderDeepak RajeshNo ratings yet

- A Very High-Frequency CMOS Complementary Folded Cascode AmplifierDocument4 pagesA Very High-Frequency CMOS Complementary Folded Cascode AmplifierBodhayan PrasadNo ratings yet

- A Review on Design a Low Power Flip Flop Based on a Signal 26bef0lyejDocument4 pagesA Review on Design a Low Power Flip Flop Based on a Signal 26bef0lyejVijay KumarNo ratings yet

- Shepphard 2017Document3 pagesShepphard 2017Алексей КоротковNo ratings yet

- A DTMOS-based Power Efficient Recycling Folded Cascode Operational Transconductance AmplifierDocument12 pagesA DTMOS-based Power Efficient Recycling Folded Cascode Operational Transconductance AmplifierBüşra AkyıldızNo ratings yet

- Fully Integrated Doherty Power Amplifiers For 5 GHZ Wireless-LANsDocument4 pagesFully Integrated Doherty Power Amplifiers For 5 GHZ Wireless-LANsHam Radio HSMMNo ratings yet

- Six-Port Modulator Based RF Transmission System Application in An OFDM EnviromentDocument6 pagesSix-Port Modulator Based RF Transmission System Application in An OFDM EnviromentWalter Santiago Campos ArandaNo ratings yet

- This Document Is Downloaded From DR-NTU, Nanyang Technological University Library, SingaporeDocument10 pagesThis Document Is Downloaded From DR-NTU, Nanyang Technological University Library, SingaporeRavinder KumarNo ratings yet

- A Reconfigurable CMOS Rectifier With 14-DB Power Dynamic Range Achieving Gt36-DB Mm2 FoM for RF-Based Hybrid Energy HarvestingDocument5 pagesA Reconfigurable CMOS Rectifier With 14-DB Power Dynamic Range Achieving Gt36-DB Mm2 FoM for RF-Based Hybrid Energy HarvestingJordan RussellNo ratings yet

- An 8-Bit 120-MS/s Interleaved CMOS Pipeline ADC Based On MOS Parametric AmplificationDocument5 pagesAn 8-Bit 120-MS/s Interleaved CMOS Pipeline ADC Based On MOS Parametric Amplificationjulio perezNo ratings yet

- BUC BiasDocument6 pagesBUC BiasedgarlibanioNo ratings yet

- High Efficiency Gan 2.5 To 9 GHZ Power Amplifiers Realized in Multilayer LCP Hybrid TechnologyDocument3 pagesHigh Efficiency Gan 2.5 To 9 GHZ Power Amplifiers Realized in Multilayer LCP Hybrid TechnologyRabbia SalmanNo ratings yet

- Final ProjectDocument5 pagesFinal Projectnksharma.naveen1855No ratings yet

- Pramod 2019Document12 pagesPramod 2019venkat301485No ratings yet

- Low-Power High-Speed Double Gate 1-Bit Full Adder Cell: Raushan Kumar, Sahadev Roy, and C.T. BhuniaDocument6 pagesLow-Power High-Speed Double Gate 1-Bit Full Adder Cell: Raushan Kumar, Sahadev Roy, and C.T. BhuniaArynNo ratings yet

- Linköping University Post PrintDocument11 pagesLinköping University Post PrintIfeanyi OparaekeNo ratings yet

- Tappered Buffers Literature ReviewDocument5 pagesTappered Buffers Literature ReviewZulfiqar AliNo ratings yet

- Reducing Power Consumption With Relaxed Quasi Delay-Insensitive CircuitsDocument10 pagesReducing Power Consumption With Relaxed Quasi Delay-Insensitive CircuitskattasrinivasNo ratings yet

- 0.9V 32Nm Dual-Gate Si Finfet: Low-Power Ptl-Based Multiplexer Design inDocument4 pages0.9V 32Nm Dual-Gate Si Finfet: Low-Power Ptl-Based Multiplexer Design inNamrata SaxenaNo ratings yet

- Folded Cascode Operational Transconductance Amplifier ThesisDocument6 pagesFolded Cascode Operational Transconductance Amplifier Thesismelissawardbaltimore100% (1)

- An Optimum Vlsi Design of A 16 6-Bit Alu: Ii. Binary Adder R CircuitsDocument4 pagesAn Optimum Vlsi Design of A 16 6-Bit Alu: Ii. Binary Adder R CircuitsBüşra HasılcıNo ratings yet

- Low-Power Pulse-Triggered Flip-Flop Design Based On A Signal Feed-Through SchemeDocument5 pagesLow-Power Pulse-Triggered Flip-Flop Design Based On A Signal Feed-Through SchemeNano Scientific Research Centre pvt ltdNo ratings yet

- A Partially Static High Frequency 18T Hybrid Topological Flip-Flop Design For Low Power ApplicationDocument5 pagesA Partially Static High Frequency 18T Hybrid Topological Flip-Flop Design For Low Power ApplicationRatnakarVarunNo ratings yet

- Improving Power Efficiency of A Two-Stage Operational AmplifierDocument11 pagesImproving Power Efficiency of A Two-Stage Operational AmplifierHenry HuoNo ratings yet

- Improving Performance of Full Adders Using Modified Level RestorersDocument8 pagesImproving Performance of Full Adders Using Modified Level RestorersmadhuNo ratings yet

- A Low-Noise Chopper Amplifier Designed For Multi-Channel Neural Signal AcquisitionDocument11 pagesA Low-Noise Chopper Amplifier Designed For Multi-Channel Neural Signal AcquisitionRajeeNo ratings yet

- Advanced low-power full-adder cell for low voltageDocument6 pagesAdvanced low-power full-adder cell for low voltagedurairajmary100% (1)

- Compact and Wide-Band Efficiency Improved RF Differential Rectifier For Wireless Energy HarvestingDocument4 pagesCompact and Wide-Band Efficiency Improved RF Differential Rectifier For Wireless Energy HarvestingLukas BalciusNo ratings yet

- Continuous-Time Common-Mode Feedback For High-Speed Switched-Capacitor Networks. IEEE Journal of Solid-State Circuits, 40 (8), 1610-1617Document9 pagesContinuous-Time Common-Mode Feedback For High-Speed Switched-Capacitor Networks. IEEE Journal of Solid-State Circuits, 40 (8), 1610-1617LaurMateiNo ratings yet

- A Review of 0.18-m Full Adder Performances For Tree Structured Arithmetic CircuitsDocument10 pagesA Review of 0.18-m Full Adder Performances For Tree Structured Arithmetic CircuitsChandan KumarNo ratings yet

- Low Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationsDocument5 pagesLow Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationssunilsheelavantNo ratings yet

- Broadband Powerline Communication Performance EvaluationDocument21 pagesBroadband Powerline Communication Performance EvaluationNjitnumNo ratings yet

- SDR Implementation of An OFDM Transmitter and Receiver: Jaime Luque Quispe, Jackelyn Tume Ruiz, Luis G. MeloniDocument5 pagesSDR Implementation of An OFDM Transmitter and Receiver: Jaime Luque Quispe, Jackelyn Tume Ruiz, Luis G. MeloniGonzalo HuaracNo ratings yet

- Low Power CMOS Full Adders Using Pass Transistor LogicDocument6 pagesLow Power CMOS Full Adders Using Pass Transistor LogicswathiNo ratings yet

- 4 Watt, 45% Bandwidth Si-LDMOS High Linearity Power Amplifier For Modern Wireless Communication SystemsDocument4 pages4 Watt, 45% Bandwidth Si-LDMOS High Linearity Power Amplifier For Modern Wireless Communication SystemsYanelis GilNo ratings yet

- 10.1007@s40009 020 01016 9Document6 pages10.1007@s40009 020 01016 9Vani YamaniNo ratings yet

- An Efficient DSP FPGA Based Real Time ImDocument8 pagesAn Efficient DSP FPGA Based Real Time ImR&D LivelineNo ratings yet

- Study and Analysis of High Performance Xnor Based 1-Bit Full Adder CellDocument5 pagesStudy and Analysis of High Performance Xnor Based 1-Bit Full Adder CellInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- A High Efficiency Bridgeless Flyback PFC Converter For Adapter ApplicationDocument5 pagesA High Efficiency Bridgeless Flyback PFC Converter For Adapter ApplicationAshwin Kumar JNo ratings yet

- Design and Optimization of Multielement Antennas and RF Circuits For Beamforming With A Reduced Number of RF Front-EndsDocument3 pagesDesign and Optimization of Multielement Antennas and RF Circuits For Beamforming With A Reduced Number of RF Front-EndsFlavia CesarNo ratings yet

- Sad Raf Shari 2016Document9 pagesSad Raf Shari 2016mhmedNo ratings yet

- Modified Low Power Low Area Array Multiplier With SOC EncounterDocument4 pagesModified Low Power Low Area Array Multiplier With SOC EncounterShamia SathishNo ratings yet

- Time-Interleaved and Circuit-Shared Dual-Channel 10 B 200 MS/s 0.18 Analog-to-Digital ConvertorDocument8 pagesTime-Interleaved and Circuit-Shared Dual-Channel 10 B 200 MS/s 0.18 Analog-to-Digital ConvertorKasi BandlaNo ratings yet

- Highly Integrated Gate Drivers for Si and GaN Power TransistorsFrom EverandHighly Integrated Gate Drivers for Si and GaN Power TransistorsNo ratings yet

- Automated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsFrom EverandAutomated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsNo ratings yet

- A 4x4 Modified 8T SRAM Cell Array Using Power Gating TechniqueDocument7 pagesA 4x4 Modified 8T SRAM Cell Array Using Power Gating TechniqueArvind ChakrapaniNo ratings yet

- AIP ProceedingsDocument66 pagesAIP ProceedingsArvind ChakrapaniNo ratings yet

- A Millimeter-Wave Generation Scheme Based On Frequency Octupling Using LiNbO3 Mach-Zehnder ModulatorDocument8 pagesA Millimeter-Wave Generation Scheme Based On Frequency Octupling Using LiNbO3 Mach-Zehnder ModulatorArvind ChakrapaniNo ratings yet

- A Novel 8T SRAM Cell With Reduction in Power Using Power Gating TechniqueDocument4 pagesA Novel 8T SRAM Cell With Reduction in Power Using Power Gating TechniqueArvind ChakrapaniNo ratings yet

- Extraction of The Molecular Level Biomedical Event Trigger Based On Gene Ontology Using Radial Belief Neural Network TechniquesDocument10 pagesExtraction of The Molecular Level Biomedical Event Trigger Based On Gene Ontology Using Radial Belief Neural Network TechniquesArvind ChakrapaniNo ratings yet

- Weighted Soft ComputingDocument13 pagesWeighted Soft ComputingArvind ChakrapaniNo ratings yet

- QPDocument3 pagesQPArvind ChakrapaniNo ratings yet

- Tuto 2Document4 pagesTuto 2Arvind ChakrapaniNo ratings yet

- Control Systems Unit Test 1 AnswersDocument1 pageControl Systems Unit Test 1 AnswersArvind ChakrapaniNo ratings yet

- A Novel Scheme For Optical Millimeter Wave Generation Using Linbo Mach - Zehnder Modulator Without AmplifierDocument8 pagesA Novel Scheme For Optical Millimeter Wave Generation Using Linbo Mach - Zehnder Modulator Without AmplifierArvind ChakrapaniNo ratings yet

- High Performance Low Power Low Voltage Adder: A. Wu and C.K. NGDocument2 pagesHigh Performance Low Power Low Voltage Adder: A. Wu and C.K. NGArvind ChakrapaniNo ratings yet

- Smart Dustbin Monitoring System LAN Server and ArduinoDocument4 pagesSmart Dustbin Monitoring System LAN Server and ArduinoArvind ChakrapaniNo ratings yet

- 10.1007 - s40009 018 0766 3Document8 pages10.1007 - s40009 018 0766 3Arvind ChakrapaniNo ratings yet

- Vivekanandar StoriesDocument27 pagesVivekanandar StoriesArvind ChakrapaniNo ratings yet

- Novel Splitter Based Parallel MultiplierDocument7 pagesNovel Splitter Based Parallel MultiplierArvind ChakrapaniNo ratings yet

- IJARCCE8D A Smart Navin Real Time EmbeddedDocument4 pagesIJARCCE8D A Smart Navin Real Time EmbeddedArvind ChakrapaniNo ratings yet

- ADS IntroductionDocument14 pagesADS IntroductionsaiknaramNo ratings yet

- CHAPTER 4 ElectronicsDocument47 pagesCHAPTER 4 ElectronicsrenuNo ratings yet

- Panasonic Sa-Ht855e Eb EgDocument119 pagesPanasonic Sa-Ht855e Eb EgNuno SobreiroNo ratings yet

- PLDDocument81 pagesPLDAntonio SabaNo ratings yet

- 3RW4436-6BC44 en PDFDocument4 pages3RW4436-6BC44 en PDFOmar GuillenNo ratings yet

- Flash MemoryDocument18 pagesFlash Memoryamit.c.parekh131786% (7)

- Cargador de Baterias 12V 4ahDocument4 pagesCargador de Baterias 12V 4ahRamón Antonio Rodríguez DíazNo ratings yet

- Facts DevicesDocument18 pagesFacts DevicesKANCHIVIVEKGUPTANo ratings yet

- MacSpice - User's Guide (TOC)Document5 pagesMacSpice - User's Guide (TOC)Lee RickHunter0% (1)

- Automatic Voltage Regulating Relay EE 301-M: Instruction ManualDocument22 pagesAutomatic Voltage Regulating Relay EE 301-M: Instruction ManualnarendragahlotNo ratings yet

- p7211 e PDFDocument4 pagesp7211 e PDFritasilabannatalieNo ratings yet

- ENSC 450 FINAL EXAM KEY POINTSDocument22 pagesENSC 450 FINAL EXAM KEY POINTSYoujung KimNo ratings yet

- Intel Processors: Timothy Render and Carlton MataraDocument19 pagesIntel Processors: Timothy Render and Carlton MataraVenkat Kiran SribhashyamNo ratings yet

- Energy Band DiagramDocument6 pagesEnergy Band DiagramAlyssa GuiyabNo ratings yet

- SB1660CTDocument2 pagesSB1660CTEvaNo ratings yet

- Ag-Doped SnSe2 As A Promising Mid-Temperature Thermoelectric MaterialDocument11 pagesAg-Doped SnSe2 As A Promising Mid-Temperature Thermoelectric MaterialAhmed Fouad MusaNo ratings yet

- Linear Integrated Circuits Lab ManualDocument104 pagesLinear Integrated Circuits Lab ManualNandha KumarNo ratings yet

- Alpha Lubricator MC-S (Education)Document37 pagesAlpha Lubricator MC-S (Education)AkhilvjohnNo ratings yet

- 18727-MS Microstepping Motor Driver Setup GuideDocument8 pages18727-MS Microstepping Motor Driver Setup GuideAbdo AbdoNo ratings yet

- 2222 PDFDocument7 pages2222 PDFciro mendezNo ratings yet

- Irfpc50, Sihfpc50: Vishay SiliconixDocument9 pagesIrfpc50, Sihfpc50: Vishay Siliconixxor_45No ratings yet

- schematic-design-review-checklistDocument4 pagesschematic-design-review-checklistraphael.souzaNo ratings yet

- Uc3842b 3843BDocument10 pagesUc3842b 3843Bbob75No ratings yet

- Doping SemiconductorsDocument4 pagesDoping SemiconductorsPratheek UNo ratings yet

- Calidades TonillosDocument29 pagesCalidades TonillosEliezer BrachoNo ratings yet

- Unit 1-ERTS QBDocument5 pagesUnit 1-ERTS QBBabuKannanNo ratings yet