Professional Documents

Culture Documents

Time Analysis Seq CKT

Uploaded by

arpit sharmaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Time Analysis Seq CKT

Uploaded by

arpit sharmaCopyright:

Available Formats

ENGIN 112

Intro to Electrical and Computer Engineering

Lecture 28

Timing Analysis

ENGIN112 L28: Timing Analysis November 7, 2003

Overview

° Circuits do not respond instantaneously to input

changes

° Predictable delay in transferring inputs to outputs

• Propagation delay

° Sequential circuits require a periodic clock

° Goal: analyze clock circuit to determine maximum

clock frequency

• Requires analysis of paths from flip-flop outputs to flip-flop inputs

° Even after inputs change, output signal of circuit

maintains original output for short time

• Contamination delay

ENGIN112 L28: Timing Analysis November 7, 2003

Sequential Circuits

° Sequential circuits can contain both combinational

logic and edge-triggered flip flops

° A clock signal determines when data is stored in flip

flops

° Goal: How fast can the circuit operate?

• Minimum clock period: Tmin

• Maximum clock frequency: fmax

° Maximum clock frequency is the inverse of the

minimum clock period

• 1/Tmin = fmax Clock

Period

Clock

ENGIN112 L28: Timing Analysis November 7, 2003

Combinational Logic Timing: Inverter

A Y Y

t cd

t pd

° Combinational logic is made from electronic circuits

• An input change takes time to propagate to the output

° The output remains unchanged for a time period

equal to the contamination delay, tcd

° The new output value is guaranteed to valid after a

time period equal to the propagation delay, tpd

ENGIN112 L28: Timing Analysis November 7, 2003

Combinational Logic Timing: XNOR Gate

A

A

B C

B

C

t cd

t pd

° The output is guaranteed to be stable with old

value until the contamination delay

• Unknown values shown in waveforms as Xs

° The output is guaranteed to be stable with the new

value after the propagation delay

ENGIN112 L28: Timing Analysis November 7, 2003

Combinational Logic Timing: complex circuits

Tpd = 2ns

Tcd = 1ns

Circuit X

Tpd = 3ns

Tcd = 1ns

A

C A

Circuit X C

B

Tpd = 5ns

B Tcd = 1ns

° Propagation delays are additive

• Locate the longest combination of tpd

° Contamination delays may not be additive

• Locate the shortest path of tcd

° Find propagation and contamination delay of new,

combined circuit

ENGIN112 L28: Timing Analysis November 7, 2003

Clocked Device: Contamination and Propagation Delay

D Q

D

Clk

Q

tcd

tClk-Q

° Timing parameters for clocked devices are specified

in relation to the clock input (rising edge)

° Output unchanged for a time period equal to the

contamination delay, tcd after the rising clock edge

° New output guaranteed valid after time equal to

the propagation delay, tClk-Q

• Follows rising clock edge

ENGIN112 L28: Timing Analysis November 7, 2003

Clocked Devices: Setup and Hold Times

ts th

D Q

D

Clk

° Timing parameters for clocked devices are specified

in relation to the clock input (rising edge)

° D input must be valid at least ts (setup time) before

the rising clock edge

° D input must be held steady th (hold time) after

rising clock edge

° Setup and hold are input restrictions

• Failure to meet restrictions causes circuit to operate incorrectly

ENGIN112 L28: Timing Analysis November 7, 2003

Edge-Triggered Flip Flop Timing

CLK

th = hold time

ts = setup time

° The logic driving the flip flop must ensure that

setup and hold are met

° Timing values (tcd tpd tClk-Q ts th)

ENGIN112 L28: Timing Analysis November 7, 2003

Analyzing Sequential Circuits

TClk-Q = 5ns Tpd = 5ns TClk-Q = 5 ns

Ts = 2 ns

D X Y

Comb.

D Q D Q Z

Logic

FFA FFB

G

CLK

° What is the minimum time between rising clock

edges?

• Tmin = TCLK-Q (FFA) + Tpd (G) + Ts (FFB)

° Trace propagation delays from FFA to FFB

° Draw the waveforms! Fmax = _______

ENGIN112 L28: Timing Analysis November 7, 2003

Analyzing Sequential Circuits

Tpd = 4ns

Comb.

Logic F

X Y

Comb.

D Q D Q Z

Logic H

FFA FFB

Tpd = 5ns

CLK

TClk-Q = 5ns

TClk-Q = 4 ns

Ts = 2 ns

° What is the minimum clock period (Tmin) of this

circuit? Hint: evaluate all FF to FF paths

° Maximum clock frequency is 1/T min

ENGIN112 L28: Timing Analysis November 7, 2003

Analyzing Sequential Circuits

Tpd = 4ns

Comb.

Fmax = _______ Logic F

X Y

Comb.

D Q D Q Z

Logic H

FFA FFB

Tpd = 5ns

CLK

TClk-Q = 5ns

TClk-Q = 4 ns

Ts = 2 ns

° Path FFA to FFB

• TClk-Q(FFA) + Tpd(H) + Ts(FFB) = 5ns + 5ns + 2ns = 12ns

° Path FFB to FFB

• TCLK-Q(FFB) + Tpd(F) + Tpd(H) + Ts(FFB) = 4ns + 4ns + 5ns + 2ns

ENGIN112 L28: Timing Analysis November 7, 2003

Analyzing Sequential Circuits: Hold Time Violation

Tcd = 1ns Tcd = 2ns Th = 2 ns

D X Y

Comb.

D Q D Q Z

Logic

FFA FFB

G

CLK

° One more issue: make sure Y remains stable for hold

time (Th) after rising clock edge

° Remember: contamination delay ensures signal

doesn’t change

° How long before first change arrives at Y?

• Tcd(FFA) + Tcd(G) >= Th

• 1ns + 2ns > 2ns

ENGIN112 L28: Timing Analysis November 7, 2003

Analyzing Sequential Circuits: Hold Time Violations

Tcd = 1ns

All paths must satisfy requirements

Comb.

Logic F

X Y

Comb.

D Q D Q Z

Logic H

FFA FFB

Tcd = 2ns

CLK

TClD = 1ns

TClD = 1 ns

Th = 2 ns

° Path FFA to FFB

• TCD(FFA) + TCD(H) > Th(FFB) = 1 ns + 2ns > 2ns

° Path FFB to FFB

• TCD(FFB) + TCD(F) + TCd(H) > Th(FFB) = 1ns + 1ns + 2ns > 2ns

ENGIN112 L28: Timing Analysis November 7, 2003

Summary

° Maximum clock frequency is a fundamental parameter

in sequential computer systems

° Possible to determined clock frequency from

propagation delays and setup time

° The longest path determines the clock frequenct

° All flip-flop to flip-flop paths must be checked

° Hold time are satisfied by examining contamination

delays

° The shortest contamination delay path determines if

hold times are met

° Check handout for more details and examples.

ENGIN112 L28: Timing Analysis November 7, 2003

You might also like

- Gate-Level Timing Analysis ExplainedDocument41 pagesGate-Level Timing Analysis ExplainedNiloy RoyNo ratings yet

- Archl FSM 04Document52 pagesArchl FSM 04Ajax KrausNo ratings yet

- Discrete-Time IIR Filter Design From Continuous-Time FiltersDocument16 pagesDiscrete-Time IIR Filter Design From Continuous-Time FiltersstudentNo ratings yet

- OFDMDocument15 pagesOFDMAvinash RaghooNo ratings yet

- LSI Logic Design Chapter 2 ExtraDocument7 pagesLSI Logic Design Chapter 2 Extradu.le0802No ratings yet

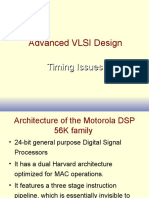

- Advanced VLSI Design: Timing IssuesDocument88 pagesAdvanced VLSI Design: Timing IssuesSudhanshu BadolaNo ratings yet

- CEN212 Unit 2 DR KhursheedDocument123 pagesCEN212 Unit 2 DR Khursheedمنصور الهماميNo ratings yet

- Lecture 2Document11 pagesLecture 2Ed CastroNo ratings yet

- Sampling of Continuous-Time SignalsDocument11 pagesSampling of Continuous-Time SignalsfarhanshakeelNo ratings yet

- Seminar on Time Borrowing & Clock Skew TechniquesDocument18 pagesSeminar on Time Borrowing & Clock Skew TechniquesNitin Suyan PanchalNo ratings yet

- ECE 3512 - Signal Modulation and Demodulation TechniquesDocument15 pagesECE 3512 - Signal Modulation and Demodulation TechniquesRicha SharmaNo ratings yet

- QPSK Experiment No 4 (31-May-2023)Document3 pagesQPSK Experiment No 4 (31-May-2023)shovanjitmaity2No ratings yet

- Clocking Part 2Document4 pagesClocking Part 2Dmitry LeyzerovichNo ratings yet

- Lecture11 PDFDocument26 pagesLecture11 PDFTimothy EngNo ratings yet

- Analog and Digital VLSI Design: Lecture 20 - 21: Delay Estimation Using Logical EffortDocument19 pagesAnalog and Digital VLSI Design: Lecture 20 - 21: Delay Estimation Using Logical EffortYash GuptaNo ratings yet

- CSE 140L Lecture 6 Interface and State AssignmentDocument19 pagesCSE 140L Lecture 6 Interface and State AssignmentMani NellantiNo ratings yet

- Mos Inverter DynamicDocument39 pagesMos Inverter DynamicvinothrathinamNo ratings yet

- Timing Parameters of A Digital CircuitDocument7 pagesTiming Parameters of A Digital CircuitShwetabhAsthanaNo ratings yet

- Metastability and Clock Domain Crossing: IN3160 IN4160Document30 pagesMetastability and Clock Domain Crossing: IN3160 IN4160kumarNo ratings yet

- 6004 Spring 1998: L10: Clocking and The Dynamic DisciplineDocument8 pages6004 Spring 1998: L10: Clocking and The Dynamic Disciplinemohammed zubairNo ratings yet

- FF in VHDL PDFDocument5 pagesFF in VHDL PDFzakaria zakariyaNo ratings yet

- 5 - A/D and D/A Conversion: Systems For Digital Signal ProcessingDocument35 pages5 - A/D and D/A Conversion: Systems For Digital Signal ProcessingBomber KillerNo ratings yet

- 04 Design in Hazard States PDFDocument43 pages04 Design in Hazard States PDFJignesh GunasegerenNo ratings yet

- ECE465 Clocking Methodologies Lecture NotesDocument21 pagesECE465 Clocking Methodologies Lecture NotesMohammed El-AdawyNo ratings yet

- MIMO Antenna Systems for Wireless CommunicationDocument15 pagesMIMO Antenna Systems for Wireless CommunicationThilaga MohanNo ratings yet

- SampleingDocument13 pagesSampleinganthony.onyishi.242680No ratings yet

- ECE1371 NoiseSC-2Document22 pagesECE1371 NoiseSC-2Ron JosephNo ratings yet

- Design and Implementation of VLSI SystemsDocument55 pagesDesign and Implementation of VLSI SystemsLê Bá Phước LongNo ratings yet

- A/D and D/A Converter FundamentalsDocument18 pagesA/D and D/A Converter FundamentalskarkeraNo ratings yet

- EE 459/500 - HDL Based Digital Design With Programmable Logic Timing and Clock IssuesDocument23 pagesEE 459/500 - HDL Based Digital Design With Programmable Logic Timing and Clock Issuessneha96669No ratings yet

- L25 - Datapath Design - p1Document46 pagesL25 - Datapath Design - p1Shanawar AliNo ratings yet

- Logic Gate Delay ModelingDocument45 pagesLogic Gate Delay ModelingDevendra GoswamiNo ratings yet

- Adaptive Modulation Reduction of Peak-to-Average Power Ratio Channel Estimation OFDM in Frequency Selective Fading ChannelDocument49 pagesAdaptive Modulation Reduction of Peak-to-Average Power Ratio Channel Estimation OFDM in Frequency Selective Fading ChannelDong WangNo ratings yet

- MIMODocument15 pagesMIMOMitraNo ratings yet

- Nyquist Sampling Theorem and Signal ReconstructionDocument13 pagesNyquist Sampling Theorem and Signal ReconstructionSalmaanCadeXaajiNo ratings yet

- InverterDocument231 pagesInverterMaitrik Shah100% (1)

- Timing Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignDocument33 pagesTiming Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignVarun KondagunturiNo ratings yet

- CD4013B CMOS Dual D-Type Flip-Flop: 1 Features 3 DescriptionDocument30 pagesCD4013B CMOS Dual D-Type Flip-Flop: 1 Features 3 DescriptionDama DamaNo ratings yet

- CD4013B CMOS Dual D-Type Flip-Flop: 1 Features 3 DescriptionDocument28 pagesCD4013B CMOS Dual D-Type Flip-Flop: 1 Features 3 DescriptionjwestmisterNo ratings yet

- Slides Robin AutotuningDocument19 pagesSlides Robin AutotuningJorge MunozNo ratings yet

- Performance Characterization PDFDocument46 pagesPerformance Characterization PDFSankalp JainNo ratings yet

- GPS Signal Structure: - SourcesDocument23 pagesGPS Signal Structure: - Sourcessoumya_cu100% (2)

- Buffer InsertionDocument47 pagesBuffer InsertionAkhil MehtaNo ratings yet

- CIRCUIT BASIC CONCEPTSDocument43 pagesCIRCUIT BASIC CONCEPTSmonisa kannanNo ratings yet

- High Frequency Voltage Controlled Ring Oscillators in Standard CMOSDocument18 pagesHigh Frequency Voltage Controlled Ring Oscillators in Standard CMOSKaan AyyildizNo ratings yet

- DC Lab ManualDocument27 pagesDC Lab ManualkslnNo ratings yet

- Lecture 5Document51 pagesLecture 5abd rocksNo ratings yet

- Ofdm PrencipleDocument18 pagesOfdm PrencipleAhmed FadulNo ratings yet

- SeminarDocument200 pagesSeminarMudassarNo ratings yet

- Lecture03 Ee620 PLL SystemDocument128 pagesLecture03 Ee620 PLL SystemPeygamberinizi SikiyimNo ratings yet

- Setup1 1210Document32 pagesSetup1 1210Akhila PurushothamanNo ratings yet

- ASIC Construction: Floor Planning, Placement and RoutingDocument40 pagesASIC Construction: Floor Planning, Placement and RoutingsiddhasenNo ratings yet

- S&W Performance, and Go-back-N ARQ: Unit 02.01.03 CS 5220: Computer CommunicationsDocument13 pagesS&W Performance, and Go-back-N ARQ: Unit 02.01.03 CS 5220: Computer CommunicationsKlaus BertokNo ratings yet

- Delay Time Estimation in Digital DesignDocument12 pagesDelay Time Estimation in Digital DesignSandeep PaulNo ratings yet

- Lec 3Document24 pagesLec 3dwirelesNo ratings yet

- Understanding Sampling Theory for Signal ProcessingDocument17 pagesUnderstanding Sampling Theory for Signal ProcessingMuhammad Muinul IslamNo ratings yet

- Lecture 10 PDFDocument5 pagesLecture 10 PDFMehdi RabbaniNo ratings yet

- WINSEM2021-22 ECE5014 ETH VL2021220505486 Reference Material III 27-04-2022 STA Fundamentals Session2Document31 pagesWINSEM2021-22 ECE5014 ETH VL2021220505486 Reference Material III 27-04-2022 STA Fundamentals Session2AMIT VERMANo ratings yet

- Designation Wise Scale of PayDocument3 pagesDesignation Wise Scale of Payarpit sharmaNo ratings yet

- EthicsDocument20 pagesEthicsankursonicivilNo ratings yet

- ESSAY CompulsaryDocument2 pagesESSAY CompulsaryAbhishekVadadoriyaNo ratings yet

- Rajasthan Rajya Vidyut Utpadan Nigam LTD.: Vacancies of Assistant Engineer (Electrical) in RvunDocument1 pageRajasthan Rajya Vidyut Utpadan Nigam LTD.: Vacancies of Assistant Engineer (Electrical) in Rvunarpit sharmaNo ratings yet

- IAF Exercise, Pasighat Airport, Quit India Movement, Statue of UnityDocument2 pagesIAF Exercise, Pasighat Airport, Quit India Movement, Statue of Unityarpit sharmaNo ratings yet

- ENGIN 112 Intro To Electrical and Computer Engineering: Circuit Analysis ProcedureDocument13 pagesENGIN 112 Intro To Electrical and Computer Engineering: Circuit Analysis ProcedureIsrar UllahNo ratings yet

- Basic network elements and their propertiesDocument7 pagesBasic network elements and their propertiesarpit sharmaNo ratings yet

- BCD To OtherDocument18 pagesBCD To Otherarpit sharmaNo ratings yet

- Alphabetical List of Towns and Their Population: RajasthsanDocument8 pagesAlphabetical List of Towns and Their Population: Rajasthsanarpit sharmaNo ratings yet

- Lesson 44 Line Integral: 44.2.1 ExampleDocument6 pagesLesson 44 Line Integral: 44.2.1 Examplearpit sharmaNo ratings yet

- Session 5 Logic GatesDocument3 pagesSession 5 Logic Gateszaibakhan8No ratings yet

- Digital Electronics Objective QuestionsDocument8 pagesDigital Electronics Objective QuestionsVishnu Priya50% (2)

- Lesson 6 Eigenvalues and Eigenvectors of MatricesDocument8 pagesLesson 6 Eigenvalues and Eigenvectors of Matricesarpit sharmaNo ratings yet

- EE201 Network TheoremsDocument14 pagesEE201 Network Theoremsapi-26587237100% (2)

- Difference Eqn PDFDocument11 pagesDifference Eqn PDFarpit sharmaNo ratings yet

- Guass Div THDocument5 pagesGuass Div THarpit sharmaNo ratings yet

- EE201 Network TheoremsDocument14 pagesEE201 Network Theoremsapi-26587237100% (2)

- Lesson 8 Diagonalization of Matrices: Module 1: Matrices and Linear AlgebraDocument8 pagesLesson 8 Diagonalization of Matrices: Module 1: Matrices and Linear Algebraarpit sharmaNo ratings yet

- Guass Div THDocument5 pagesGuass Div THarpit sharmaNo ratings yet

- Vector Calculus Divergence and CurlDocument4 pagesVector Calculus Divergence and Curlarpit sharmaNo ratings yet

- Stocks TheoramDocument5 pagesStocks Theoramarpit sharmaNo ratings yet

- Gauss Jordan Method For Solving Systems of Linear EquationsDocument5 pagesGauss Jordan Method For Solving Systems of Linear Equationsciki1100% (2)

- Module 4: Special Types of First Order Non-Linear PDEsDocument5 pagesModule 4: Special Types of First Order Non-Linear PDEsarpit sharmaNo ratings yet

- Linear Algebra: Simultaneous Linear EquationsDocument19 pagesLinear Algebra: Simultaneous Linear EquationsTarun SharmaNo ratings yet

- Fourier Transform to Solve PDEsDocument4 pagesFourier Transform to Solve PDEsrisehighNo ratings yet

- Prob 07Document9 pagesProb 07surbhi pareekNo ratings yet

- The Fourier Transform ExplainedDocument35 pagesThe Fourier Transform ExplainedThanatkrit KaewtemNo ratings yet

- Differences and Z-TransformsDocument10 pagesDifferences and Z-Transformsarpit sharmaNo ratings yet

- Differences and Z-TransformsDocument10 pagesDifferences and Z-Transformsarpit sharmaNo ratings yet

- MK - ND10 NC10 NP-N108 N110 Winchester-R - 0113 - Final BA41-01050A BA41-01051A BA41-01051A 010Document56 pagesMK - ND10 NC10 NP-N108 N110 Winchester-R - 0113 - Final BA41-01050A BA41-01051A BA41-01051A 010Alejandro BaroneNo ratings yet

- TimersDocument22 pagesTimersghulam mustafaNo ratings yet

- Jntu Hyd 3 2 It Embsys Set 1Document5 pagesJntu Hyd 3 2 It Embsys Set 1Sri DNo ratings yet

- PC Interfacing Fourth Level Lecture Four: Experiment Board Design and Expanding The CentronicDocument9 pagesPC Interfacing Fourth Level Lecture Four: Experiment Board Design and Expanding The Centronicأسامة المياحيNo ratings yet

- 6309 1Document4 pages6309 1electronitelNo ratings yet

- Quizzes: Chapter 05Document6 pagesQuizzes: Chapter 05Kiệt Trương AnhNo ratings yet

- ARM Lab MannualDocument136 pagesARM Lab MannualRanjith M KumarNo ratings yet

- 08 - LCD TutorialDocument3 pages08 - LCD TutorialicaanmpzNo ratings yet

- Unit 2Document15 pagesUnit 2Abishek NeupaneNo ratings yet

- Aes-z7pz-Sdr2-Dev-g-fmc Revc Schem 02 039799c Top 0Document12 pagesAes-z7pz-Sdr2-Dev-g-fmc Revc Schem 02 039799c Top 0Mauricio Reyna CameroNo ratings yet

- HP ProBook 4720s Wistron Laptop SchematicsDocument62 pagesHP ProBook 4720s Wistron Laptop SchematicsjoaquinmjuanNo ratings yet

- MPMC AakashDocument18 pagesMPMC AakashAarushi SaxenaNo ratings yet

- Elmore Delay, Logical EffortDocument47 pagesElmore Delay, Logical EffortAtul YadavNo ratings yet

- Multi Function Sata Quick Dock - ManhattanDocument2 pagesMulti Function Sata Quick Dock - ManhattanPiergiorgio BassoNo ratings yet

- Update to Promate display panel specificationsDocument3 pagesUpdate to Promate display panel specificationsIonescu CristinaNo ratings yet

- Introduction - Computer ArchitectureDocument37 pagesIntroduction - Computer ArchitecturemuiNo ratings yet

- EDA Introduction: Professor: Sci.D., Prof. Vazgen MelikyanDocument57 pagesEDA Introduction: Professor: Sci.D., Prof. Vazgen MelikyanThi NguyenNo ratings yet

- Design and Performance Analysis of a Low-Power Double-Tail ComparatorDocument5 pagesDesign and Performance Analysis of a Low-Power Double-Tail ComparatorSayantan RoyNo ratings yet

- Bios Cmos MemoryDocument23 pagesBios Cmos MemoryEmman BalicoNo ratings yet

- Read Modify Write CoreDocument1 pageRead Modify Write CoreevaNo ratings yet

- 3ware 9500s 12kDocument2 pages3ware 9500s 12kmaldelreyNo ratings yet

- AT89S52 Micro Controller FeaturesDocument2 pagesAT89S52 Micro Controller FeaturesDibesh Grg100% (2)

- DSP-8 (DSP Processors)Document8 pagesDSP-8 (DSP Processors)Sathish BalaNo ratings yet

- User'S Manual of Intel G41 Express Chipset & Intel ICH7 Chipset BasedDocument16 pagesUser'S Manual of Intel G41 Express Chipset & Intel ICH7 Chipset BasedTony KututoNo ratings yet

- ZX Next Dev Guide r2Document231 pagesZX Next Dev Guide r2y3p3t0No ratings yet

- w25q32fv Revh 091613Document99 pagesw25q32fv Revh 091613aldo_suviNo ratings yet

- Compal La-6582p r1.0 Schematics PDFDocument49 pagesCompal La-6582p r1.0 Schematics PDFdinnhowNo ratings yet

- B.E. B.Tech. - III Semester (R2011) - REGULAR & ARREARDocument1 pageB.E. B.Tech. - III Semester (R2011) - REGULAR & ARREARSundar MahalingamNo ratings yet

- Dell PowerEdge R230 SpecSheet FinalDocument2 pagesDell PowerEdge R230 SpecSheet FinalAdy Nex TNo ratings yet

- CMOS VLSI Design Introduction to AddersDocument44 pagesCMOS VLSI Design Introduction to AdderssoniyaNo ratings yet