Professional Documents

Culture Documents

APW8868C: Features General Description

Uploaded by

Felix BlancoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

APW8868C: Features General Description

Uploaded by

Felix BlancoCopyright:

Available Formats

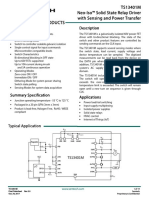

APW8868C

DDR2 AND DDR3/DDR3L SYNCHRONOUS BUCK CONTROLLER

WITH 1.5A LDO SUPPORT LOW IQ

Features General Description

Buck Controller (VDDQ)

The APW8868C integrates a synchronous buck PWM con-

• High Input Voltages Range from 3V to 28V Input

troller to generate VDDQ, a sourcing and sinking LDO

Power

linear regulator to generate VTT. It offers the lowest total

• Provide Adjustable Output Voltage from 0.75V to solution cost in system where space is at a premium.

5.5V +1% Accuracy over Temperature

The APW8868C provides excellent transient response

• Integrated MOSFET Drivers and Bootstrap Forward

and accurate DC voltage output in either PFM or PWM

P-CH MOSFET

Mode. In Pulse Frequency Mode (PFM), the APW8868C

• Low Quiescent Current (200µA)

provides very high efficiency over light to heavy loads with

• Excellent Line and Load Transient Responses loading-modulated switching frequencies. On TQFN-20

• PFM Mode for Increased Light Load Efficiency Package, the Forced PWM Mode works nearly at con-

• Constant On-Time Controller Scheme stant frequency for low-noise requirements.

- Switching Frequency Compensation for PWM

The APW8868C is equipped with accurate current-limit,

Mode

output under-voltage, and output over-voltage protections.

- Adjustable Switching Frequency from 400kHz to

A Power-On- Reset function monitors the voltage on VCC

550kHz in PWM Mode with DC Output Current

prevents wrong operation during power on.

• S3 and S5 Pins Control The Device in S0, S3 or S4/

The LDO is designed to provide a regulated voltage with

S5 State

bi-directional output current for DDR-SDRAM termination.

• Power Good Monitoring

The device integrates two power transistors to source or

• 70% Under-Voltage Protection (UVP)

sink current up to 1.5A. It also incorporates current-limit

• 125% Over-Voltage Protection (OVP) and thermal shutdown protection.

• Adjustable Current-Limit Protection

The output voltage of LDO tracks the voltage at VREF pin.

- Using Sense Low-Side MOSFET’s RDS(ON)

An internal resistor divider is used to provide a half volt-

• TQFN-20 3mmx3mm Thin package

age of VREF for VTTREF and VTT Voltage. The VTT output

• Lead Free Available (RoHS Compliant)

voltage is only requiring 20µF of ceramic output capaci-

+1.5A LDO Section (VTT)

tance for stability and fast transient response. The S3

• Sourcing or Sinking Current up to 1.5A and S5 pins provide the sleep state for VTT (S3 state)

• Fast Transient Response for Output Voltage and suspend state (S4/S5 state) for device, when S5 and

• Output Ceramic Capacitors Support at least 10µF S3 are both pulled low the device provides the soft-off for

MLCC VTT and VTTREF.

• VTT and VTTREF Track at Half the VDDQSNS by

internal divider

• +20mV Accuracy for VTT and VTTREF

• Independent Over-Current Limit (OCL)

• Thermal Shutdown Protection

Copyright ANPEC Electronics Corp. 1 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Simplified Application Circuit Applications

5V

VIN • DDR2, and DDR3/DDR3L Memory Power Supplies

+3V~28V

VCC CS • SSTL-2 SSTL-18 and HSTL Termination

Q1 RCS

VDDQ LOUT

PWM

Q2 DDR

LDO VTT

VDDQ/2

S3 S5

Ordering and Marking Information

APW8868C

Package Code

QB : TQFN3x3-20

Lead Free Code Operating Ambient Temperature Range

I : -40 to 85 °C

Handling Code Handling Code

TR : Tape & Reel

Temperature Range Lead Free Code

G : Halogen and Lead Free Device

Package Code

APW

APW8868C QB : 8868C XXXXX - Date Code

XXXXX

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which

are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for

MSL classification at lead-free peak reflow temperature. ANPEC defines “Green” to mean lead-free (RoHS compliant) and halogen

free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by

weight).

Pin Configuration

PHASE

UGATE

LDOIN

BOOT

VTT

20 19 18 17 16

VTTGND 1 15 LGATE

VTTSNS 2 14 PGND

21

GND 3 13 CS

PGND

VTTREF 4 12 VCC

VDDQSNS 5 11 VCC

6 7 8 9 10

FB

TON

PGOOD

S3

S5

= Thermal Pad (connected to GND plane for better heat

dissipation)

Copyright ANPEC Electronics Corp. 2 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Absolute Maximum Ratings (Note 1,2)

Symbol Parameter Rating Unit

VCC VCC Supply Voltage (VCC to GND) -0.3 ~ 7 V

VBOOT BOOT Supply Voltage (BOOT to PHASE) -0.3 ~ 7 V

VBOOT-GND BOOT Supply Voltage (BOOT to GND) -0.3 ~ 35 V

UGATE Voltage (UGATE to PHASE)

<400ns pulse width -5 ~ VBOOT+0.3 V

>400ns pulse width -0.3 ~ VBOOT+0.3

LGATE Voltage (LGATE to GND)

<400ns pulse width -5 ~ VCC+0.3 V

>400ns pulse width -0.3 ~ VCC+0.3

PHASE Voltage (PHASE to GND)

<400ns pulse width -5 ~ 35 V

>400ns pulse width -0.3 ~ 28

PGND, VTTGND and CS_GND to GND Voltage -0.3 ~ 0.3 V

All Other Pins (CS,S3, S5, VTTSNS, VDDQSNS, VLDOIN, VFB,

-0.3 ~ 7 V

PGOOD, VTT, VTTREF GND)

o

Tj Maximum Junction Temperature 150 C

o

TSTG Storage Temperature -65 ~ 150 C

o

TSDR Maximum Soldering Temperature, 10 Seconds 260 C

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are

stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recom-

mended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device

reliability

Note 2: The device is ESD sensitive. Handling precautions are recommended.

Thermal Characteristics (Note 3)

Symbol Parameter Typical Value Unit

θJA Thermal Resistance -Junction to Ambient °C/W

50

θJC Thermal Resistance -Junction to Case °C/W

8

Note 3: θJA and θJCare measured with the component mounted on a high effective the thermal conductivity test board in free air. The

exposed pad of package is soldered directly on the PCB

Copyright ANPEC Electronics Corp. 3 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Recommended Operating Conditions (Note 4)

Symbol Parameter Range Unit

VCC VCC Supply Voltage 4.5 ~ 5.5 V

VIN Converter Input Voltage 3 ~ 28 V

VVDDQ Converter Output Voltage 0.75 ~5.5V V

VVTT LDO Output Voltage 0.375 ~ 2.75 V

IOUT Converter Output Current 0 ~ 15 A

IVTT LDO Output Current -1.5 ~ +1.5 A

CVCC VCC Capacitance 1~ µF

CVTT VTT Output Capacitance 10~100 µF

CVTTREF VTTREF Output Capacitance 0.01~0.1 µF

o

TA Ambient Temperature -40 ~ 85 C

o

TJ Junction Temperature -40 ~ 125 C

Note 4: Refer to the typical application circuit.

Electrical Characteristics

Refer to the typical application circuits. These specifications apply over V VCC=V BOOT=5V, V IN=12V and T A= -40 ~ 85oC, unless

otherwise specified. Typical values are at TA=25oC.

APW 8868 C

Sym bol Param eter Test Conditions Unit

Min Typ Max

SUP PLY CURRENT

I VC C VCC S upp ly Curre nt o

T A = 2 5 C, VS3 = V S5 = 5V, no load , VCC Cu rrent - 180 2 20 µA

o

T A = 2 5 C, VS3 = 0 V, V S5 = 5V, no load, VCC

I VC CSTB VCC Standb y Curre nt - 120 1 60 µA

Current

o

I VC CSDN VCC S hutdown Current T A =25 C, V S3 = VS5 = 0V, no loa d - 0.1 1 µA

o

I LDOIN LDOIN S uppl y Curren t T A = 2 5 C, VS3 = V S5 = 5V, no load - 1 10

I LDOIN STB LDOIN Standb y Curre nt o

T A = 2 5 C, VS3 = 0 V, V S5 = 5V, no load, - 0.1 10 µA

o

I LDOIN SDN LDOIN S hutdown Cu rrent T A = 2 5 C, VS3 = V S5 = 0V, no load - 0.1 1

POWER-ON-RESET

VCC P OR Thr eshold VCC Rising 3 .9 5 4.1 4.4 V

VCC P OR Hyste resis - 0.1 - V

VTT OUTP UT

VLD OIN = VVDD QSNS = 1.5V - 0.75 -

VVTT VTT O utp ut Voltage VLD OIN = VVDD QSNS = 1.35 V - 0.6 75 - V

VLD OIN = VVDD QSNS = 1.2V - 0.6 -

VLD OIN = VVDD QSNS = 1.5V , VVDDQSNS/2 - VVTT,

-20 - 20

IVTT = 0 A

VLD OIN = VVDD QSNS = 1.5V , VVDDQSNS/2 - VVTT,

-30 - 30

IVTT = 1 A

VVTT VTT O utp ut Tolera nce mV

VLD OIN = VVDD QSNS = 1.35 V, VVD DQSNS/2 - VVTT,

-20 - 20

IVTT = 0 A

VLD OIN = VVDD QSNS = 1.35 V, VVD DQSNS/2 - VVTT,

-30 - 30

IVTT = 1 A

Copyright ANPEC Electronics Corp. 4 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Electrical Characteristics

Refer to the typical application circuits. These specifications apply over V VCC=V BOOT=5V, V IN=12V and T A= -40 ~ 85oC, unless

otherwise specified. Typical values are at TA=25oC.

APW8 868C

Sym bol P aram eter Test Conditions Unit

Min Typ Max

VTT OUTP UT

VLDOIN = VVDD QSNS = 1.2V, VVDDQSNS/2 - V VTT,

-20 - 20

IVTT = 0A

VTT VTT O utput Tole rance mV

VLDOIN = VVDD QSNS = 1.2V, VVDDQSNS/2 - V VTT,

-30 - 30

IVTT = 1A

VSSVTT VTT S oft Start time S3 is g o h igh to 0 .9 5*VTT Regul atio n 25 30 35 us

Sourcin g Cu rrent o

T J=25 C 1.2 1.8 2.6

( VLDOIN=1.5 V)

A

Sinking Curre nt o

T J=25 C -1.3 -1 .8 -2 .6

( VLDOIN=1.5 V)

Sourcin g Cu rrent

T J=25 oC 1.1 1.8 2.6

( VLDOIN=1.3 5V)

I LIM Curren t-L imit

Sinking Curre nt o

T J=25 C -1.2 -1 .8 -2 .6

( VLDOIN=1.3 5V)

A

S ourcin g Cu rrent o

T J=25 C 1 1.8 2.6

( VLDOIN=1.2 V)

Sinking Curre nt

T J=25 oC -1.05 -1 .8 -2 .6

( VLDOIN=1.2 V)

Up per MOSFE T - 3 50 500

R DS(ON ) VTT Po we r MOSFETs R DS(ON) mΩ

Lower MOSFE T - 3 50 500

VVTT = 1.25V, VS3 = 0V, VS5 = 5V,

I VTTLK VTT Lea kage Curren t -1.0 - 1.0 µA

TA = 25 oC

I VTTSNSLK VTTS NS Leakag e Cu rrent VVTT = 1.25V, T A = 2 5oC -1.00 0.01 1 .00 µA

VTTRE F O UTPUT

VLDOIN = VVDD QSNS = 1.5V, VVDDQSNS/2 - 0.75 -

VVTTR EF VTTREF Ou tp ut Voltage VLDOIN = VVDD QSNS = 1.35V, VVD DQSNS/2 - 0 .6 75 - V

VLDOIN = VVDD QSNS = 1.2V, VVDDQSNS/2 - 0.6 -

-10mA < IVTTREF < 10mA, VVD DQSN S/2 - VVTTREF

-20 - 20

VLDOIN = VVTTR EF =1.5V

-10mA < IVTTREF < 10mA, VVD DQSN S/2 - VVTTREF

VTTREF Tolera nce -20 - 20 mV

VLDOIN = VVDD QSNS = 1.35V

-10mA < IVTTREF < 10mA, VVD DQSN S/2 - VVTTREF

-20 - 20

VLDOIN = VVDD QSNS = 1.2V

I VTTREF VTTREF So urce Cu rrent VVTTREF = 0V -10 -2 0 - 50 mA

I VTTREF VTTREF Sin k Curre nt VVTTREF = 1.5V 10 20 60 mA

Copyright ANPEC Electronics Corp. 5 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Electrical Characteristics

Refer to the typical application circuits. These specifications apply over V VCC=V BOOT=5V, V IN=12V and T A= -40 ~ 85oC, unless

otherwise specified. Typical values are at TA=25oC.

APW 8868 C

Sym bol Param eter Test Conditions Unit

Min Typ Max

VDDQ OUTPUT

o

TA = 2 5 C 0.745 0.75 0.757 V

o o

T A = - 40 C to 85 C 0 .7 425 0.75 0 .7 575 V

o

VVFB VFB Regula ti on Vo lta ge T A = 2 5 C,

-0.1 - +0.1 %

VVCC = 4 .5V to 5.5V, VIN = 3V to 2 8V

o

T A = 2 5 C,

-1 - +1 %

Load = 0 to 10A , VVC C = 4.5 V to 5.5V

VFB Input Cu rrent VVFB= 0.78V -0.1 - +0.1 µA

PWM CONTROLLE RS

F SW Ope rating Frequ ency Adju stabl e Fre quen cy 400 - 550 KHz

T SS Internal So ft Sta rt Time S5 is Hi gh to 0.9*VO UT Re gulation 0.77 1.1 1 .4 ms

PWM CONTROLLE RS

TO Fast on time VIN =1 9V, V VDDQ =1 .5V , R TON =620kΩ 175 2 05 235 ns

TOFF(MIN) Minimum off time - 3 00 - ns

T ON (MIN) Slo w on time 80 11 0 140 ns

Zero-Crossing Thresh old -9.5 0.5 10.5 mV

VDDQ PROTECTIONS

TA = 2 5 o C 9 10 11 µA

CS Pin Sink Curren t Tempera tur e Co efficient, ppm/

- 450 0 - o

On The Basis of 25 °C C

(VVCC – V CS) – (V PHASE – PGND),

OCP Comparator Offset -18 0 18 mV

VVCC – VC S = 6 0mV

VDDQ Curren t Limit S ettin g Ran ge VVCC -VCS 30 - 200 mV

VDDQ OVP Tr ip Thre sh old VVDD Q Risin g 120 1 25 130 %

VDDQ OVP Debo unce Delay VFB Rising, DV=1 0mV - 1.5 - µs

VDDQ UVP Trip Threshol d VVDD Q Falling 60 70 80 %

VDDQ UVP Deboun ce - 10 - µs

VLDO IN Dischar ge Current S3=S5=5V,V LDOIN=1.5V 150 3 00 - mA

PG OOD

PG OOD in fr om Lo we r ( PGOOD Goes High) 87 90 93 %

VPGOOD PG OOD Th reshold

PGOOD in from High er (PGOOD Goes Hi gh) 120 1 25 130 %

I PGOOD PG OOD Leakag e Cu rrent VPGOOD=5V - 0.1 1 .0 µA

PG OOD Sink Curren t VPGOOD=0.5V 2.5 7.5 - mA

PG OOD Debou nce Time - 63 - µs

TSSPOK PO K Soft Star t Time S5 is Hi gh to POK Ready 1.5 2 26 ms

Copyright ANPEC Electronics Corp. 6 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Electrical Characteristics

Refer to the typical application circuits. These specifications apply over V VCC=V BOOT=5V, V IN=12V and T A= -40 ~ 85oC, unless

otherwise specified. Typical values are at TA=25oC.

APW 8868 C

Sym bol Param eter Test Conditions Unit

Min Typ Max

GATE DRIVE RS

UGATE P ull-Up Resistan ce BO OT-UGATE=0.5V - 5 7 Ω

UGATE S ink Resistance UGATE-PHAS E=0.5 V - 1 2 .5 Ω

LGATE Pu ll -Up Resistance PV CC-L GATE=0.5V - 5 7 Ω

LGATE Sink Resistance LGATE-P GND=0.5V - 1 2 .5 Ω

UGATE to LGATE Dead time UGATE falli ng to LGATE rising , no loa d - 20 - ns

LGATE to UGATE Dead time LGATE falling to UGATE rising , no loa d - 20 - ns

BOO TS TRAP DIODE

o

Forward Voltage VVCC – VBOOT , I F = 1 0mA, T A = 25 C - 0.3 0 .5 V

o

Reve rse Leakag e VBOOT = 30V, VPHASE = 25V, VVC C=5V, T A = 25 C - - 0 .5 µA

LOG IC THRESHOLD

VIH S3, S5 High Thresho ld V oltage S3, S5 Risi ng 2 - - V

VIL S3, S5 Low Threshol d V oltage S3, S5 Falling - - 0 .8 V

o

I ILEAK Logi c Input Leakag e Cu rrent VS3 = VS5 = 5 V, T A =25 C -1 - 1 µA

THE RMAL SHUTDOWN

o

TSD Thermal Shutdown Te mperature T J Rising - 1 60 - C

o

Thermal Shutdown Hysteresis - 25 - C

Copyright ANPEC Electronics Corp. 7 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Typical Operating Characteristics

Supply Current In S0 VS Temperature Supply Current In S3 VS Temperature

250 200

225

175

200

Supply Current (uA)

Supply Current (uA)

150

175

150 125

125 100

100

75

75

50

50

25

25

0 0

-60 -40 -20 0 20 40 60 80 100 120 140 160 -60 -40 -20 0 20 40 60 80 100 120 140 160

o

Temperature( C) Temperature (oC)

Shutdown Current VS Temperature On-Time VS Temperature

1.6 240

235

1.4

230

Shutdown Current (uA)

1.2 225

On-Time (ns)

220

1.0

215

0.8 210

205

0.6

200

0.4 195

190

0.2

185

0 180

-60 -40 -20 0 20 40 60 80 100 120 140 160 -60 -40 -20 0 20 40 60 80 100 120 140 160

Temperature (oC) Temperature (oC)

Reference Voltage VS Temperature

755

754

Reference Voltage (mV)

753

752

751

750

749

748

747

746

745

-60 -40 -20 0 20 40 60 80 100 120 140 160

Temperature (oC)

Copyright ANPEC Electronics Corp. 8 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Operating Waveforms

Enable VCC – No Load Enable S3 – No Load

CH2 CH2

CH3

CH3

CH1

CH1

CH4 CH4

CH1:VCC-5V/div CH1:VS3-5V/div

CH2:VDDQ-1V/div CH2:VDDQ-1V/div

CH3:VTT-500mV/div CH3:VTT-500mV/div

CH4:IL-2A/div CH4:IL-10A/div

Time:5ms/div Time:50us/div

Disable S3/S5 – No Load OTP

CH2 CH1

CH3 CH2

CH1

CH4

CH3

CH1:VS3/S5-5V/div

CH1:VDDQ-1V/div

CH2:VDDQ-1V/div

CH2:VTT-500mV/div

CH3:VTT-500mV/div

CH3:IL-10A/div

CH4:IL-5A/div

Time:200ms/div

Time:1ms/div

Copyright ANPEC Electronics Corp. 9 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Operating Waveforms

UVP Normal Operaion

CH2 CH2

CH3

CH3 CH1

CH1

CH4 CH4

CH1:Phase-2V/div CH1:Phase-20V/div

CH2:VDDQ-1V/div CH2:VDDQ-1V/div

CH3:VTT-500mV/div CH3:VTT-500mV/div

CH4:IL-10A/div CH4:IL-5A/div

Time:20us/div Time:2us/div

OCP POK-Enable S3/S5

CH2

CH2

CH3 CH3

CH1

CH1

CH4

CH4

CH1:Phase-20V/div

CH2:VDDQ-1V/div CH1:POK-5V/div

CH3:VTT-500mV/div CH2:VDDQ-1V/div

CH4:IL-10A/div CH3:VTT-500mV/div

Time:100us/div CH4:VS3/S5-5V/div

Time:500us/div

Copyright ANPEC Electronics Corp. 10 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Operating Waveforms

Load Transient-Load=1.2A<-->12A

CH1

CH2

CH1:VDDQ-50mV/div

CH2:IL-5A/div

Time:50us/div

Copyright ANPEC Electronics Corp. 11 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Pin Description

NO. NAME FUNCTION

1 VTTGND Power ground output for the VTT LDO.

2 VTTSNS Voltage sense input for the VTT LDO. Connect to plus terminal of the VTT LDO output capacitor.

3 GND Signal Ground

4 VTTREF VTTREF buffered reference output.

VDDQ reference input for VTT and VTTREF. Power supply for the VTTREF. Discharge current sinking

5 VDDQSNS

terminal for VDDQ non-tracking discharge.

6 FB VDDQ output voltage setting pin.

7 S3 S3 signal input.

8 S5 S5 signal input.

This Pin is Allowed to Adjust The Switching Frequency. Connect a resistor RTON = 100KΩ ~ 1.2MΩ from

9 TON

TON pin to PHASE pin.

Power-good output pin. PGOOD is an open drain output used to Indicate the status of the output

10 PGOOD

voltage. When VDDQ output voltage is within the target range, it is in high state.

11, 12 VCC 5V power supply voltage input pin for both internal control circuitry and low-side MOSFET gate driver.

Over-current trip voltage setting input for RDS(ON) current sense scheme if connected to VCC through the

13 CS

voltage setting resistor.

Power ground of the LGATE low-side MOSFET driver. Connect the pin to the Source of the low-side

14 PGND

MOSFET.

Output of the low-side MOSFET driver for PWM. Connect this pin to Gate of the low-side MOSFET.

15 LGATE

Swings from PGND to VCC.

Junction point of the high-side MOSFET Source, output filter inductor and the low-side MOSFET Drain.

16 PHASE Connect this pin to the Source of the high-side MOSFET. PHASE serves as the lower supply rail for the

UGATE high-side gate driver.

17 UGATE Output of the high-side MOSFET driver for PWM. Connect this pin to Gate of the high-side MOSFET.

Supply Input for the UGATE Gate Driver and an internal level-shift circuit. Connect to an external

18 BOOT

capacitor and diode to create a boosted voltage suitable to drive a logic-level N-channel MOSFET.

19 LDOIN Supply voltage input for the VTT LDO.

20 VTT Power output for the VTT LDO.

Copyright ANPEC Electronics Corp. 12 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Block Diagram

0.5 x VDDQ

VDDQSNS

VTTREF

VLDOIN

Thermal

Shutdown

S3

S3,S5 Control Logic Current Limit

VTT

S5

0.5 x VDDQ +5/10%

VTTSNS

0.5 x VDDQ -5/10%

VTTGND

Tracking

Discharge

VCC

Soft

POR VCC

GND Start

VREF 1.25V

Current

Limit

CS

VREF

FB

10uA

125% x VREF

OV Error

Comparator BOOT

UGATE

UV

PWM

Signal

70% x VREF PHASE

TON Controller

TON

PHASE Generator

ZC VCC

LGATE

VREF x

PGOOD

125%/122%

PGND

Delay

VREF x 90%/87%

Copyright ANPEC Electronics Corp. 13 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Typical Application Circuit

CBOOT VIN

7V~25V

0.1uF CIN

Q1 10uF x 2

PHASE LOUT

VDDQ 1uH VDDQ

10A

VTT COUT

VDDQ/2 Q2 22uF x 4

(MLCC)

UGATE

VTT

CVTT

PHASE

BOOT

LDOIN

10uF x 2

VTTGND LGATE

VTTSNS PGND

APW8868C RCS

VCC

CS

RVCC

TQFN-20 5.1K, 1%

VTTREF VTTREF VCC

VDDQ/2 2.2

CVTTREF VDDQSNS CVCC

0.033uF 1uF CPVCC

PGOOD

4.7uF

TON

VFB

S5

S3

RPGOOD

PGOOD

100k

VDDQ RTON

RTOP VIN or PHASE

75K, 1% RGND 1.2M

75K, 1%

Copyright ANPEC Electronics Corp. 14 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Function Description

The APW8868C integrates a synchronous buck PWM con- Both in PFM and PWM, the on-time generator, which

troller to generate VDDQ, a sourcing and sinking LDO senses input voltage on PHASE pin, provides very fast

linear regulator to generate VTT. It provides a complete on-time response to input line transients.

power supply for DDR2 and DDR3/DDR3L memory sys- Another one-shot sets a minimum off-time (typical:

tem in a 20-pin TQFN package. User defined output volt- 300ns). The on-time one-shot is triggered if the error com-

age is also possible and can be adjustable from 0.75V to parator is high, the low-side switch current is below the

5.5V. Input voltage range of the PWM converter is 3V to current-limit threshold, and the minimum off-time one-

28V. The converter runs an adaptive on-time PWM opera- shot has timed out.

tion at high-load condition and automatically reduces fre- Power-On-Reset

quency to keep excellent efficiency down to several mA.

A Power-On-Reset (POR) function is designed to prevent

The VTT LDO can source and sink up to 1.5A peak cur-

wrong logic controls when the VCC voltage is low. The

rent with only 10µF ceramic output capacitor. VTTREF

POR function continually monitors the bias supply volt-

tracks VDDQ/2 within 1% of VDDQ. VTT output tracks

age on the VCC pin if at least one of the enable pins is set

VTTREF within 20 mV at no load condition while 40 mV at

high. When the rising VCC voltage reaches the rising

full load. The LDO input can be separated from VDDQ

POR voltage threshold (4.1V typical), the POR signal goes

and optionally connected to a lower voltage by using

high and the chip initiates soft-start operations. Should

VLDOIN pin. This helps reducing power dissipation in

this voltage drop lower than 4V (typical), the POR dis-

sourcing phase. The APW8868C is fully compatible to

ables the chip.

JEDEC DDR2 and DDR3/DDR3L specifications at S3/

S5 sleep state (see Table 1). When both VTT and VDDQ Soft- Start

are disabled, the non-tracking discharge mode dis- The APW8868C integrates digital soft-start circuits to

charges outputs using internal discharge MOSFETs that ramp up the output voltage of the converter to the pro-

are connected to VDDQSNS and VTT. grammed regulation set point at a predictable slew rate.

The slew rate of output voltage is internally controlled to

Constant-On-Time PWM Controller with Input Feed-For- limit the inrush current through the output capacitors dur-

ward

ing soft-start process. The figure 1 shows VDDQ soft-

The constant on-time control architecture is a pseudo- start sequence. When the S5 pin is pulled above the ris-

fixed frequency with input voltage feed-forward. This ar- ing S5 threshold voltage, the device initiates a soft-start

chitecture relies on the output filter capacitor’s effective process to ramp up the output voltage. The soft-start in-

series resistance (ESR) to act as a current-sense resistor, terval is 1.2ms (typical) and independent of the UGATE

so the output ripple voltage provides the PWM ramp signal. switching frequency.

In PFM operation, the high-side switch on-time controlled

by the on-time generator is determined solely by a one-

2ms

shot whose pulse width is inversely proportional to input

VCC and VPVCC

voltage and directly proportional to output voltage. In PWM

operation, the high-side switch on-time is determined by 1.2ms

VOUT

a switching frequency control circuit in the on-time gen-

erator block. The switching frequency control circuit

senses the switching frequency of the high-side switch S5

and keeps regulating it at a constant frequency in PWM

mode. The design improves the frequency variation and

be more outstanding than a conventional constant on-

time controller which has large switching frequency varia-

tion over input voltage, output current and temperature. VPGOOD

Fig1. Soft-Start Sequence

Copyright ANPEC Electronics Corp. 15 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Function Description (cont.)

Soft- Start (cont.) Over Voltage Protection (OVP)

During soft-start stage before the PGOOD pin is ready, The feedback voltage should increase over 125% of the

the under voltage protection is prohibited. The over volt- reference voltage due to the high-side MOSFET failure or

age and current limit protection functions are enabled. If for other reasons, and the over voltage protection com-

the output capacitor has residue voltage before startup, parator designed with a 1.5µs noise filter will force the

both low-side and high-side MOSFETs are in off-state low-side MOSFET gate driver to be high. This action ac-

until the internal digital soft start voltage equal the inter- tively pulls down the output voltage and eventually at-

nal feedback voltage. This will ensure the output voltage tempts to blow the battery fuse.

starts from its existing voltage level. When the OVP occurs, the PGOOD pin will pull down and

The VTT LDO part monitors the output current, both sourc- latch-off the converter. This OVP scheme only clamps the

ing and sinking current, and limits the maximum output voltage overshoot, and does not invert the output voltage

current to prevent damages during current overload or when otherwise activated with a continuously high output

short circuit (shorted from VTT to GND or VLDOIN) from low-side MOSFET driver. It’s a common problem for

conditions. OVP schemes with a latch. Once an over-voltage fault

The VTT LDO provides a soft-start function, using the condition is set, toggling VCC power-on-reset signal can

constant current to charge the output capacitor that gives only reset it.

a rapid and linear output voltage rise. If the load current is

above the current limit start-up, the VTT cannot start PWM Converter Current Limit

successfully. The current-limit circuit employs a unique “valley” current

APW8868C has an independent counter for each output, sensing algorithm (Figure 2). CS pin should be con-

but the PGOOD signal indicates only the status of VDDQ nected to VCC through the trip voltage-setting resistor,

and does not indicate VTT power good externally. RCS. CS terminal sinks 10uA current, ICS, and the current

limit threshold is set to the voltage across the RCS. The

Power-Good Output (PGOOD)

voltage between or CS_GND pin and PHASE pin moni-

PGOOD is an open-drain output and the PGOOD com-

parator continuously monitors the output voltage. PGOOD tors the inductor current so that PHASE pin should be

connected to the drain terminal of the low side MOSFET.

is actively held low in shutdown, and standby. When PWM

converter’s output voltage is greater than 95% of its tar- PGND is used as the positive current sensing node so

that PGND should be connected to the proper current

get value, the internal open-drain device will be pulled

low. After 63µs debounce time, the PGOOD goes high. sensing device, i.e. the sense resistor or the source ter-

minal of the low side MOSFET.

The PGOOD goes low if VVDDQ output is 10% below or

above its nominal regulation point. If the magnitude of the current-sense signal is above the

current-limit threshold, the PWM is not allowed to initiate

Under Voltage Protection a new cycle. The actual peak current is greater than the

In the process of operation, if a short-circuit occurs, the current-limit threshold by an amount equal to the induc-

output voltage will drop quickly. When load current is big- tor ripple current. Therefore, the exact current- limit char-

ger than current limit threshold value, the output voltage acteristic and maximum load capability are a function of

will fall out of the required regulation range. The under- the sense resistance, inductor value, and input voltage.

voltage continually monitors the setting output voltage The equation for the current limit threshold is as follows:

after 2ms of PWM operations to ensure startup. If a load

step is strong enough to pull the output voltage lower

RCS×10uA (VIN − VVDDQ) VVDDQ

than the under voltage threshold (70% of normal output ILIMIT = + ×

RDS(ON) 2 × L × fsw VIN

voltage), APW8868C shuts down the output gradually and

latches off both high and low side MOSFETs.

Copyright ANPEC Electronics Corp. 16 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Function Description (cont.)

PWM Converter Current Limit(cont.) S3, S5 Control

Where ILIMIT is the desired current limit threshold, RCS is

In the DDR2 and DDR3/DDR3L memory applications, it

the value of the current sense resistor connected to VCC

is important to keep VDDQ always higher than VTT/

and CS pin VCS is the voltage across the R CS resistor

VTTREF including both start-up and shutdown. The S3

IRIPPLE is inductor peak to peak current FSW is the PWM

and S5 signals control the VDDQ, VTT, VTTREF states

switching frequency.

and these pins should be connected to SLP_S3 and

In a current limit condition, the current to the load ex-

SLP_S5 signals respectively. The table1 shows the truth

ceeds the current to the output capacitor thus the output

table of the S3 and S5 pins. When both S3 and S5 are

voltage tends to fall down. If the output voltage becomes

above the logic threshold voltage, the VDDQ, VTT and

less than power good level, the VCS is cut into half and the

VTTREF are turned on at S0 state. When S3 is low and

output voltage tends to be even lower. Eventually, it

S5 is high, the VDDQ and VTTREF are kept on while the

crosses the under voltage protection threshold and

VTT voltage is disabled and left high impedance in S3

shutdown.

state. When both S3 and S5 are low, the VDDQ, VTT and

VTTREF are turned off and tracking discharge to the

IPEAK ground.

INDUCTOR CURRENT

Table1. The Truth Table of S3 and S5 pins.

STATE S3 S5 VDDQ VTTREF VTT

ILIMIT S0 H H 1 1 1

S3 L H 1 1 0 (high-Z)

IVALLEY

S4/5 L L 0 (discharge) 0 (discharge) 0 (discharge)

0 Time

Fig2. Current Limit Algorithm

VTT Sink/Source Regulator

The output voltage at VTT pin tracks the reference voltage

applied at VTTREF pin. Two internal N-channel MOSFETs

controlled by separate high bandwidth error amplifiers

regulate the output voltage by sourcing current from

VLDOIN pin or sinking current to GND pin. To prevent two

pass transistors from shoot-through, a small voltage off-

set is created between the positive inputs of the two error

amplifiers. The VTT with fast response feedback loop

keeps tracking to the VTTREF within +40 mV at all condi-

tions including fast load transient.

Copyright ANPEC Electronics Corp. 17 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Function Description (cont.)

Thermal Shutdown

A thermal shutdown circuit limits the junction tempera-

ture of APW8868C. When the junction temperature ex-

ceeds +160oC, PWM converter, VTTLDO and VTTREF are

shut off, allowing the device to cool down. The regulator

regulates the output again through initiation of a new soft-

start cycle after the junction temperature cools by 25oC,

resulting in a pulsed output during continuous thermal

overload conditions. The thermal shutdown designed with

a 25oC hysteresis lowers the average junction tempera-

ture during continuous thermal overload conditions, ex-

tending life time of the device. For normal operation, de-

vice power dissipation should be externally limited so

that junction temperatures will not exceed +125oC.

Programming the On-Time Control and PWM Switch-

ing Frequency

The APW8868C does not use a clock signal to produce

PWM. The device uses the constant on-time control ar-

chitecture to produce pseudo-fixed frequency with input

voltage feed-forward. The on-time pulse width is propor-

tional to output voltage VOUT and inverse proportional to

input voltage VIN. In PWM, the on-time calculation is writ-

ten as below equation.

2 × VVDDQ

TON = 6.3 × 10 −12 × R TON × 3

VIN

Where:

RTON is the resistor connected from TON pin to PHASE

pin. Furthermore, The approximate PWM switching fre-

quency is written as:

D VOUT / VIN

TON = = FSW =

FSW TON

Where:

FSW is the PWM switching frequency

APW8868C doesn’t have VIN pin to calculate on-time

pulse width. Therefore, monitoring VPHASE voltage as in-

put voltage to calculate on-time when the high-side

MOSFET is turned on. And then, use the relationship be-

tween on-time and duty cycle to obtain the switching

frequency.

Copyright ANPEC Electronics Corp. 18 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Application Information (cont.)

Output Voltage Selection In some types of inductors, especially core that is made

PWM can be also adjusted from 0.75V to 5.5V with a of ferrite, the ripple current will increase abruptly when it

resistor-driver at FB between VDDQSNS and GND. Us- saturates. This will be result in a larger output ripple

ing 1% or better resistors for the resistive divider is voltage.

recommended. The FB pin is the inverter input of the

error amplifier, and the reference voltage is 0.75V. Take Output Capacitor Selection

the example, the output voltage of PWM is determined by: Output voltage ripple and the transient voltage deviation

are factors that have to be taken into consideration when

R selecting an output capacitor. Higher capacitor value and

V OUT = 0.75 × 1 + TOP

R GND lower ESR reduce the output ripple and the load tran-

sient drop. Therefore, selecting high performance low

Where RTOP is the resistor connected from VOUT to FB and

ESR capacitors is intended for switching regulator

RGND is the resistor connected from FB to GND.

applications. In addition to high frequency noise related

Output Inductor Selection MOSFET turn-on and turn-off, the output voltage ripple

includes the capacitance voltage drop and ESR voltage

The duty cycle of a buck converter is the function of the

drop caused by the AC peak-to-peak current. These two

input voltage and output voltage. Once an output voltage

voltages can be represented by:

is fixed, it can be written as:

IRIPPLE

VOUT ∆VCOUT =

D= 8C OUT FSW

VIN

The inductor value determines the inductor ripple current

∆VESR = IRIPPLE × RESR

and affects the load transient response. Higher inductor

value reduces the inductor’s ripple current and induces

These two components constitute a large portion of the

lower output ripple voltage. The ripple current and ripple

voltage can be approximated by: total output voltage ripple. In some applications, multiple

capacitors have to be paralleled to achieve the desired

VIN − VOUT VOUT ESR value. If the output of the converter has to support

IRIPPLE = ×

FSW × L VIN another load with high pulsating current, more capaci-

Where FSW is the switching frequency of the regulator. tors are needed in order to reduce the equivalent ESR

Although increase the inductor value and frequency re- and suppress the voltage ripple to a tolerable level. A

duce the ripple current and voltage, there is a tradeoff small decoupling capacitor in parallel for bypassing the

between the inductor’s ripple current and the regulator noise is also recommended, and the voltage rating of the

load transient response time. output capacitors must also be considered.

A smaller inductor will give the regulator a faster load To support a load transient that is faster than the switch-

transient response at the expense of higher ripple current. ing frequency, more capacitors have to be used to re-

Increasing the switching frequency (FSW ) also reduces duce the voltage excursion during load step change. An-

the ripple current and voltage, but it will increase the other aspect of the capacitor selection is that the total AC

switching loss of the MOSFETs and the power dissipa- current going through the capacitors has to be less than

tion of the converter. The maximum ripple current occurs the rated RMS current specified on the capacitors to pre-

at the maximum input voltage. A good starting point is to vent the capacitor from over-heating.

choose the ripple current to be approximately 30% of the

maximum output current. Once the inductance value has

been chosen, selecting an inductor is capable of carrying

the required peak current without going into saturation.

Copyright ANPEC Electronics Corp. 19 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Application Information (cont.)

Input Capacitor Selection Phigh-side = IOUT2(1+TC)(RDS(ON))D+(0.5)(IOUT)(VIN)(tSW )FSW

The input capacitor is chosen based on the voltage rat-

ing and the RMS current rating. For reliable operation, Plow-side = IOUT2(1+TC)(RDS(ON))D(1-D)

select the capacitor voltage rating to be at least 1.3 times

higher than the maximum input voltage. The maximum Where

RMS current rating requirement is approximately IOUT/2, I is the load current

where IOUT is the load current. During power up, the input TC is the temperature dependency of RDS(ON)

capacitors have to handle large amount of surge current. FSW is the switching frequency

In low-duty notebook applications, ceramic capacitors are tSW is the switching interval

recommended. The capacitors must be connected be- D is the duty cycle

tween the drain of high-side MOSFET and the source of

Note that both MOSFETs have conduction losses while

low-side MOSFET with very low-impedance PCB layout.

the high-side MOSFET includes an additional transition

MOSFET Selection loss. The switching internal, t SW , is the function of the

The application for a notebook battery with a maximum reverse transfer capacitance CRSS. The (1+TC) term is to

voltage of 24V, at least a minimum 30V MOSFETs should factor in the temperature dependency of the RDS(ON) and

be used. The design has to trade off the gate charge with can be extracted from the “RDS(ON) vs Temperature” curve

the RDS(ON) of the MOSFET: of the power MOSFET.

- For the low-side MOSFET, before it is turned on, the

body diode has been conducted. The low-side MOSFET Layout Consideration

driver will not charge the miller capacitor of this MOSFET. In any high switching frequency converter, a correct lay-

- In the turning off process of the low-side MOSFET, the out is important to ensure proper operation of the

load current will shift to the body diode first. The high dv/ regulator. W ith power devices switching at higher

dt of the phase node voltage will charge the miller ca- frequency, the resulting current transient will cause volt-

pacitor through the low-side MOSFET driver sinking cur- age spike across the interconnecting impedance and

rent path. This results in much less switching loss of the parasitic circuit elements. As an example, consider the

low-side MOSFETs. The duty cycle is often very small in turn-off transition of the PWM MOSFET. Before turn-off

high battery voltage applications, and the low-side condition, the MOSFET is carrying the full load current.

MOSFET will conduct most of the switching cycle; During turn-off, current stops flowing in the MOSFET and

therefore, the RDS(ON) of the low-side MOSFET, the less is freewheeling by the lower MOSFET and parasitic diode.

the power loss. The gate charge for this MOSFET is usu- Any parasitic inductance of the circuit generates a large

ally a secondary consideration. The high-side MOSFET voltage spike during the switching interval. In general,

does not have this zero voltage switching condition, and using short and wide printed circuit traces should mini-

because it conducts for less time compared to the low- mize interconnecting impedances and the magnitude of

side MOSFET, the switching loss tends to be dominant. voltage spike. And signal and power grounds are to be

Priority should be given to the MOSFETs with less gate kept separating and finally combined to use the ground

charge, so that both the gate driver loss and switching plane construction or single point grounding. The best

loss will be minimized. tie-point between the signal ground and the power ground

The selection of the N-channel power MOSFETs are de- is at the negative side of the output capacitor on each

termined by the RDS(ON), reversing transfer capacitance channel, where there is less noise. Noisy traces beneath

(CRSS) and maximum output current requirement. The the IC are not recommended. Below is a checklist for

losses in the MOSFETs have two components: conduc- your layout:

tion loss and transition loss. For the high-side and low-

side MOSFETs, the losses are approximately given by

the following equations:

Copyright ANPEC Electronics Corp. 20 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Application Information (cont.)

Layout Consideration 3mm

- Keep the switching nodes (UGATE, LGATE, BOOT, and

PHASE) away from sensitive small signal nodes(VFB,

VTTREF, and CS) since these nodes are fast moving

signals. Therefore, keep traces to these nodes as short 0.5mm *

as possible and there should be no other weak signal 0.2mm

traces in parallel with theses traces on any layer.

1.66 mm

- The signals going through theses traces have both high

dv/dt and high di/dt, with high peak charging and dis- 3mm

charging current. The traces from the gate drivers to the 0.4mm

MOSFETs (UGATE and LGATE) should be short and wide. 1.66 mm

- Place the source of the high-side MOSFET and the drain 0.17mm

0.5mm

of the low-side MOSFET as close as possible. Minimiz-

ing the impedance with wide layout plane between the

two pads reduces the voltage bounce of the node.

* Just Recommend

- Decoupling capacitor, the resistor dividers, boot TQFN3x3-20

capacitors, and current limit stetting resistor should be

close their pins. (For example, place the decoupling ce- Figure3. Recommended Minimum Footprint

ramic capacitor near the drain of the high-side MOSFET

as close as possible. The bulk capacitors are also placed

near the drain).

- The input capacitor should be near the drain of the up-

per MOSFET; the high quality ceramic decoupling capaci-

tor can be put close to the VCC and GND pins; the VTTREF

decoupling capacitor should be close to the VTTREF pin

and GND; the VDDQ and VTT output capacitors should

be located right across their output pin as close as pos-

sible to the part to minimize parasitic. The input capacitor

GND should be close to the output capacitor GND and

the lower MOSFET GND.

- The drain of the MOSFETs (VIN and PHASE nodes)

should be a large plane for heat sinking. And PHASE pin

traces are also the return path for UGATE. Connect this

pin to the converter’s upper MOSFET source.

- The APW8868C used ripple mode control. Build the

resistor divider close to the VFB pin so that the high im-

pedance trace is shorter. And the VFB pin traces can’t be

closed to the switching signal traces (UGATE, LGATE,

BOOT, and PHASE).

- The PGND trace should be a separate trace, and inde-

pendently go to the source of the low-side MOSFETs for

current limit accuracy.

Copyright ANPEC Electronics Corp. 21 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Package Information

TQFN3x3-20

D A

b

E

Pin 1

A1

A3

D2 NX

aaa C

Pin 1 Corner

E2

K

L

S TQFN3x3-20

Y

M MILLIMETERS INCHES

B

O

L MIN. MAX. MIN. MAX.

A 0.70 0.80 0.028 0.031

A1 0.00 0.05 0.000 0.002

A3 0.20 REF 0.008 REF

b 0.15 0.25 0.006 0.010

D 2.90 3.10 0.114 0.122

D2 1.50 1.80 0.059 0.071

E 2.90 3.10 0.114 0.122

E2 1.50 1.80 0.059 0.071

e 0.40 BSC 0.016 BSC

L 0.30 0.50 0.012 0.020

K 0.20 0.008

aaa 0.08 0.003

Note : 1. Followed from JEDEC MO-220 WEEE

Copyright ANPEC Electronics Corp. 22 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Carrier Tape & Reel Dimensions

OD0 P0 P2 P1 A

E1

F

W

B0

K0 A0 A

OD1 B

B

SECTION A-A

T

SECTION B-B

d

H

A

T1

Application A H T1 C d D W E1 F

12.4+2.00 13.0+0.50

330±2.00 50 MIN. 1.5 MIN. 20.2 MIN. 12.0±0.30 1.75±0.10 5.5±0.05

-0.00 -0.20

TQFN3x3-20 P0 P1 P2 D0 D1 T A0 B0 K0

1.5+0.10 0.6+0.00

4.0±0.10 8.0±0.10 2.0±0.05 1.5 MIN. 3.30±0.20 3.30±0.20 1.00±0.20

-0.00 -0.40

(mm)

Devices Per Unit

Package Type Unit Quantity

TQFN3x3-20 Tape & Reel 3000

Copyright ANPEC Electronics Corp. 23 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Taping Direction Information

TQFN3x3-20

USER DIRECTION OF FEED

Classification Profile

Copyright ANPEC Electronics Corp. 24 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Classification Reflow Profiles

Profile Feature Sn-Pb Eutectic Assembly Pb-Free Assembly

Preheat & Soak

100 °C 150 °C

Temperature min (Tsmin)

150 °C 200 °C

Temperature max (Tsmax)

60-120 seconds 60-120 seconds

Time (Tsmin to Tsmax) (ts)

Average ramp-up rate

3 °C/second max. 3°C/second max.

(Tsmax to TP)

Liquidous temperature (TL) 183 °C 217 °C

Time at liquidous (tL) 60-150 seconds 60-150 seconds

Peak package body Temperature

See Classification Temp in table 1 See Classification Temp in table 2

(Tp)*

Time (tP)** within 5°C of the specified

20** seconds 30** seconds

classification temperature (Tc)

Average ramp-down rate (Tp to Tsmax) 6 °C/second max. 6 °C/second max.

Time 25°C to peak temperature 6 minutes max. 8 minutes max.

* Tolerance for peak profile Temperature (Tp) is defined as a supplier minimum and a user maximum.

** Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

3 3

Package Volume mm Volume mm

Thickness <350 ≥350

<2.5 mm 235 °C 220 °C

≥2.5 mm 220 °C 220 °C

Table 2. Pb-free Process – Classification Temperatures (Tc)

3 3 3

Package Volume mm Volume mm Volume mm

Thickness <350 350-2000 >2000

<1.6 mm 260 °C 260 °C 260 °C

1.6 mm – 2.5 mm 260 °C 250 °C 245 °C

≥2.5 mm 250 °C 245 °C 245 °C

Reliability Test Program

Test item Method Description

SOLDERABILITY JESD-22, B102 5 Sec, 245°C

HOLT JESD-22, A108 1000 Hrs, Bias @ Tj=125°C

PCT JESD-22, A102 168 Hrs, 100%RH, 2atm, 121°C

TCT JESD-22, A104 500 Cycles, -65°C~150°C

HBM MIL-STD-883-3015.7 VHBM≧2KV

MM JESD-22, A115 VMM≧200V

Latch-Up JESD 78 10ms, 1tr≧100mA

Copyright ANPEC Electronics Corp. 25 www.anpec.com.tw

Rev. A.3 - Feb., 2019

APW8868C

Customer Service

Anpec Electronics Corp.

Head Office :

No.6, Dusing 1st Road, SBIP,

Hsin-Chu, Taiwan, R.O.C.

Tel : 886-3-5642000

Fax : 886-3-5642050

Taipei Branch :

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd.,

Sindian City, Taipei County 23146, Taiwan

Tel : 886-2-2910-3838

Fax : 886-2-2917-3838

Copyright ANPEC Electronics Corp. 26 www.anpec.com.tw

Rev. A.3 - Feb., 2019

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Sinopower Semicon APW8868BQBI TRG - C2842165Document26 pagesSinopower Semicon APW8868BQBI TRG - C2842165Artuf3No ratings yet

- As15 FDocument28 pagesAs15 FHamza Abbasi AbbasiNo ratings yet

- APW8823Document28 pagesAPW8823mariusz sNo ratings yet

- APW8813/A: Features General DescriptionDocument31 pagesAPW8813/A: Features General DescriptionDanielle ButlerNo ratings yet

- OB2362 DatasheetDocument10 pagesOB2362 DatasheetTín SmpsNo ratings yet

- APW8720BDocument22 pagesAPW8720BAlbertNo ratings yet

- APX9131A: Features General DescriptionDocument12 pagesAPX9131A: Features General DescriptionChek OmarovNo ratings yet

- General Description Features: High Performance Current Mode PWM ControllerDocument11 pagesGeneral Description Features: High Performance Current Mode PWM ControllerPhạm Tấn HảiNo ratings yet

- Power Management Ic For Li-Ion Powered Systems: Features DescriptionDocument45 pagesPower Management Ic For Li-Ion Powered Systems: Features DescriptionErmand WindNo ratings yet

- Power Management Ic For Li-Ion Powered Systems: Features DescriptionDocument45 pagesPower Management Ic For Li-Ion Powered Systems: Features DescriptionErmand WindNo ratings yet

- Features General Description: Dual-Phase Synchronous-Rectifier Buck ControllerDocument26 pagesFeatures General Description: Dual-Phase Synchronous-Rectifier Buck ControllerVịnh DemoNo ratings yet

- Multi-Phase PWM Controller For CPU Core Power Supply: Features General DescriptionDocument24 pagesMulti-Phase PWM Controller For CPU Core Power Supply: Features General Descriptionakhmad mukhsinNo ratings yet

- TS13401M Neo-Iso™ Solid State Relay Driver With Sensing and Power Transfer High-Reliability ProductsDocument19 pagesTS13401M Neo-Iso™ Solid State Relay Driver With Sensing and Power Transfer High-Reliability ProductsSero StivNo ratings yet

- Features General Description: Hall Effect Micro Switch ICDocument14 pagesFeatures General Description: Hall Effect Micro Switch IChigocNo ratings yet

- Features General Description: Two-Phase Buck PWM Controller With Integrated MOSFET DriversDocument26 pagesFeatures General Description: Two-Phase Buck PWM Controller With Integrated MOSFET DriversMoisesNo ratings yet

- APW7068Document23 pagesAPW7068Fərid SirafilzadəNo ratings yet

- APW8715A: Features General DescriptionDocument26 pagesAPW8715A: Features General Descriptionmben osbiNo ratings yet

- HCPL 7601 AvagoDocument13 pagesHCPL 7601 AvagoSyed Khawar MukhtarNo ratings yet

- Integrated High Power PoE-PD Interface & DC-DC Converter ControllerDocument18 pagesIntegrated High Power PoE-PD Interface & DC-DC Converter ControllerArun PadmanabhanNo ratings yet

- A4960 A Automotive DatasheetDocument34 pagesA4960 A Automotive DatasheetCanerNo ratings yet

- Datasheet PDFDocument16 pagesDatasheet PDFRaul LeonNo ratings yet

- Tps 56 C 230Document30 pagesTps 56 C 230maxibettNo ratings yet

- RT8577ADocument18 pagesRT8577ASamuel SamTechNo ratings yet

- And Automotive 3-Phase BLDC Controller and MOSFET Driver: Description Features and BenefitsDocument21 pagesAnd Automotive 3-Phase BLDC Controller and MOSFET Driver: Description Features and BenefitsCanerNo ratings yet

- APW7073A: Features General DescriptionDocument20 pagesAPW7073A: Features General DescriptionyanjunNo ratings yet

- SC 2595Document12 pagesSC 2595Stelian DobreNo ratings yet

- tps54239 ReguladorDocument24 pagestps54239 ReguladorAntonioPierreNo ratings yet

- Apw7705 PDFDocument54 pagesApw7705 PDFLin CokeNo ratings yet

- 3930Document21 pages3930Rodrigo BronzeriNo ratings yet

- Sensorless BLDC Controller A4960: Description Features and BenefitsDocument34 pagesSensorless BLDC Controller A4960: Description Features and BenefitsadilNo ratings yet

- Max 14866Document23 pagesMax 14866hibluedeerNo ratings yet

- 4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Document23 pages4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™temarioNo ratings yet

- 4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Document21 pages4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Egor FedorenkoNo ratings yet

- Power Management Ics For Handheld Device: General Description FeaturesDocument33 pagesPower Management Ics For Handheld Device: General Description FeaturesHakim BenmajidNo ratings yet

- Nithya Electronics Tiruchendur 2A 1.4M 5.5V Synchronous Buck ConverterDocument6 pagesNithya Electronics Tiruchendur 2A 1.4M 5.5V Synchronous Buck ConverterSonu KumarNo ratings yet

- Ob 2223 HCDocument11 pagesOb 2223 HCRivaldyNo ratings yet

- Charge Pump DC-to-DC Voltage Converter: Features Package TypesDocument20 pagesCharge Pump DC-to-DC Voltage Converter: Features Package TypesTomás CuetoNo ratings yet

- Features General Description: High Input Voltage 6A PWM Converter With Adj. Soft StartDocument20 pagesFeatures General Description: High Input Voltage 6A PWM Converter With Adj. Soft StartLeonardo DiegoNo ratings yet

- Tps 54140Document52 pagesTps 54140niceautomation8831No ratings yet

- OB2530P On BrightElectronicsDocument10 pagesOB2530P On BrightElectronicsrrNo ratings yet

- Apl5916 AnpecDocument20 pagesApl5916 Anpecايهاب فوزيNo ratings yet

- RT8870ADocument12 pagesRT8870AFrastyan FazzaNo ratings yet

- OB2273A On BrightDocument10 pagesOB2273A On BrightHamza Abbasi AbbasiNo ratings yet

- Carlo - Gavazzi RGC2P60V75C1DFM Datasheet PDFDocument29 pagesCarlo - Gavazzi RGC2P60V75C1DFM Datasheet PDFmikeNo ratings yet

- Datasheet - HK hcpl-2731 92412Document13 pagesDatasheet - HK hcpl-2731 92412Anonymous aP1FSUPoNo ratings yet

- A4407 DatasheetDocument29 pagesA4407 DatasheetJairo PadronNo ratings yet

- Controlador CAN MC33389Document49 pagesControlador CAN MC33389Jorge Martinez PerezNo ratings yet

- NCP45790 D-2317241Document13 pagesNCP45790 D-2317241SuBaRu GTNo ratings yet

- NCP 1251Document22 pagesNCP 1251Cintya Cardozo100% (1)

- Tja1040t PDFDocument18 pagesTja1040t PDF81968No ratings yet

- Str-A6251M: Universal-Input/15 W 67 KHZ Flyback Switching RegulatorDocument7 pagesStr-A6251M: Universal-Input/15 W 67 KHZ Flyback Switching RegulatorAlexisNo ratings yet

- HOJA DE DATOS ncp1083Document17 pagesHOJA DE DATOS ncp1083Diego Javier Ramirez PerezNo ratings yet

- LCDM Inverter Controller: FeaturesDocument11 pagesLCDM Inverter Controller: FeaturesReneNo ratings yet

- Features General Description: 3A, 12V, Synchronous-Rectified Buck ConverterDocument21 pagesFeatures General Description: 3A, 12V, Synchronous-Rectified Buck ConverterVeronica GonzalezNo ratings yet

- REN Isl6308 DST 20080807Document28 pagesREN Isl6308 DST 20080807DiegoTavaresNo ratings yet

- Str-x6759n Ds enDocument9 pagesStr-x6759n Ds enCleiton SilvaNo ratings yet

- A4950 DatasheetDocument9 pagesA4950 DatasheetIndra KurniawanNo ratings yet

- Atom z540 z530 z520 z510 z500 45 NM Technology Datasheet PDFDocument73 pagesAtom z540 z530 z520 z510 z500 45 NM Technology Datasheet PDFFelix BlancoNo ratings yet

- Datasheet 7184Document24 pagesDatasheet 7184Alexandre HolandaNo ratings yet

- Asus Laptop Schematic DiagramDocument56 pagesAsus Laptop Schematic Diagramlisycat100% (1)

- Alc269 Datasheet 1 5-A5b89Document79 pagesAlc269 Datasheet 1 5-A5b89Billes GatesNo ratings yet

- Milwaukee 10M: Premp BuildDocument53 pagesMilwaukee 10M: Premp BuildFelix BlancoNo ratings yet

- 63dd2 - Samsung NP-RV420-NP-RV520-NP-RV720 Scala2 - R BA41-01609A BA41-01608A BA41-01610A Rev 0 1 SchematicsDocument48 pages63dd2 - Samsung NP-RV420-NP-RV520-NP-RV720 Scala2 - R BA41-01609A BA41-01608A BA41-01610A Rev 0 1 SchematicsRajesh Ks100% (1)

- Lenovo G40-70 - G50-70 - ACLU1-ACLU2 ACLU3 ACLU4 NM-A361 NM2710 NM-A271 Rev1.0 PDFDocument59 pagesLenovo G40-70 - G50-70 - ACLU1-ACLU2 ACLU3 ACLU4 NM-A361 NM2710 NM-A271 Rev1.0 PDFflavio_b_703950% (4)

- Havells General Purpose SwitchgearDocument4 pagesHavells General Purpose Switchgearadvance electricalNo ratings yet

- 2-1 EDC Lab Manual Jntuk R20 - 201021Document96 pages2-1 EDC Lab Manual Jntuk R20 - 201021Durgasaiteja923 SunnyNo ratings yet

- Se Data Logger Installation Guide NaDocument67 pagesSe Data Logger Installation Guide NaapocalipcNo ratings yet

- CBD 72.5-550 KV Centre-Break Disconnector: Costruzioni Elettromeccaniche - SpaDocument4 pagesCBD 72.5-550 KV Centre-Break Disconnector: Costruzioni Elettromeccaniche - SpaKelly chatNo ratings yet

- Remote I/O IS1 CPU and Power Module For Zone 2 9440/15-01-11-C1243 Art. No. 162201Document6 pagesRemote I/O IS1 CPU and Power Module For Zone 2 9440/15-01-11-C1243 Art. No. 162201Hugo HurtadoNo ratings yet

- Learning Insight: 10 Rules For Workplace SafetyDocument6 pagesLearning Insight: 10 Rules For Workplace SafetyIV-BTVTED GROUP 3No ratings yet

- Manual ANSUL Inergen 200barDocument121 pagesManual ANSUL Inergen 200barAldi SubagioNo ratings yet

- HCU option board installation guideDocument16 pagesHCU option board installation guideThái NgọcNo ratings yet

- Ece Practice Book PDFDocument16 pagesEce Practice Book PDFs_subbulakshmi0% (1)

- Service Manual: HCD-LX9AV/LX10AV/LX90AVDocument82 pagesService Manual: HCD-LX9AV/LX10AV/LX90AVJohan AponteNo ratings yet

- KSTAR PV Inverters CatalogueDocument29 pagesKSTAR PV Inverters CatalogueBernardoNo ratings yet

- July Car Sales ReportDocument1 pageJuly Car Sales ReportBima Trisnu Ardinal D'brandonizerNo ratings yet

- Rapid Milk Cooling Without Diesel Generator Backup: Feature BenefitsDocument2 pagesRapid Milk Cooling Without Diesel Generator Backup: Feature Benefitsibson045001256No ratings yet

- Latha Mathavan Engineering College EEE Ist Internal Exam ResultsDocument3 pagesLatha Mathavan Engineering College EEE Ist Internal Exam Resultspriya dharshiniNo ratings yet

- Service Manual Level &2: NokiaDocument27 pagesService Manual Level &2: NokiaPako PikoNo ratings yet

- Interfacing 7 Segment Display and LCDDocument35 pagesInterfacing 7 Segment Display and LCDYupniatsNo ratings yet

- DWDM Assignment 2Document8 pagesDWDM Assignment 2Amber MishraNo ratings yet

- WEG WMO Brake Motor Instruction Manual For Installation Operation Maintenance of Brake Motors 50021973 Brochure English WebDocument2 pagesWEG WMO Brake Motor Instruction Manual For Installation Operation Maintenance of Brake Motors 50021973 Brochure English WebMiguel LunaNo ratings yet

- VSXD 412 KDocument82 pagesVSXD 412 KJucaNo ratings yet

- Process Flow Chart - Smart MeterDocument4 pagesProcess Flow Chart - Smart MeterQAD LotusNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- DefibrillatorDocument85 pagesDefibrillatorDhruv DesaiNo ratings yet

- Cummins Data Sheet C550D5Document3 pagesCummins Data Sheet C550D5fahad pirzadaNo ratings yet

- Electric Motor Usage in VehiclesDocument27 pagesElectric Motor Usage in VehiclesKadir YavuzNo ratings yet

- Data Sheet: HCPL-3120/J312 HCNW3120Document26 pagesData Sheet: HCPL-3120/J312 HCNW3120Nae CarNo ratings yet

- PO 128 Manual - OriginalDocument2 pagesPO 128 Manual - Originaldalloner2No ratings yet

- Comissioning ProcedureDocument7 pagesComissioning Procedurekarim karimNo ratings yet

- UG CxxAcc Smart LiIon Power en Rev01 ScreenDocument24 pagesUG CxxAcc Smart LiIon Power en Rev01 ScreenAntonio Augusto Silva AlvesNo ratings yet

- Exercise 8.3Document28 pagesExercise 8.3aagi23No ratings yet

- QUIZ# 1-ResultDocument7 pagesQUIZ# 1-ResultAyhan AbdulAzizNo ratings yet