Professional Documents

Culture Documents

Reg. No.: Psna College of Engineering and Technology, Dindigul-624622 Department of Ece

Uploaded by

shasi0 ratings0% found this document useful (0 votes)

30 views1 pageOriginal Title

LPVLSI Test1

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

30 views1 pageReg. No.: Psna College of Engineering and Technology, Dindigul-624622 Department of Ece

Uploaded by

shasiCopyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 1

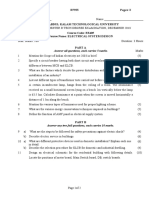

Reg.

No. PSNA COLLEGE OF ENGINEERING AND TECHNOLOGY, DINDIGUL-624622

DEPARTMENT OF ECE

Series Test-I

Subject : LOW POWER VLSI DESIGN Max. Marks :50

Sub Code : VL5202 Year : I Sem: II Duration : 90 Min.

Staff : Dr.M.Revathy Date :

Course Outcome Covered Part A Part B Part C

CO.1 To identify sources of power in an 1,2,3,4,5,6,7 10(a), 10(b), 12(a)

IC. 11(a)

CO.2 To identify the power reduction 8,9 11(b) 12(b)

techniques based on technology

independent and technology

dependent.

PART – A (Answer all) (9 x 2 = 18)

1. What is body effect?

2. Realise a full adder using half adders.

3. Give the need for low power VLSI chips.

4. Comment on the impact of scaling devices in low power design.

5. Name some multiple Vth techniques.

6. What are the sources of power consumption?

7. Realise a XOR gate using pass transistor logic.

8. What does architecture level power estimation approach require?

9. Mention the different types of adders used in low power design.

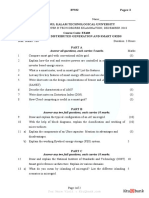

PART- B (Answer all) (2 x 10= 20)

10. (a) Describe the sources of static and dynamic power dissipation in CMOS circuits. (10)

(OR)

(b) Elaborate the Circuit techniques for leakage power reduction. (10)

11. (a) Discuss the basic principles behind low power VLSI design . (10)

(OR)

(b) Explain the various logic level power optimization techniques for low power design. (10)

PART- C (Answer all) (1 x 12= 12)

12. (a) With the help of energy band diagram analyze the physics of power dissipation in MOSFETs

by deriving expression for space charge region and threshold voltage. (12)

(OR)

12. (b) Explain the various CMOS Adders architectures. (12)

Faculty HOD-ECE

You might also like

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsContent for all CreatorNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Karthiga MuruganNo ratings yet

- Low Power Vlsi Question PaperDocument2 pagesLow Power Vlsi Question Paperustadkrishna100% (3)

- M.Tech I Semester Supplementary Examinations February/March 2018Document1 pageM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- DLC Model IDocument2 pagesDLC Model IEEE DEPTNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- LPVD 19-20 Mid SemDocument1 pageLPVD 19-20 Mid Semajay vermaNo ratings yet

- HVDC Previous Paper-R16Document2 pagesHVDC Previous Paper-R16swarna100% (1)

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- I A) B) 2 A) B) If 3 A) B) C) : Unitvnnsifv''.. Examination (R&S)Document2 pagesI A) B) 2 A) B) If 3 A) B) C) : Unitvnnsifv''.. Examination (R&S)Adithyan JNo ratings yet

- Ec7001 Adhoc and Wireless Sensor NetworksDocument2 pagesEc7001 Adhoc and Wireless Sensor NetworksninbrocknitinNo ratings yet

- Question Paper Code:: ElectiveDocument2 pagesQuestion Paper Code:: ElectiveShanmugapriya AnandanNo ratings yet

- Basic Eln-2021-IA-1-Set 2 - ModifiedDocument2 pagesBasic Eln-2021-IA-1-Set 2 - ModifiedProf. Nikhil KulkarniNo ratings yet

- L-4ff-l/EEE Date: 06/07/2013Document42 pagesL-4ff-l/EEE Date: 06/07/2013HolloGramNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- 16BT70408 - Low Power Cmos Vlsi DesignDocument1 page16BT70408 - Low Power Cmos Vlsi DesignS KkNo ratings yet

- C H1074 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesC H1074 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDeepak KumarNo ratings yet

- Question Paper CodeDocument2 pagesQuestion Paper CodeDinesh SrinivasanNo ratings yet

- Ex05 - Question Paper Ada Te-1Document2 pagesEx05 - Question Paper Ada Te-1shankarNo ratings yet

- FEE Model 1Document2 pagesFEE Model 1amangamingofficial2020No ratings yet

- Time: 3 Hours Total Marks: 100: Printed Pages: 02 Sub Code:NEC703 Paper Id: 130718 Roll NoDocument2 pagesTime: 3 Hours Total Marks: 100: Printed Pages: 02 Sub Code:NEC703 Paper Id: 130718 Roll NoDeepanshi RuhelaNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- Low - Power - VLSI - JUNE 2023Document2 pagesLow - Power - VLSI - JUNE 20231ms21ec132No ratings yet

- Ec 703 2019-20Document2 pagesEc 703 2019-202000520310061No ratings yet

- Candidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarksDocument2 pagesCandidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarkssushilNo ratings yet

- Btech Ee 5 Sem Power System 1 Kee501 2023Document2 pagesBtech Ee 5 Sem Power System 1 Kee501 2023Manoj GuptaNo ratings yet

- Time: 3 Hours Total Marks: 70: PD PLDocument1 pageTime: 3 Hours Total Marks: 70: PD PLDeepanshi RuhelaNo ratings yet

- Ecen 3103Document2 pagesEcen 3103gaurav kumarNo ratings yet

- PPE Question PaperDocument2 pagesPPE Question Papersiva VNo ratings yet

- Previous Question PapersDocument11 pagesPrevious Question PapersShaik Sadhik BashaNo ratings yet

- OU - 1607 OU - 1607: FACULTY OF EngineeringDocument15 pagesOU - 1607 OU - 1607: FACULTY OF EngineeringSrikanth RenikuntaNo ratings yet

- Gec 101 FinalDocument2 pagesGec 101 FinalVijay Dhar MauryaNo ratings yet

- R3Fvle: & Etrr - )Document7 pagesR3Fvle: & Etrr - )sarveshNo ratings yet

- Vlsi Model 4-QPDocument2 pagesVlsi Model 4-QPsanthoshNo ratings yet

- Previous Year Question PaperDocument11 pagesPrevious Year Question PaperMinuNo ratings yet

- HVDC Ac Transmission Kee072Document2 pagesHVDC Ac Transmission Kee072xefedoy533No ratings yet

- Cmos Dec 2019Document2 pagesCmos Dec 2019Prabhodh KulkarniNo ratings yet

- Eds Mid Ii 2016 Set A &BDocument6 pagesEds Mid Ii 2016 Set A &BPurushotham MerimNo ratings yet

- Answer All Questions, Each Carries 5 Marks.: EE405 Electrical System DesignDocument19 pagesAnswer All Questions, Each Carries 5 Marks.: EE405 Electrical System DesigneeetistNo ratings yet

- WWW - Manaresults.co - In: (Electrical and Electronics Engineering)Document2 pagesWWW - Manaresults.co - In: (Electrical and Electronics Engineering)SaiNo ratings yet

- PSD - PG - Cat 2 QPDocument1 pagePSD - PG - Cat 2 QPSiva ForeviewNo ratings yet

- Ec0033-Asic Design-Model Qp-Vii Sem-Set2Document1 pageEc0033-Asic Design-Model Qp-Vii Sem-Set2skarthikpriyaNo ratings yet

- Final Put 2023Document3 pagesFinal Put 2023Akash AnandNo ratings yet

- 18EI56Document6 pages18EI56Rocky BhaiNo ratings yet

- Smart Materials, Sensors and ActuatorsDocument2 pagesSmart Materials, Sensors and ActuatorsmanojNo ratings yet

- 2019 May EE403-B - Ktu QbankDocument2 pages2019 May EE403-B - Ktu QbankjibipmathewNo ratings yet

- Low Power VLSI 2022-23Document1 pageLow Power VLSI 2022-23souranshusNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityHet ShahNo ratings yet

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071No ratings yet

- EE403 Distributed Generation and Smart Grids: Answer All Questions, Each Carries 5 MarksDocument2 pagesEE403 Distributed Generation and Smart Grids: Answer All Questions, Each Carries 5 MarksXahid YousafNo ratings yet

- EXAM Phys Elec II 2016 SolutionsDocument10 pagesEXAM Phys Elec II 2016 SolutionsThulasizwe PhethaNo ratings yet

- Nov - Dec 2021Document3 pagesNov - Dec 2021Pandyselvi BalasubramanianNo ratings yet

- Question Paper Code:: (10 2 20 Marks)Document2 pagesQuestion Paper Code:: (10 2 20 Marks)Kaleeswari SaraswathiNo ratings yet

- Question PapersDocument6 pagesQuestion Papersgunasekar3538No ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- Dem 22421Document15 pagesDem 22421Payal VeerNo ratings yet

- PS7004Document5 pagesPS7004shasi100% (1)

- Saranya Phase 1 BonafideDocument3 pagesSaranya Phase 1 BonafideshasiNo ratings yet

- U3895 PDFDocument13 pagesU3895 PDFshasiNo ratings yet

- Quantum Lasers: EE 566 Optical CommunicationsDocument26 pagesQuantum Lasers: EE 566 Optical CommunicationsshasiNo ratings yet

- BRK Man Sk6820Document216 pagesBRK Man Sk6820Victor AlvaradoNo ratings yet

- Building Utilities Module 2 Lesson 3Document7 pagesBuilding Utilities Module 2 Lesson 3Bryan ManlapigNo ratings yet

- Fault Codes For Quantum Engines: Section IVDocument26 pagesFault Codes For Quantum Engines: Section IVHenriqueNo ratings yet

- Lab#02: Characteristics of Power Diode: Objective: To Become Familiar With The Operating Principles of Power DiodesDocument5 pagesLab#02: Characteristics of Power Diode: Objective: To Become Familiar With The Operating Principles of Power DiodesUsmanIbrahimNo ratings yet

- Crane Control Catalog 7001 Relay SectionDocument9 pagesCrane Control Catalog 7001 Relay SectionAndi KaNo ratings yet

- RE 10 030/03.00 External Gear Pump Type G2, Series 4X: Up To 22.4 CM Up To 250 Bar NS 4 To 22 Replaces: 04.99Document12 pagesRE 10 030/03.00 External Gear Pump Type G2, Series 4X: Up To 22.4 CM Up To 250 Bar NS 4 To 22 Replaces: 04.99Paris AndreadisNo ratings yet

- NMB RT 8200wDocument2 pagesNMB RT 8200wSergio Diaz PereiraNo ratings yet

- Phantom 400Document14 pagesPhantom 400Yogendra ReddyNo ratings yet

- Systems Operation Testing and Adjusting: 4008-30 Industrial EngineDocument42 pagesSystems Operation Testing and Adjusting: 4008-30 Industrial EngineMARCO100% (1)

- Plansa Motopompa Caprari MEC-MG 80-4-3ADocument2 pagesPlansa Motopompa Caprari MEC-MG 80-4-3AAlex BancilaNo ratings yet

- PI 800sbd+zp PDFDocument7 pagesPI 800sbd+zp PDFFernando CastilloNo ratings yet

- Hydrotrac II User Manual 0.9Document43 pagesHydrotrac II User Manual 0.9Candhra SeparsaNo ratings yet

- Cargador de BateríasDocument42 pagesCargador de BateríasHumberto Dzul MayNo ratings yet

- Introduction To Micromaster MM420: Simatic S7Document22 pagesIntroduction To Micromaster MM420: Simatic S7ING. OSCAR PACHECONo ratings yet

- SttaptiteDocument6 pagesSttaptiteSean YangNo ratings yet

- Kuantitas Barang Per Gudang Jsbangunan 190626135041Document88 pagesKuantitas Barang Per Gudang Jsbangunan 190626135041Arié WibowoNo ratings yet

- Vstrom 250Document8 pagesVstrom 250Ricardo FernandezNo ratings yet

- FocDocument11 pagesFocSL PRASAD KOLLURUNo ratings yet

- 16H Motor Grader ATS00001-UP (MACHINE) POWERED BY 3196 Engine (SEBP3329 - 89) - Círculo - InstalarDocument12 pages16H Motor Grader ATS00001-UP (MACHINE) POWERED BY 3196 Engine (SEBP3329 - 89) - Círculo - InstalarDouglas GomesNo ratings yet

- ABB RCCB F 804Document12 pagesABB RCCB F 804catalinccNo ratings yet

- Operating System ConceptsDocument116 pagesOperating System ConceptsVivek278100% (3)

- 2A201-384E - M - Asteion4 Site PlanningDocument100 pages2A201-384E - M - Asteion4 Site Planningmedical serviceNo ratings yet

- 04 EN 3.0 A4webDocument2 pages04 EN 3.0 A4webDaniel SilvaNo ratings yet

- Brush Wear GuideDocument3 pagesBrush Wear GuideSomkene MbakweNo ratings yet

- K 737 Jul06 Engine Dxi 11Document73 pagesK 737 Jul06 Engine Dxi 11mliugong95% (21)

- HF 251 D & RFC 20Document2 pagesHF 251 D & RFC 20cripecaNo ratings yet

- RAM Vs ROMDocument5 pagesRAM Vs ROMShubh SatvikNo ratings yet

- Océ 5120 User's ManualDocument172 pagesOcé 5120 User's ManualdrchapmanNo ratings yet

- H4A71110 Vol-4 AllDocument181 pagesH4A71110 Vol-4 AllRhonny AlbertoNo ratings yet

- Abbreviations and Symbols For Hvac&R Drawings: Iranian Petroleum StandardsDocument12 pagesAbbreviations and Symbols For Hvac&R Drawings: Iranian Petroleum StandardsRoel FranciscoNo ratings yet