Professional Documents

Culture Documents

Gujarat Technological University

Uploaded by

Het Shah0 ratings0% found this document useful (0 votes)

6 views1 pageOriginal Title

2161101

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views1 pageGujarat Technological University

Uploaded by

Het ShahCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

Seat No.: ________ Enrolment No.

___________

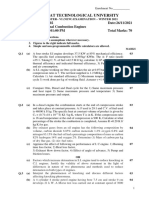

GUJARAT TECHNOLOGICAL UNIVERSITY

BE - SEMESTER– VI (NEW) EXAMINATION – WINTER 2021

Subject Code:2161101 Date:02/12/2021

Subject Name:VLSI Technology & Design

Time:10:30 AM TO 01:00 PM Total Marks: 70

Instructions:

1. Attempt all questions.

2. Make suitable assumptions wherever necessary.

3. Figures to the right indicate full marks.

4. Simple and non-programmable scientific calculators are allowed.

Q.1 (a) Explain the concept of regularity and modularity in brief. 03

(b) Discuss VLSI design flow in brief 04

(c) Explain MOS system under external bias for nMOS transistor in detail. 07

Q.2 (a) Explain LOCOS method in detail. 03

(b) Discuss the impact of different VLSI design styles upon the design cycle time 04

and the achievable circuit performances.

(c) Explain Gradual Channel Approximation (GCA), with help of that derive 07

current voltage equations for nMOS transistor.

OR

(c) Explain the fabrication of CMOS n-Well Process using neat diagrams. 07

Q.3 (a) Explain the substrate bias effect. 03

(b) Explain the channel length modulation effect in detail. 04

(c) Derive the threshold voltage equation for nMOS transistor. 07

OR

Q.3 (a) Compare FPGA and CPLD devices. 03

(b) Draw and explain the inverter circuit of depletion type nMOS load 04

(c) Draw circuit of CMOS inverter. Derive VIH , VIL ,VOL and VOH for CMOS 07

inverter.

Q.4 (a) What is CMOS ring oscillator? Explain in brief. 03

(b) Explain clocked JK latch circuit and waveform 04

(c) Define the propagation delay τPHL and τPLH Derive τPHL for CMOS inverter. 07

OR

Q.4 (a) Prove that switching power dissipation of CMOS inverter is proportional to 03

switching frequency.

(b) Explain Generalized NAND structure with Multiple inputs using 04

combinational MOS logic circuits.

(c) Derive the threshold voltage expression for CMOS two input NAND Gate. 07

Q.5 (a) Explain controllability and observabality in brief. 03

(b) Explain Built in self test (BIST) technique in brief. 04

(c) Explain voltage Bootstrapping in detail. 07

OR

Q.5 (a) Explain on chip clock generation techniques. 03

(b) Write short note on Complimentary pass transistor logic (CPL) 04

(c) Explain Dynamic CMOS Logic (Precharge-Evaluate Logic) in detail. Also 07

illustrate the cascading problem in dynamic CMOS logic.

*************

You might also like

- Computational Liquid Crystal Photonics: Fundamentals, Modelling and ApplicationsFrom EverandComputational Liquid Crystal Photonics: Fundamentals, Modelling and ApplicationsNo ratings yet

- Electrochemical Processes in Biological SystemsFrom EverandElectrochemical Processes in Biological SystemsAndrzej LewenstamNo ratings yet

- Be Summer 2021Document2 pagesBe Summer 2021Sandip SolankiNo ratings yet

- VLSI_papersDocument6 pagesVLSI_papersSandip SolankiNo ratings yet

- 3151105-BE-WINTER-2022Document2 pages3151105-BE-WINTER-2022kaushal.21beect008No ratings yet

- Model Question Paper with effect from 2020-21Document6 pagesModel Question Paper with effect from 2020-21Rocky BhaiNo ratings yet

- BE - Semester-VI Examination B.E. (Ec) Semester Vi Subject Code: Subject Name: VLSI Technology and Design Date: Time: Total Marks: 70 InstructionsDocument1 pageBE - Semester-VI Examination B.E. (Ec) Semester Vi Subject Code: Subject Name: VLSI Technology and Design Date: Time: Total Marks: 70 Instructionshiren467_ecNo ratings yet

- GTU BE-SEMESTER-V VLSI Design Exam QuestionsDocument2 pagesGTU BE-SEMESTER-V VLSI Design Exam QuestionsSuraj ThakurNo ratings yet

- Question Paper VlsiDocument2 pagesQuestion Paper VlsiH&P GamingNo ratings yet

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsArchana TrivediNo ratings yet

- M.Tech. Degree Examination, Dec.08/Jan.09: Advances in VLSI DesignDocument1 pageM.Tech. Degree Examination, Dec.08/Jan.09: Advances in VLSI DesignRavindra vsNo ratings yet

- VLSI DesignDocument5 pagesVLSI DesignqwertyuiopNo ratings yet

- Microelectronics and VLSI Design ExamDocument3 pagesMicroelectronics and VLSI Design ExampikluNo ratings yet

- M.Tech I Semester Supplementary Examinations February/March 2018Document1 pageM.Tech I Semester Supplementary Examinations February/March 2018baburao_kodavatiNo ratings yet

- Be Winter 2022Document1 pageBe Winter 2022Fariha shaikhNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsContent for all CreatorNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityTaral MehtaNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Assignment-2 Vlsi 29.04.2023Document1 pageAssignment-2 Vlsi 29.04.2023040-NishanthNo ratings yet

- Eprvd-102 Eprds-102a - 01.12 PDFDocument2 pagesEprvd-102 Eprds-102a - 01.12 PDFNaresh KumarNo ratings yet

- VLSI DESIGN Question Bank: Unit 1Document12 pagesVLSI DESIGN Question Bank: Unit 1Babu GundlapallyNo ratings yet

- 16EC5DCFOVDocument2 pages16EC5DCFOVvkjoshiNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityyicef37689No ratings yet

- VTU Model Question Papers VI Sem ECE - TCEDocument44 pagesVTU Model Question Papers VI Sem ECE - TCEMr Ashutosh SrivastavaNo ratings yet

- Ecen 3103Document2 pagesEcen 3103gaurav kumarNo ratings yet

- Be Summer 2022Document1 pageBe Summer 2022Fariha shaikhNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- ADC Paper 3Document1 pageADC Paper 3ashishNo ratings yet

- CMOS Technology Question Bank & TutorialDocument3 pagesCMOS Technology Question Bank & TutorialRathore Yuvraj SinghNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document8 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaNo ratings yet

- 2022w MergedDocument12 pages2022w MergedTaral MehtaNo ratings yet

- Question Paper CodeDocument2 pagesQuestion Paper Codekenny kannaNo ratings yet

- VLSID R20 Q BankDocument4 pagesVLSID R20 Q BankSATYA SRI LIKHITHA DUSANAPUDINo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological Universitywolf gamingNo ratings yet

- Ec 1354Document5 pagesEc 1354kvnelavarasiNo ratings yet

- C H1074 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesC H1074 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDeepak KumarNo ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- See Cmos Vlsi Jan 2020Document3 pagesSee Cmos Vlsi Jan 20201ms21ec132No ratings yet

- Gujarat Technological University: InstructionsDocument26 pagesGujarat Technological University: Instructionsdilawar sumraNo ratings yet

- E ( (Caqsd CCN: G Mox - Mor Ks - E 3 HoursDocument7 pagesE ( (Caqsd CCN: G Mox - Mor Ks - E 3 HourssarveshNo ratings yet

- Semiconductor Device Modeling ExamDocument2 pagesSemiconductor Device Modeling ExamVijay Dhar MauryaNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityyicef37689No ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityRenieNo ratings yet

- PDFDocument29 pagesPDFSaurabh PatelNo ratings yet

- Gujarat Technological University: Subject Code:161001 Date: Subject Name: Digital Communication Time: Total Marks: 70Document1 pageGujarat Technological University: Subject Code:161001 Date: Subject Name: Digital Communication Time: Total Marks: 70Taral MehtaNo ratings yet

- Vlsi ModuleDocument2 pagesVlsi ModuleAshwini kumarNo ratings yet

- Gtu Computer 3130704 Summer 2023Document2 pagesGtu Computer 3130704 Summer 2023madhavjani06No ratings yet

- GTU BE Semester VII Microwave Theory and Techniques Exam QuestionsDocument1 pageGTU BE Semester VII Microwave Theory and Techniques Exam Questionsfeyayel988No ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityRushabh PatelNo ratings yet

- VLSI Design 2010 Sept CUSATDocument1 pageVLSI Design 2010 Sept CUSATvineethvrr5948No ratings yet

- Be Summer 2021Document1 pageBe Summer 2021jagdishsimariyaNo ratings yet

- Previous Question PapersDocument4 pagesPrevious Question Papersshaker423No ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological Universityyicef37689No ratings yet

- SEPTEMBERDocument3 pagesSEPTEMBERRocky BobeeNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- Gujarat Technological UniversityDocument3 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Computer Aided Process Synthesis Exam QuestionsDocument2 pagesComputer Aided Process Synthesis Exam QuestionsHet ShahNo ratings yet

- GTU BE Semester VII Process Equipment Design Exam QuestionsDocument2 pagesGTU BE Semester VII Process Equipment Design Exam QuestionsHet ShahNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- GTU BE Semester VI Exam Industrial Engineering QuestionsDocument1 pageGTU BE Semester VI Exam Industrial Engineering QuestionsHet ShahNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityHet ShahNo ratings yet

- GTU BE Semester VI Exam Questions on Bio-Potential InstrumentationDocument2 pagesGTU BE Semester VI Exam Questions on Bio-Potential InstrumentationHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- GTU BE Semester VI Digital Control Exam QuestionsDocument1 pageGTU BE Semester VI Digital Control Exam QuestionsHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Control of Electrical Drives Exam QuestionsDocument2 pagesControl of Electrical Drives Exam QuestionsHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityVijay DharajiyaNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- GTU BE Semester VI Exam High Voltage Engineering QuestionsDocument2 pagesGTU BE Semester VI Exam High Voltage Engineering QuestionsHet ShahNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- Product Specification: 7/16M-4310M HCF1/2 LMDocument1 pageProduct Specification: 7/16M-4310M HCF1/2 LMlatinocomm2009No ratings yet

- Synchronised Ujt Triggering CircuitDocument2 pagesSynchronised Ujt Triggering Circuitsvinod s67% (3)

- TL 431Document79 pagesTL 431uumpNo ratings yet

- XHHW-2: XLP Insulation, 600 VoltsDocument2 pagesXHHW-2: XLP Insulation, 600 VoltsNaveedNo ratings yet

- Manual For Filastruder ENGLISH PDFDocument10 pagesManual For Filastruder ENGLISH PDFstavroula zarkadoulaNo ratings yet

- DIY Automatic Alcohol Dispenser No Arduino NeededDocument16 pagesDIY Automatic Alcohol Dispenser No Arduino NeededAnkur RaiNo ratings yet

- Data Sheet de Un Guardamotor SIEMENS Linea Nueva Tamaño S00Document10 pagesData Sheet de Un Guardamotor SIEMENS Linea Nueva Tamaño S00IvanNo ratings yet

- Resonant DC-DC ConvertingDocument21 pagesResonant DC-DC ConvertingSanthoshNo ratings yet

- NTM 51-10-01Document21 pagesNTM 51-10-01kien Duy PhanNo ratings yet

- Classf and Inverse ADS PaperDocument11 pagesClassf and Inverse ADS Papergaurav bhargavNo ratings yet

- Steel Calculation For Two Way Slab TamilDocument1 pageSteel Calculation For Two Way Slab TamilmanojNo ratings yet

- Instal RRUDocument85 pagesInstal RRUКурбан УмархановNo ratings yet

- Rohini 69038786578Document4 pagesRohini 69038786578Avinash SinghNo ratings yet

- Prism Audio LA50B DatasheetDocument2 pagesPrism Audio LA50B DatasheetJason PartridgeNo ratings yet

- Engineering Colleges and Institutes in Madhya PradeshDocument3 pagesEngineering Colleges and Institutes in Madhya PradeshAnsh PandeyNo ratings yet

- Determine SCR Holding, Latching Currents & Breakover VoltageDocument4 pagesDetermine SCR Holding, Latching Currents & Breakover VoltageRishi Raj KanojiaNo ratings yet

- Draw Electrical Circuits for Common Industrial Devices and Control SystemsDocument10 pagesDraw Electrical Circuits for Common Industrial Devices and Control SystemsAjay SahuNo ratings yet

- Learn Arduino Sensor With Projects For BeginnersDocument85 pagesLearn Arduino Sensor With Projects For BeginnersJorge Jockyman JuniorNo ratings yet

- SCT 013Document1 pageSCT 013SilvioNo ratings yet

- DC Power Transmission TechnologyDocument10 pagesDC Power Transmission TechnologyDrVikas Singh BhadoriaNo ratings yet

- Micr Ostep: User ManualDocument54 pagesMicr Ostep: User ManualRoberto MedinaNo ratings yet

- Relays TerminologyDocument1 pageRelays TerminologyJavid SalamovNo ratings yet

- Manual CIAC CH41E-CG41EDocument20 pagesManual CIAC CH41E-CG41EPrimero Valencia LuisNo ratings yet

- Data / Input Value Comments: High-Density Zone - Worksheet and ChecklistDocument2 pagesData / Input Value Comments: High-Density Zone - Worksheet and Checklistfernanda boldtNo ratings yet

- Unit 1 Life Stories - Vocab 1Document3 pagesUnit 1 Life Stories - Vocab 1Trần NgọcNo ratings yet

- 3600 - Tech Bro - Satis + Infant Closed Incubator MédiprémaDocument4 pages3600 - Tech Bro - Satis + Infant Closed Incubator MédiprémaMisril YadiNo ratings yet

- G-Type Alternator 100ampDocument6 pagesG-Type Alternator 100ampxaviercomamengualNo ratings yet

- Baylan: AK-311 ES2 Remote Reading and Prepaid Water MetersDocument1 pageBaylan: AK-311 ES2 Remote Reading and Prepaid Water Metersamr ibrahimNo ratings yet

- Index of Interactive Equations: Machinery's Handbook 27th EditionDocument5 pagesIndex of Interactive Equations: Machinery's Handbook 27th EditionEduardo CorreiaNo ratings yet

- Installation Manual: Technology Within Your ReachDocument2 pagesInstallation Manual: Technology Within Your ReachJhonny SilvaNo ratings yet