Professional Documents

Culture Documents

ECE 3002 VLSI Lab Task - D Latch and D Flip Flop Characterization

Uploaded by

Kotha HemanthOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ECE 3002 VLSI Lab Task - D Latch and D Flip Flop Characterization

Uploaded by

Kotha HemanthCopyright:

Available Formats

1

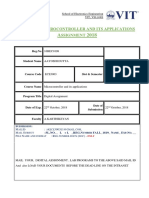

VLSI(ECE3002)

Lab Task – 05

Name: KOTARU DRONA PHANI KOWSHIK

Redg.No: 18BEC0175

SLOT: L13+L14

FACULTY: NITHISH KUMAR V

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

2

Aim:

Circuit Diagram:

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

3

OUTPUT

Now to find the time delay

For fall delay

V(d)= 1.0000015u sec

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

4

V(q)=1.000016u sec

Fall delay(TPDF)=1.000016us-1.0000015us

=14.5ps

For Raise delay

V(d)=2.0000005u sec

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

5

V(q)=2.000016 u sec

Raise Delay(TPDR) =2.000016us - 2.0000005us

=15.8ps

Total propagation delay=((raise delay)+(fall delay))/2

=15.15psec

Average power Consumed

Power of M8 = 4.3524n W

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

6

Power of M5 = -0.311n W

Power of M2 = 44.022n W

Power of M1 = 23.956n W

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

7

Power of M7 = -10.1n W

Power of M6 = 0.969n W

Power of M4 = 6.9405n W

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

8

Power of M3 = -13.02n W

Average power=4.3524 -10.1+0.969-0.311+6.9405-13.02+44.022 + 23.956

=56.8089nW

Inference:

Here we also get the power in negative for some mosfets.

We can see in the functionality graph that when clock is 1 then output is equal to the

previous one. And when clock is 0 then output is equal to given input.

Individual NMOS or PMOS cannot pass both high and low logic levels with equal strength

(i.e. on resistance). A single NMOS device can pass a strong logic 0 but will pass a weak

logic 1. Conversely, a single PMOS device can pass a strong logic 1 but will pass a weak

logic 0.

Result:

The functionality of the negative d-latch was plotted on Lt spice. The tpdr is 15.8 ps and tpdf is 14.5

ps. Then the average delay which is the average of fall delay and raie delay is 15.15ps.The average

power of d-latch is

56.8089nW.

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

9

B.

D FLIP FLOPS

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

10

D FLIP FLOP USING DFF BLOCK

Here the DFF is negative edge tigger so I used clk for making it positive edge

trigger

Output in LTSPICE

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

11

INFERENCE

The D flip flop output ‘Q’ follows input ‘D’ at only raising edges of the clock

and at remaining time it stores the previous value of input .

RESULT

Implentation of D flipflop is done using transmission gate logic and

corresponding outputs are obtained .

Reg.No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05

You might also like

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentDocument43 pagesECE3003 M A 2018: Icrocontroller and Its Applications SsignmentAayoshi DuttaNo ratings yet

- Final Review DSPDocument17 pagesFinal Review DSPKota Krishna DheerajNo ratings yet

- Digital Communication Systems: ECE-4001 TASK-3Document12 pagesDigital Communication Systems: ECE-4001 TASK-3Aniket SaxenaNo ratings yet

- 17BEC0901 TASK 2 MicrocontrollersDocument13 pages17BEC0901 TASK 2 Microcontrollersrohan joshuaNo ratings yet

- Dcs Vit Lab ManualDocument36 pagesDcs Vit Lab ManualDEEPIKANo ratings yet

- Microprocessors and Microcontrollers Lab ManualDocument53 pagesMicroprocessors and Microcontrollers Lab ManualKarthik BoggarapuNo ratings yet

- Ecad Lab ManualDocument55 pagesEcad Lab Manualjeravi84100% (3)

- DSP Lab ReportDocument28 pagesDSP Lab ReportKaaviyaNo ratings yet

- Micro Controller Lab Manual 1Document38 pagesMicro Controller Lab Manual 1Suresh KumarNo ratings yet

- NI Tutorial 3115 enDocument3 pagesNI Tutorial 3115 enajith.ganesh2420No ratings yet

- Final C++ ManualDocument36 pagesFinal C++ ManualHarish G CNo ratings yet

- Ec - 501 - Microprocessor and Its ApplicationDocument41 pagesEc - 501 - Microprocessor and Its ApplicationDr Nikita ShivhareNo ratings yet

- Embedded Systems Lab 18ECL66: Demonstrate The Use of An External Interrupt To Toggle An LED On/OffDocument16 pagesEmbedded Systems Lab 18ECL66: Demonstrate The Use of An External Interrupt To Toggle An LED On/OffJAYANTH JNo ratings yet

- Digital Lab VIVA QuestionsDocument4 pagesDigital Lab VIVA QuestionsAnirudhan RaviNo ratings yet

- Astable Multivibrator Using 555 Timer Simulated in ProteusDocument2 pagesAstable Multivibrator Using 555 Timer Simulated in ProteusSumithNo ratings yet

- Optical Fiber Transmission Link ElementsDocument15 pagesOptical Fiber Transmission Link ElementsAchu0% (1)

- MPMC Lab ManualDocument107 pagesMPMC Lab ManualReena RajNo ratings yet

- Extracting Features From The Fundus Image Using Canny Edge Detection Method For PreDetection of Diabetic RetinopathyDocument6 pagesExtracting Features From The Fundus Image Using Canny Edge Detection Method For PreDetection of Diabetic RetinopathyVIVA-TECH IJRINo ratings yet

- Experiment No. 01 Experiment Name-ASK ModulationDocument47 pagesExperiment No. 01 Experiment Name-ASK ModulationmuskanNo ratings yet

- BME 3111 S#5 Data Reduction TechniquesDocument28 pagesBME 3111 S#5 Data Reduction TechniquesMuhammad Muinul Islam100% (1)

- Data Processing InstructionDocument35 pagesData Processing InstructionDado Fabrička GreškaNo ratings yet

- VLSI 7th Sem Lab Manual PDFDocument66 pagesVLSI 7th Sem Lab Manual PDFFootlooseNo ratings yet

- DSDV MODULE 3 Implementation FabricsDocument17 pagesDSDV MODULE 3 Implementation Fabricssalman shariffNo ratings yet

- Introduction To TMS320C6713 DSP Starter Kit DSK)Document18 pagesIntroduction To TMS320C6713 DSP Starter Kit DSK)Anup DharanguttiNo ratings yet

- HDL Manual (18ecl58)Document20 pagesHDL Manual (18ecl58)lohith sNo ratings yet

- Practical: 1: Aim: Getting Started With Nodemcu, Arduino With Esp8266 and Esp32 in The Arduino IdeDocument25 pagesPractical: 1: Aim: Getting Started With Nodemcu, Arduino With Esp8266 and Esp32 in The Arduino IdeGanesh GhutiyaNo ratings yet

- VLSI Internship Report by REC RewaDocument42 pagesVLSI Internship Report by REC RewaTrivedi JiiNo ratings yet

- Interfacing Programs For 8085Document37 pagesInterfacing Programs For 8085archankumarturagaNo ratings yet

- DSA Codes - Hackerrank - AllDocument141 pagesDSA Codes - Hackerrank - Alludaykiran penumakaNo ratings yet

- Q4Document3 pagesQ4SkvkNo ratings yet

- EC8491 Notes PDFDocument90 pagesEC8491 Notes PDFgunasekaran kNo ratings yet

- Choosing Between DSP, FPGA and ASIC for Digital Hardware in Software Defined RadioDocument13 pagesChoosing Between DSP, FPGA and ASIC for Digital Hardware in Software Defined RadioKAMRAN12345786No ratings yet

- Automatic Test Pattern Generation - II: Virendra SinghDocument34 pagesAutomatic Test Pattern Generation - II: Virendra Singhamy2chang_1No ratings yet

- To Design An Adaptive Channel Equalizer Using MATLABDocument43 pagesTo Design An Adaptive Channel Equalizer Using MATLABAngel Pushpa100% (1)

- Me2255 Electronics and Microprocessor Anna University Question BankDocument6 pagesMe2255 Electronics and Microprocessor Anna University Question BankMayakannan RNo ratings yet

- FALLSEM2019-20 STS4021 SS VL2019201000258 Reference Material I 18-Jul-2019 Ppt-A2 Module 2 PDFDocument134 pagesFALLSEM2019-20 STS4021 SS VL2019201000258 Reference Material I 18-Jul-2019 Ppt-A2 Module 2 PDFjahnavi rajuNo ratings yet

- BSC Electronics Syllabus Kerala UniversityDocument64 pagesBSC Electronics Syllabus Kerala UniversityVarunRaj67% (3)

- 8051 Lab ManualDocument35 pages8051 Lab ManualVenkat BalajiNo ratings yet

- EE6403 DSP Hand Written NotesDocument282 pagesEE6403 DSP Hand Written Notessyed ibrahim100% (1)

- Seven Segment Based Alarm Clock Using 8051 MicrocontrollerDocument16 pagesSeven Segment Based Alarm Clock Using 8051 MicrocontrollerBiswajit SarkarNo ratings yet

- MPMC Lab Manual To PrintDocument138 pagesMPMC Lab Manual To PrintKasthuri SelvamNo ratings yet

- D Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALDocument41 pagesD Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALArrnaav Singh RathoreeNo ratings yet

- Program For Interfacing 8279: 1. 8085 Microprocessor Kit 2. 8279 Interfacing Module 3. Power SupplyDocument21 pagesProgram For Interfacing 8279: 1. 8085 Microprocessor Kit 2. 8279 Interfacing Module 3. Power SupplySubhashini MurugesanNo ratings yet

- 2 To 4 DecoderDocument6 pages2 To 4 DecoderKrishna PremNo ratings yet

- Lesson Plan - Signals & Systems 2012Document3 pagesLesson Plan - Signals & Systems 2012KALAIMATHINo ratings yet

- Ad Hoc and Wireless Sensor Networks - Ec8702: Session byDocument28 pagesAd Hoc and Wireless Sensor Networks - Ec8702: Session byRaja MadhuvanthiNo ratings yet

- MATLAB-ZF-LMSDocument4 pagesMATLAB-ZF-LMSImmanuel VinothNo ratings yet

- Tripping Sequence Recorder Cum IndicatorDocument7 pagesTripping Sequence Recorder Cum IndicatormahbubunnisaNo ratings yet

- 8051-CH6-ArithLigic InstructnsDocument114 pages8051-CH6-ArithLigic Instructnsshivaspy100% (1)

- ADC Program For LPC2138Document8 pagesADC Program For LPC2138hypernuclide100% (1)

- Ranjana Chaturvedi - A Survey On Compression Techniques For EcgDocument3 pagesRanjana Chaturvedi - A Survey On Compression Techniques For Ecglucamessina71No ratings yet

- Adc Interfacing With 8051Document2 pagesAdc Interfacing With 8051Sumukha Kumar0% (1)

- Microcontroller Lab Manual PDFDocument61 pagesMicrocontroller Lab Manual PDFManoj SkNo ratings yet

- Generation of PWM Using Verilog in FPGA 11Document7 pagesGeneration of PWM Using Verilog in FPGA 11Rajani kant tiwariNo ratings yet

- VLSI M3 Ktunotes - in PDFDocument76 pagesVLSI M3 Ktunotes - in PDFSangeetha SumamNo ratings yet

- Two Stage Amplifier Circuit Analysis Lab ManualDocument57 pagesTwo Stage Amplifier Circuit Analysis Lab Manualvinodh123No ratings yet

- L23Document29 pagesL23Mary MorseNo ratings yet

- Aula6 - ConversoresDocument26 pagesAula6 - ConversoreslucianoNo ratings yet

- AM5898NDocument11 pagesAM5898NGabriel Cosme VazquezNo ratings yet

- Vlsi System Design: FALL - (2019-20) Pranav Kumar 17BEC0473 Prof. Jagannadha Naidu K 15Document12 pagesVlsi System Design: FALL - (2019-20) Pranav Kumar 17BEC0473 Prof. Jagannadha Naidu K 15PRANAV KUMAR 17BEC0473No ratings yet

- Driver Mosfet MIC5021Document10 pagesDriver Mosfet MIC5021robert_lascuNo ratings yet

- Notes PDFDocument24 pagesNotes PDFkalyanNo ratings yet

- Digital System Design and CMOS Analog IC DesignDocument6 pagesDigital System Design and CMOS Analog IC DesignrppvchNo ratings yet

- Car Park Digital ControllerDocument25 pagesCar Park Digital Controllermuddassir07100% (5)

- Power Management & Supply: Datasheet, Version 2.0, 04 July 2011Document19 pagesPower Management & Supply: Datasheet, Version 2.0, 04 July 2011Eletrohelp EletrodomésticosNo ratings yet

- Topic 4Document28 pagesTopic 4AzWia MkhtrNo ratings yet

- An-120 Capacitive Coupling For Ethernet TransceiverDocument2 pagesAn-120 Capacitive Coupling For Ethernet Transceiversrinie_5No ratings yet

- Irwin, Engineering Circuit Analysis, 11e ISVDocument194 pagesIrwin, Engineering Circuit Analysis, 11e ISVDr. Mohammad ZunoubiNo ratings yet

- 74HC14N TGSDocument4 pages74HC14N TGSLeila MoralesNo ratings yet

- Design of Low Power 12-Bit Magnitude ComparatorDocument6 pagesDesign of Low Power 12-Bit Magnitude Comparatoreditor_ijtelNo ratings yet

- Replacement of TCA 785 IC with Configurable PSoC IC for Single and Three Phase ConvertersDocument6 pagesReplacement of TCA 785 IC with Configurable PSoC IC for Single and Three Phase Convertersbpd21No ratings yet

- GPIO ProgrammingDocument12 pagesGPIO ProgrammingNikhil SinghNo ratings yet

- Capacitance in Series and ParallelDocument21 pagesCapacitance in Series and Parallelzeravla_19No ratings yet

- Fpga and Cads: Presented by Peng Du & Xiaojun BaoDocument28 pagesFpga and Cads: Presented by Peng Du & Xiaojun BaoMani KannanNo ratings yet

- Medha Servo Drives Written Exam Pattern Given by KV Sai KIshore (BVRIT-2005-09-ECE)Document2 pagesMedha Servo Drives Written Exam Pattern Given by KV Sai KIshore (BVRIT-2005-09-ECE)Varaprasad KanugulaNo ratings yet

- RS-232 transceiver IC with one supply voltageDocument7 pagesRS-232 transceiver IC with one supply voltageBalaji TriplantNo ratings yet

- Digital and Pulse-Train Conditioning: Digital I/O InterfacingDocument6 pagesDigital and Pulse-Train Conditioning: Digital I/O InterfacingcoolhemakumarNo ratings yet

- DM 00043574Document1,037 pagesDM 00043574morpheus_unknownNo ratings yet

- Utc 2030Document14 pagesUtc 2030Jose M PeresNo ratings yet

- Power Amplifier 180W Stereo 2x80W Bridge Mode TDA7294Document4 pagesPower Amplifier 180W Stereo 2x80W Bridge Mode TDA7294veerakumarsNo ratings yet

- CD4000 LibDocument33 pagesCD4000 LibFernando Sobrino-Manzanares MasNo ratings yet

- Three-Stage OpAmp DesignDocument5 pagesThree-Stage OpAmp Design駱祈宏No ratings yet

- 7493 Count EricDocument1 page7493 Count EricHesusa Krisani Mendoza CardonaNo ratings yet

- Max 7705Document8 pagesMax 7705savapostNo ratings yet

- LIC Lab ManualDocument65 pagesLIC Lab ManualBala Subramanian0% (1)

- Encoder, Decoder, Multiplexers and DemultiplexersDocument31 pagesEncoder, Decoder, Multiplexers and DemultiplexersZaghi Junior100% (1)

- PONTES-Nelson Aka NeyllowDocument41 pagesPONTES-Nelson Aka NeyllowCamilo Caetano CarmeloNo ratings yet

- Ec8453 - Linear Integrated Circuits: Question BankDocument5 pagesEc8453 - Linear Integrated Circuits: Question Bankrkkumar07No ratings yet

- Tutorial 5Document8 pagesTutorial 5Muhammad FauziNo ratings yet

- Large Signal AmplifierDocument10 pagesLarge Signal AmplifierMohammed IftekharNo ratings yet