Professional Documents

Culture Documents

DLD List of Experiments

DLD List of Experiments

Uploaded by

Ishfaq AhmadCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DLD List of Experiments

DLD List of Experiments

Uploaded by

Ishfaq AhmadCopyright:

Available Formats

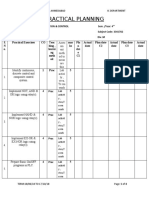

Department of Electrical Engineering

Riphah College of Science and Technology

Riphah International University, Lahore Campus

Program: B.Sc. Electrical Engineering Semester: III

Subject: EE-202 Digital Logic Design

List of Experiments

Level

S. No Experiments of CLO

Inquiry

0 4,6

Experiment 1 Introduction to digital logic trainer

1 4,6

Experiment 2 Verification of truth tables of basic logic gates

1 4,6

Experiment 3 Simulation and implementation of functions using basic logic gates

Design and implement a logic circuit with four input variables that 1 4,6

Experiment 4

will only produce a 1 output when exactly 3 input variables are 1

Design a combinational circuit with 4 inputs A, B, C and D and one 4,6

output E. E is equal to 1 when A=1 if B=0 or when B=1 provided 1

Experiment 5

that either C or D is also equal to 1. Otherwise, the output is equal to

0

To implement basic logic gates using universal gates (NAND & 1 4,6

Experiment 6

NOR)

To design and implement half adder and full adder, half Subtractor 1 4,6

Experiment 7(a)

and full subtractor.

Experiment 7(b) To design and implement half Subtractor and full subtractor. 1 4,6

Experiment 8(a) Investigate the operation of Encoders 1 4,6

1 4,6

Experiment 8(b) Investigate the operation of Decoders

Experiment 9(a) Investigate the operation of multiplexers 1 4,6

Experiment 9(b) Investigate the operation of demultiplexers 1 4,6

Experiment 10 Implementation of RS latches 1 4,6

Experiment 11 Implementation of JK flip flop 1 4,6

1 4,6

Experiment 12 Implementation of JK flip flop circuits

1 4,6

Experiment 13 To study shift-register operation

1 4,6

Experiment 14 To implement and study multivibrators using 555 timer IC

Department of Electrical Engineering

Riphah College of Science and Technology

Riphah International University, Lahore Campus

1 4,6

Experiment 15 Implement synchronous up/down counter using JK flip flop

2 4,6

Experiment 16 Open Ended Lab

You might also like

- Digital Design Interview QuestionsDocument47 pagesDigital Design Interview QuestionsSangameshwer Enterprises100% (1)

- Ecen 248 Lab 8 ReportDocument7 pagesEcen 248 Lab 8 Reportapi-241454978No ratings yet

- MESB333 Lab Manual (Uniten)Document73 pagesMESB333 Lab Manual (Uniten)Natalie Ninachuu0% (1)

- Home Assignment No-4: Digital Logic Design BEE-1B&CDocument4 pagesHome Assignment No-4: Digital Logic Design BEE-1B&COzi ---No ratings yet

- Electronics Circuit Design Lab ManualsDocument71 pagesElectronics Circuit Design Lab ManualsTalha WaqarNo ratings yet

- Nptel Virtual Lab ListDocument5 pagesNptel Virtual Lab Listchanchlesh tripathiNo ratings yet

- Adv CCIE R&S - Vol-I - DiagramsDocument64 pagesAdv CCIE R&S - Vol-I - DiagramsmanishdokaniaNo ratings yet

- Digital Logic & Processors: Lab ManualDocument38 pagesDigital Logic & Processors: Lab ManualPAILA HEMANTHNo ratings yet

- 15ECL38 - Digital-Electronics LMDocument55 pages15ECL38 - Digital-Electronics LMbnatarajNo ratings yet

- Digital Design Lab Course Code:-Cse256PDocument38 pagesDigital Design Lab Course Code:-Cse256PYash JaiswalNo ratings yet

- Lab 10Document5 pagesLab 10Aafaq khanNo ratings yet

- Laboratory Manual: Digital ElectronicsDocument59 pagesLaboratory Manual: Digital ElectronicsKrunal MakwanaNo ratings yet

- Designing Test Suites: Design A Test Suite For The Following ProblemDocument2 pagesDesigning Test Suites: Design A Test Suite For The Following ProblemAndroid Sourvivors sNo ratings yet

- DLP Lab Manual 2Document36 pagesDLP Lab Manual 2sokkuNo ratings yet

- ECEN 248 Lab 8 ReportDocument7 pagesECEN 248 Lab 8 ReportRebecca SontheimerNo ratings yet

- Bee31101 Lab 6 6 Electronics Engineering Laboratory IV DC Motor Control SerDocument36 pagesBee31101 Lab 6 6 Electronics Engineering Laboratory IV DC Motor Control Serelxao9292100% (1)

- Eca-II Lab Manual - Fa20Document100 pagesEca-II Lab Manual - Fa20Hafiz Hassan JawadNo ratings yet

- DLD Lab 1Document5 pagesDLD Lab 1Sardar SubhanNo ratings yet

- Final Report For Data CommunicationDocument50 pagesFinal Report For Data CommunicationMst. Muktara KhatunNo ratings yet

- Course Outline of CSE 104Document4 pagesCourse Outline of CSE 104Ju KaNo ratings yet

- Lab 11Document10 pagesLab 11Aafaq khanNo ratings yet

- Plate 21Document8 pagesPlate 21Charles RitterNo ratings yet

- Expt 6 PDFDocument18 pagesExpt 6 PDFYashodhan JaltareNo ratings yet

- Lab Manual: Digital System Design (PR) : COT-215 Digital Electronics (P) : IT-211Document7 pagesLab Manual: Digital System Design (PR) : COT-215 Digital Electronics (P) : IT-211rajeshforallNo ratings yet

- ECA-II Lab ManualDocument89 pagesECA-II Lab Manualsarmad.hassanNo ratings yet

- Lab 11 ReportDocument22 pagesLab 11 Reportnawinnawmu1026No ratings yet

- LMECE216Document49 pagesLMECE216Demba JallowNo ratings yet

- Activity 7 - Shift RegistersDocument6 pagesActivity 7 - Shift RegistersBETTY UYNo ratings yet

- DLP Lab ManualDocument72 pagesDLP Lab ManualPoorna chand Evuru100% (1)

- EE 179.1 Activity 5: Time ResponseDocument6 pagesEE 179.1 Activity 5: Time ResponseMark EricNo ratings yet

- Lab 9Document2 pagesLab 9Shweta LimbachiyaNo ratings yet

- CSE 324 - OBE Course Syllabus - Sec D - EEEDocument2 pagesCSE 324 - OBE Course Syllabus - Sec D - EEEMasud SarkerNo ratings yet

- Opendaylight Performance Stress Test Report: V1.0: Lithium Vs HeliumDocument8 pagesOpendaylight Performance Stress Test Report: V1.0: Lithium Vs HeliumRudhyNo ratings yet

- ECA-II Lab Manual - SP20Document99 pagesECA-II Lab Manual - SP20Hafiz Hassan JawadNo ratings yet

- DLP Lab ManualDocument32 pagesDLP Lab ManualHarshaNo ratings yet

- DAA Labmanual-UpdatedDocument38 pagesDAA Labmanual-UpdatedanuragshetyeNo ratings yet

- PLC LabDocument4 pagesPLC Laburvish_soniNo ratings yet

- Cs8382 Digital Manual PrintDocument47 pagesCs8382 Digital Manual PrintSaravana kumarNo ratings yet

- Sequential Logic Circuits: ObjectiveDocument23 pagesSequential Logic Circuits: ObjectiveTrần TânNo ratings yet

- Reading Chapters 1 - Week Topic Work Due Lab 1Document21 pagesReading Chapters 1 - Week Topic Work Due Lab 1Farah EssidNo ratings yet

- (Download PDF) Computational Nuclear Engineering and Radiological Science Using Python 1St Edition Ryan Mcclarren Online Ebook All Chapter PDFDocument42 pages(Download PDF) Computational Nuclear Engineering and Radiological Science Using Python 1St Edition Ryan Mcclarren Online Ebook All Chapter PDFgeorge.rosner865100% (9)

- ETU 07322 - Digital Electronic Lab ManualDocument33 pagesETU 07322 - Digital Electronic Lab ManualFrancis LubangoNo ratings yet

- Experiment No. 04: Three Phase Half & Full-Wave Controlled RectifierDocument6 pagesExperiment No. 04: Three Phase Half & Full-Wave Controlled RectifierMD.Minhazul Islam ShazedNo ratings yet

- Experiment 6Document5 pagesExperiment 6SAYYAMNo ratings yet

- Thermo I CDFDocument7 pagesThermo I CDFYasir RazaNo ratings yet

- 15ee408 Analog and Digital Integrated Circuits Laboratory 0 0 2 1 Course ObjectivesDocument3 pages15ee408 Analog and Digital Integrated Circuits Laboratory 0 0 2 1 Course ObjectivesnandhakumarmeNo ratings yet

- Electric Circuits Lab 15EE103L PDFDocument61 pagesElectric Circuits Lab 15EE103L PDFMadhavanInduNo ratings yet

- LAB With Experiments DetailsDocument14 pagesLAB With Experiments DetailsMohd Helmy Hakimie RozlanNo ratings yet

- Lecture Plan Digital ElectronicsDocument3 pagesLecture Plan Digital Electronicsprerak guptaNo ratings yet

- STLD Lab 2-1Document44 pagesSTLD Lab 2-1penumallu srinivasa reddyNo ratings yet

- EENG301LDocument3 pagesEENG301LOmar SroujiNo ratings yet

- List of Lab Experiments - CSE314 PDFDocument1 pageList of Lab Experiments - CSE314 PDFsk3 khanNo ratings yet

- 19A04501P ICA Lab SylDocument3 pages19A04501P ICA Lab Sylchiranjeevi muppalaNo ratings yet

- Jhep06 (2011) 128Document40 pagesJhep06 (2011) 128Deepak KumarNo ratings yet

- Experiment 1 - Basic Logic GatesDocument7 pagesExperiment 1 - Basic Logic Gatesfaizan bariNo ratings yet

- Question Bank DSD III SemDocument4 pagesQuestion Bank DSD III Semasymtodegaming0501No ratings yet

- Co-Requisite: Prerequisite: Data Book / Codes/Standards Course Category Course Designed by ApprovalDocument1 pageCo-Requisite: Prerequisite: Data Book / Codes/Standards Course Category Course Designed by ApprovalRajalearn2 Ramlearn2No ratings yet

- Electronic Engineering Applications of Two–Port Networks: Applied Electricity and Electronics DivisionFrom EverandElectronic Engineering Applications of Two–Port Networks: Applied Electricity and Electronics DivisionNo ratings yet

- Statistical Methods in Food and Consumer ResearchFrom EverandStatistical Methods in Food and Consumer ResearchRating: 5 out of 5 stars5/5 (1)

- Topics in Engineering Logic: International Series of Monographs on Electronics and InstrumentationFrom EverandTopics in Engineering Logic: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- Effectiveness of Using Blended LearningDocument7 pagesEffectiveness of Using Blended LearningIshfaq AhmadNo ratings yet

- TADA REMUNERATION CLAIM With Breakup (NAVTTC) - 3Document1 pageTADA REMUNERATION CLAIM With Breakup (NAVTTC) - 3Ishfaq AhmadNo ratings yet

- EE-241 Basic Electronics, Weekly Lecture Plan: Mid Term ExamDocument1 pageEE-241 Basic Electronics, Weekly Lecture Plan: Mid Term ExamIshfaq AhmadNo ratings yet

- One Page Monitoring FormatDocument2 pagesOne Page Monitoring FormatIshfaq AhmadNo ratings yet

- Jeac PDFDocument13 pagesJeac PDFIshfaq AhmadNo ratings yet

- Quiz 4 - Attempt Review1Document10 pagesQuiz 4 - Attempt Review1Ishfaq AhmadNo ratings yet

- Registration No. Name Gender Date of BirthDocument19 pagesRegistration No. Name Gender Date of BirthIshfaq AhmadNo ratings yet

- Mid Term PDFDocument2 pagesMid Term PDFIshfaq AhmadNo ratings yet

- IT-5170 Stepper MotorDocument17 pagesIT-5170 Stepper MotorIshfaq AhmadNo ratings yet

- Quiz 2Document1 pageQuiz 2Ishfaq AhmadNo ratings yet

- Quiz 1 (CLO-1) : Fall 2017 CS-111 Computer FundamentalsDocument2 pagesQuiz 1 (CLO-1) : Fall 2017 CS-111 Computer FundamentalsIshfaq AhmadNo ratings yet

- Course Folder FormatDocument39 pagesCourse Folder FormatIshfaq AhmadNo ratings yet

- Quiz 2Document1 pageQuiz 2Ishfaq AhmadNo ratings yet

- 7 BS EE-Enrollment 2011Document6 pages7 BS EE-Enrollment 2011Ishfaq AhmadNo ratings yet

- Igat-Ee: Total Questions (MCQS) 100 Total Test Time 150 Minutes (2.5 Hours)Document1 pageIgat-Ee: Total Questions (MCQS) 100 Total Test Time 150 Minutes (2.5 Hours)Ishfaq AhmadNo ratings yet

- Course Outline - Electrical machines-IIDocument3 pagesCourse Outline - Electrical machines-IIIshfaq AhmadNo ratings yet

- Teaching StylesDocument14 pagesTeaching StylesIshfaq AhmadNo ratings yet

- Teaching StylesDocument13 pagesTeaching StylesIshfaq AhmadNo ratings yet

- Guidance For Life HereafterDocument24 pagesGuidance For Life HereafterIshfaq AhmadNo ratings yet

- Lecture 10Document10 pagesLecture 10amanterefe99No ratings yet

- IAT-II Question Paper With Solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H PDFDocument10 pagesIAT-II Question Paper With Solution of 15EC53 Verilog HDL Nov-2017 - Sunil Kumar K.H PDFKavyashreeMNo ratings yet

- Basic Verilog Programs FileDocument33 pagesBasic Verilog Programs FileDaniel Anderson72% (18)

- Questions and Answers On Multiplexers: MultiplexerDocument2 pagesQuestions and Answers On Multiplexers: MultiplexerGopikaNo ratings yet

- Processor DP ControlDocument44 pagesProcessor DP ControlNonex IstantNo ratings yet

- Home Assgn4 BEE 3BCDocument4 pagesHome Assgn4 BEE 3BCDaniyal Yasin0% (1)

- SKEE2263 Mini Project GuideDocument39 pagesSKEE2263 Mini Project GuideÎQbãl HãikãmNo ratings yet

- DatatakerDocument40 pagesDatatakerYuniet Diaz LazoNo ratings yet

- Computer Awareness 4000 MCQDocument83 pagesComputer Awareness 4000 MCQAryanNo ratings yet

- VHDL ProgrammingDocument92 pagesVHDL ProgrammingDavid GoliathNo ratings yet

- Thesis On Content Addressable MemoryDocument8 pagesThesis On Content Addressable Memorykristilucaspittsburgh100% (1)

- Siemens FMX 5Document66 pagesSiemens FMX 5Nicolaie Nicusor100% (1)

- Xapp795 Driving XadcDocument16 pagesXapp795 Driving XadcRicardo Alonso Muñoz CanalesNo ratings yet

- SV1P1 ServiceDocument514 pagesSV1P1 ServiceRamon Johnson100% (1)

- VLSI Questions Answers r3Document79 pagesVLSI Questions Answers r3Gowtham HariNo ratings yet

- Encoders and Decoders, Multiplexer, Tri-State InverterDocument25 pagesEncoders and Decoders, Multiplexer, Tri-State InverterRohit SainiNo ratings yet

- BTL Logic Design Lab Manual 10ESL38 3rd Sem 2011Document67 pagesBTL Logic Design Lab Manual 10ESL38 3rd Sem 2011Manjunath JiNo ratings yet

- Chap 3 Combinational Logic CircuitsDocument98 pagesChap 3 Combinational Logic Circuitsvinay.niranjan006No ratings yet

- 74 Ls 139Document8 pages74 Ls 139vikasyadav123No ratings yet

- Chapter 4 Combinational LogicDocument67 pagesChapter 4 Combinational LogicAbaid UllahNo ratings yet

- Lec Verilog TrafficLight SynthesisDocument32 pagesLec Verilog TrafficLight SynthesisKartikey ManchandaNo ratings yet

- 045 2010Document60 pages045 2010tanishq malikNo ratings yet

- FirstYear-LP (First Semester)Document30 pagesFirstYear-LP (First Semester)Win MyoNo ratings yet

- DFTDocument4 pagesDFTkienukiru100% (1)

- Digital ElectronicsDocument20 pagesDigital Electronics1balamanianNo ratings yet

- Lab 4Document5 pagesLab 4Khemraj MahadewNo ratings yet

- DLD CEL-120 Lab ManualDocument65 pagesDLD CEL-120 Lab ManualMalik Tauqeer Hussain0% (2)

- Mechatronics Main ProjectDocument20 pagesMechatronics Main ProjectAbdi YizotawNo ratings yet