Professional Documents

Culture Documents

Vanteddu Sai Kiran Reddy: Mtech Microelectronics at Iiit-Allahabad

Uploaded by

Sai Kiran Reddy VantedduOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Vanteddu Sai Kiran Reddy: Mtech Microelectronics at Iiit-Allahabad

Uploaded by

Sai Kiran Reddy VantedduCopyright:

Available Formats

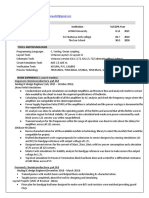

VANTEDDU SAI

KIRAN REDDY

MTech Microelectronics at IIIT-Allahabad

saikiran-reddy-12839b197 Hyderabad, India

(+91) 8668460188 saikiranr3ddy@gmail.com

PROJECTS SKILLS

Top Skills Analog Design and layout, RTL Coding,

Design of a two-stage OP-AMP using UMC 180nm Technology Digital, stability analysis, signals and system

• Two stages OP-AMP with Gain=62dB, GBW=30 MHz, PM=60, Slew rate= 20v/us

power dissipation 0.3mW. Designed and simulated in Cadence Virtuoso using

UMC 180nm technology. Tools and Tech. Xilinx Vivado, Cadence Virtuoso,

Calibre & HSpice, Synopsys DC, LT-Spice

Design and Simulate of Bandgap reference Circuit (BGR) using UMC

180nm Technology Prog. & Protocol Verilog, C/C++, MATLAB, Unix Shell

• Design Current mirror-based Bandgap Voltage reference circuit with start-up circuit

(Temp range -20°C to 140°C, Vout= 1.154v, well curve voltage = 0.015v, Vdd

=1.8v) with Cadence Virtuoso, LT-Spice Also design 1v Sub BGR circuit

Skills ASIC Design Flow, Analog Design Flow,

Design Low Voltage, High PSRR, Low Dropout Voltage Regulator Logic Synthesis, Physical Design Flow Static

(LDO) Time Analysis.

• LDO work on (0.95v < Vin < 2.4v, Vout= 0.900v, PSRR@ 100KHz= 60dB, Cload

=10u with Rser=1ohm, Max load current 50ma, load regulation =0.083%, Line

regulation=1.2%, Current Efficiency= 98.5%) EDUCATION

Design and Implementation of folded and telescopic amplifier in 180nm

technology. MTech Microelectronics

IIIT, Allahabad

Design and Implement, 32 Bit RISC processor using Verilog

August 19 – June 21 CGPA- 7.5

• Implemented 32-bit RISC Architecture based processor with and without pipeline

Architecture Courses are taken: Intro. of Microelectronics, Digital VLSI Design,

• Implemented R-type, J-type, I-type Instruction set Architecture (ISA) Programming for Eng. Application, Analog VLSI Design, Embedded

Systems, Testing, and Verification, Hardware Design Methodologies,

Design fully Synthesized synchronous FIFO design VLSI IC Technology, Mix IC Design, MEMS.

• synchronous FIFO using Queue data structure, with the help of

binary pointer.

Btech Electronic system Engineering

MTECH THESIS NIELIT, Aurangabad

July 14 – June 18 7.6

LDO for SOC applications in 65nm

• working on fast transients, low load regulation, high PSRR value. Intermediate

• With the use of internal compensation techniques (work in Board of Intermediate Education Andhra Pradesh

July 12 – May 14 96.10 %

progress)

Matriculation

Board of secondary Education Andhra Pradesh

July 11 – June 12 9.5

You might also like

- MDC Ba 101 76Document190 pagesMDC Ba 101 76Marc MP100% (1)

- Monika NIT Kurukshetra June 2021 PDFDocument3 pagesMonika NIT Kurukshetra June 2021 PDFS KkNo ratings yet

- Automation Engineer ResumeDocument4 pagesAutomation Engineer ResumeMahesh VermaNo ratings yet

- VishalYadav (0 0)Document1 pageVishalYadav (0 0)Ronnit ShuklaNo ratings yet

- Hariss Jamal BhuttaDocument1 pageHariss Jamal BhuttaHamzah NaeemNo ratings yet

- ECE Undergrad Resume - Shivam GuptaDocument1 pageECE Undergrad Resume - Shivam GuptashivkumarNo ratings yet

- 233170581-Resume-Ygsairaghu-NitWarangalDocument2 pages233170581-Resume-Ygsairaghu-NitWarangalanshuman27.svnitNo ratings yet

- Sradha M (RESUME) - QualcommDocument1 pageSradha M (RESUME) - Qualcommskrxbbr7nhNo ratings yet

- Gandhi Rajan's ResumeDocument1 pageGandhi Rajan's ResumePrit GalaNo ratings yet

- Basit Mahmood: ObjectiveDocument2 pagesBasit Mahmood: ObjectivebasitNo ratings yet

- D A Navaneeth Reddy - PD - CVDocument2 pagesD A Navaneeth Reddy - PD - CVRahul Rahul KNo ratings yet

- Bathini AravindDocument2 pagesBathini AravindSantosh EswarappaNo ratings yet

- Awneeppandey - Memory Design Engineer - IIT BHUDocument2 pagesAwneeppandey - Memory Design Engineer - IIT BHUawneepNo ratings yet

- VLSI Engineer Seeking Circuit Design RolesDocument2 pagesVLSI Engineer Seeking Circuit Design RolesSai RaghuNo ratings yet

- ResumeDocument2 pagesResumeSathvik SNo ratings yet

- Nitesh CVDocument2 pagesNitesh CVpatil.nitesh9211No ratings yet

- Hammer Energy Measurement Apparatus: Instrumented RodDocument2 pagesHammer Energy Measurement Apparatus: Instrumented RodAnbazhagan PanjamaniNo ratings yet

- Akash Kumar IITMandiDocument1 pageAkash Kumar IITMandib21215No ratings yet

- Arif Ihtisham CVDocument2 pagesArif Ihtisham CVIHTISHAM ARIFNo ratings yet

- Resume Srinivasa GadigatlaDocument3 pagesResume Srinivasa GadigatlasgadigatNo ratings yet

- Nitesh CV8Document2 pagesNitesh CV8patil.nitesh9211No ratings yet

- Mani ResumeDocument4 pagesMani ResumeDurairajan AasaithambaiNo ratings yet

- Ruby Krishna. S: ObjectiveDocument5 pagesRuby Krishna. S: ObjectiveRubykrishna SankaranNo ratings yet

- ResumeDocument2 pagesResumeArnab DuttaNo ratings yet

- Nikhil Balgovind Shah's 20+ Years Physical Design ExperienceDocument3 pagesNikhil Balgovind Shah's 20+ Years Physical Design ExperienceBunti KumarNo ratings yet

- Abhilash Betanamudi: AchievementsDocument3 pagesAbhilash Betanamudi: AchievementsAbhilashBetanamudiNo ratings yet

- Core 3Document2 pagesCore 3RidhiNo ratings yet

- Oham Ondal: XperienceDocument2 pagesOham Ondal: XperienceKuch BhiNo ratings yet

- Ruby Krishna S Resume - Analog VLSI EngineerDocument5 pagesRuby Krishna S Resume - Analog VLSI EngineerRubykrishna SankaranNo ratings yet

- Sonalgupta ResumeDocument2 pagesSonalgupta Resumeapi-376821519No ratings yet

- Feroz Choudhary: Profile SummaryDocument5 pagesFeroz Choudhary: Profile SummaryFeroz AhmedNo ratings yet

- Resume Yogesh VermaDocument2 pagesResume Yogesh VermaKalpana VermaNo ratings yet

- AkEmbedded2021 3Document1 pageAkEmbedded2021 3Krishnan ApkNo ratings yet

- Sop For MSDocument2 pagesSop For MSSaiGoutham SunkaraNo ratings yet

- Resume TemplateDocument1 pageResume TemplatePrajwal PrabhuNo ratings yet

- Resume TemplateDocument1 pageResume TemplatePrajwal PrabhuNo ratings yet

- Ghayoor A. Awan: EducationDocument1 pageGhayoor A. Awan: EducationKHAWAJA ACADEMYNo ratings yet

- Research Notes On VlsiDocument70 pagesResearch Notes On VlsiMohit GirdharNo ratings yet

- Ahsan Ali BS Electronic EngineeringDocument1 pageAhsan Ali BS Electronic EngineeringR Ali ChaudhryNo ratings yet

- Resume V23.2 PDFDocument4 pagesResume V23.2 PDFhemantsinh22No ratings yet

- Sarfraz Anwar's Electrical Engineering ProfileDocument2 pagesSarfraz Anwar's Electrical Engineering ProfileSarfrazAnwarNo ratings yet

- Nithin S Poduval - Resume4Document1 pageNithin S Poduval - Resume4Nithin PoduvalNo ratings yet

- Sri Balaji Resume-Full TimeDocument2 pagesSri Balaji Resume-Full TimeJate NirmalNo ratings yet

- Resume TemplateDocument1 pageResume TemplatePrajwal PrabhuNo ratings yet

- Ashish Kumar Mishra: HighlightsDocument2 pagesAshish Kumar Mishra: Highlightsjagendra singhNo ratings yet

- ECE Graduate with Skills in Antenna Design, Embedded Systems and ProgrammingDocument1 pageECE Graduate with Skills in Antenna Design, Embedded Systems and ProgrammingAmit PrajapatiNo ratings yet

- FINALVERSIONDocument24 pagesFINALVERSIONSummer TriangleNo ratings yet

- K Triveni's VLSI career objective and experienceDocument3 pagesK Triveni's VLSI career objective and experienceTriveni KNo ratings yet

- Manoj HP: ObjectiveDocument4 pagesManoj HP: ObjectivePranav NarayanNo ratings yet

- Nouveau Microsoft Excel WorksheetDocument23 pagesNouveau Microsoft Excel WorksheetAhMadi OuaSsimNo ratings yet

- Curriculum Vitae: Career ObjectiveDocument5 pagesCurriculum Vitae: Career Objectivenareshpaluru100% (1)

- Verified The Logic of Scan-Chain and LFSR Using Verilog Code. Calculated The Area Over-Head For Scan-ChainDocument2 pagesVerified The Logic of Scan-Chain and LFSR Using Verilog Code. Calculated The Area Over-Head For Scan-ChainSiddharthSharmaNo ratings yet

- Mounika's Resume - Analog IC Design EngineerDocument3 pagesMounika's Resume - Analog IC Design Engineermounika morampudiNo ratings yet

- Microsoft Word - SIGMA 2018 - 6!6!2017Document2 pagesMicrosoft Word - SIGMA 2018 - 6!6!2017er_aman11No ratings yet

- Naresh ResumeDocument1 pageNaresh ResumeIT Jobs IndiaNo ratings yet

- Sistem Tertanam (Pendahuluan)Document11 pagesSistem Tertanam (Pendahuluan)Laura TampubolonNo ratings yet

- Resume TemplateDocument1 pageResume TemplatePrajwal PrabhuNo ratings yet

- Eecs 2017 10 PDFDocument82 pagesEecs 2017 10 PDFSuraj Kumar PrustyNo ratings yet

- Arjun Singh Senior Software EngineerDocument3 pagesArjun Singh Senior Software EngineerErArjun Singh SisodiyaNo ratings yet

- Lakshmi Narasimhan Ramakrishnan ResumeDocument2 pagesLakshmi Narasimhan Ramakrishnan ResumerlnmanirlnNo ratings yet

- DSD Notes c1Document14 pagesDSD Notes c1Sai Kiran Reddy VantedduNo ratings yet

- ChallanDocument1 pageChallanSai Kiran Reddy VantedduNo ratings yet

- M.Tech Application: Personal InformationDocument2 pagesM.Tech Application: Personal InformationSai Kiran Reddy VantedduNo ratings yet

- Ultra Low Power Multiplexer Using CMOS VariationsDocument15 pagesUltra Low Power Multiplexer Using CMOS VariationsSai Kiran Reddy VantedduNo ratings yet

- Updated Placement Detailed 2017-2018Document2 pagesUpdated Placement Detailed 2017-2018Sai Kiran Reddy VantedduNo ratings yet

- Electronic Devices and Circuits C2 Review TestDocument5 pagesElectronic Devices and Circuits C2 Review TestSai Kiran Reddy VantedduNo ratings yet

- Ultra Low Power Multiplexer Using CMOS VariationsDocument15 pagesUltra Low Power Multiplexer Using CMOS VariationsSai Kiran Reddy VantedduNo ratings yet

- JRF ApplicationDocument1 pageJRF ApplicationSai Kiran Reddy VantedduNo ratings yet

- Design of Low Dropout Voltage Regulator For Soc ApplicationsDocument65 pagesDesign of Low Dropout Voltage Regulator For Soc ApplicationsSai Kiran Reddy VantedduNo ratings yet

- Design and Analysis of Voltage-Programmed Pixel Circuits For Flexible Amoled DisplaysDocument27 pagesDesign and Analysis of Voltage-Programmed Pixel Circuits For Flexible Amoled DisplaysSai Kiran Reddy VantedduNo ratings yet

- Low Dropout Voltage Regulator For System-On-Chip (Soc) ApplicationsDocument19 pagesLow Dropout Voltage Regulator For System-On-Chip (Soc) ApplicationsSai Kiran Reddy VantedduNo ratings yet

- IeeeDocument4 pagesIeeeSai Kiran Reddy VantedduNo ratings yet

- Hardware Design Methodology: Timing Analysis of Sequential CircuitsDocument17 pagesHardware Design Methodology: Timing Analysis of Sequential CircuitsSai Kiran Reddy VantedduNo ratings yet

- Electronic Devices and Circuits: C3 Review Test: Date: 14/07/2021 Scaled MM 40 Duration: 2 HrsDocument5 pagesElectronic Devices and Circuits: C3 Review Test: Date: 14/07/2021 Scaled MM 40 Duration: 2 HrsSai Kiran Reddy VantedduNo ratings yet

- DSD Ieee Paper PDFDocument5 pagesDSD Ieee Paper PDFSai Kiran Reddy VantedduNo ratings yet

- LicenseDocument1 pageLicenseSai Kiran Reddy VantedduNo ratings yet

- Read MeDocument1 pageRead MeSourav SharmaNo ratings yet

- 3 ARM ExceptionsDocument26 pages3 ARM ExceptionsSaket JainNo ratings yet

- Memory Devices, Circuits, and Subsystem Design: 9.1 Program and Data StorageDocument13 pagesMemory Devices, Circuits, and Subsystem Design: 9.1 Program and Data Storagesai420No ratings yet

- AutoMountRemoveUSB DriveDocument2 pagesAutoMountRemoveUSB DriveDiegoPepeusNo ratings yet

- Pic 24Document371 pagesPic 24alin0604No ratings yet

- BQ24728 Datasheet PDFDocument42 pagesBQ24728 Datasheet PDFMiguel Sierra50% (2)

- Technical Data Sheet: NIR-Online Multipoint SystemDocument8 pagesTechnical Data Sheet: NIR-Online Multipoint SystemPiee SyafieNo ratings yet

- User Guide: The Upgrade Kit Is Compatible With Playstation®5Document15 pagesUser Guide: The Upgrade Kit Is Compatible With Playstation®5Edy ArquemanNo ratings yet

- CH04 COA9e.en - IdDocument46 pagesCH04 COA9e.en - IdKha KimNo ratings yet

- Module 001 Introduction To Computers: Lesson 1: Computer BasicsDocument11 pagesModule 001 Introduction To Computers: Lesson 1: Computer BasicsTriciaNo ratings yet

- PLC Rockwell CatalogueDocument5 pagesPLC Rockwell Cataloguehuynh ngoc hoi HuynhNo ratings yet

- Digital Testing: Key Concepts of Scan-Path DesignDocument54 pagesDigital Testing: Key Concepts of Scan-Path DesignaguohaqdoNo ratings yet

- Setup LogDocument216 pagesSetup LogMisteri JongNo ratings yet

- d0cc d0cd D0ce Aa Kor IndDocument177 pagesd0cc d0cd D0ce Aa Kor IndHoang Minh Pham NguyenNo ratings yet

- Tejas Micro 1 RTU Technical ManualDocument110 pagesTejas Micro 1 RTU Technical ManualAlex ProchotNo ratings yet

- Computer Merit Badge: September 2002 Tom Foss 322-1434Document46 pagesComputer Merit Badge: September 2002 Tom Foss 322-1434pRiNcE DuDhAtRaNo ratings yet

- Model Paralel ProsesorDocument12 pagesModel Paralel ProsesorKompetisi UI UXNo ratings yet

- 7 Series Fpgas Data Sheet: Overview: General DescriptionDocument18 pages7 Series Fpgas Data Sheet: Overview: General DescriptionPraveen MeduriNo ratings yet

- Hardware and Software PersuasiveDocument16 pagesHardware and Software PersuasivemaaNo ratings yet

- ASUS Product Guide Spring Summer 2010 PDFDocument24 pagesASUS Product Guide Spring Summer 2010 PDFwkfzarNo ratings yet

- Slyt416 Ecg EegDocument18 pagesSlyt416 Ecg EegsakthyinNo ratings yet

- DD&CO QBANK (Vtu23)Document3 pagesDD&CO QBANK (Vtu23)manjufk456No ratings yet

- Nexys4-DDR RMDocument29 pagesNexys4-DDR RMDocente Fede TecnologicoNo ratings yet

- Finalise Group IMS 552Document34 pagesFinalise Group IMS 552irmiiswa amirNo ratings yet

- Lenovo Diagnostics Log Reveals Battery IssueDocument11 pagesLenovo Diagnostics Log Reveals Battery IssueSalmanNo ratings yet

- Automated Shopping Trolley For Billing SystemDocument5 pagesAutomated Shopping Trolley For Billing SystemIJIRSTNo ratings yet

- UART Implementation Using FPGA: December 2019Document50 pagesUART Implementation Using FPGA: December 2019V.ASHISH REDDYNo ratings yet

- Tarpapel Bahagi NG Kompyuter LectureDocument45 pagesTarpapel Bahagi NG Kompyuter LectureMark Anthony CollargaNo ratings yet

- Volume CDocument2 pagesVolume CKadal IjoNo ratings yet

- NetApp Data ONTAP 8.0 Cluster-Mode Data SheetDocument4 pagesNetApp Data ONTAP 8.0 Cluster-Mode Data SheeteacsmediaNo ratings yet