Professional Documents

Culture Documents

Atmel 0036

Uploaded by

namerOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Atmel 0036

Uploaded by

namerCopyright:

Available Formats

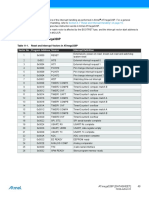

9.

6 Power-save Mode

When the SM2..0 bits are written to 011, the SLEEP instruction makes the MCU enter power-save mode. This mode is

identical to power-down, with one exception:

If Timer/Counter2 is enabled, it will keep running during sleep. The device can wake up from either timer overflow or output

compare event from Timer/Counter2 if the corresponding Timer/Counter2 interrupt enable bits are set in TIMSK2, and the

global interrupt enable bit in SREG is set.

If Timer/Counter2 is not running, power-down mode is recommended instead of power-save mode.

The Timer/Counter2 can be clocked both synchronously and asynchronously in power-save mode. If Timer/Counter2 is not

using the asynchronous clock, the Timer/Counter oscillator is stopped during sleep. If Timer/Counter2 is not using the

synchronous clock, the clock source is stopped during sleep. Note that even if the synchronous clock is running in

power-save, this clock is only available for Timer/Counter2.

9.7 Standby Mode

When the SM2..0 bits are 110 and an external crystal/resonator clock option is selected, the SLEEP instruction makes the

MCU enter standby mode. This mode is identical to power-down with the exception that the oscillator is kept running. from

standby mode, the device wakes up in six clock cycles.

9.8 Extended Standby Mode

When the SM2..0 bits are 111 and an external crystal/resonator clock option is selected, the SLEEP instruction makes the

MCU enter extended standby mode. This mode is identical to power-save with the exception that the oscillator is kept

running. From extended standby mode, the device wakes up in six clock cycles.

9.9 Power Reduction Register

The power reduction register (PRR), see Section 9.11.3 “PRR – Power Reduction Register” on page 38, provides a method

to stop the clock to individual peripherals to reduce power consumption. The current state of the peripheral is frozen and the

I/O registers can not be read or written. Resources used by the peripheral when stopping the clock will remain occupied,

hence the peripheral should in most cases be disabled before stopping the clock. Waking up a module, which is done by

clearing the bit in PRR, puts the module in the same state as before shutdown.

Module shutdown can be used in Idle mode and active mode to significantly reduce the overall power consumption. In all

other sleep modes, the clock is already stopped.

9.10 Minimizing Power Consumption

There are several possibilities to consider when trying to minimize the power consumption in an AVR® controlled system. In

general, sleep modes should be used as much as possible, and the sleep mode should be selected so that as few as

possible of the device’s functions are operating. All functions not needed should be disabled. In particular, the following

modules may need special consideration when trying to achieve the lowest possible power consumption.

9.10.1 Analog to Digital Converter

If enabled, the ADC will be enabled in all sleep modes. To save power, the ADC should be disabled before entering any

sleep mode. When the ADC is turned off and on again, the next conversion will be an extended conversion. Refer to Section

23. “Analog-to-Digital Converter” on page 205 for details on ADC operation.

9.10.2 Analog Comparator

When entering Idle mode, the analog comparator should be disabled if not used. When entering ADC noise reduction mode,

the analog comparator should be disabled. In other sleep modes, the analog comparator is automatically disabled. However,

if the analog comparator is set up to use the internal voltage reference as input, the analog comparator should be disabled in

all sleep modes. Otherwise, the internal voltage reference will be enabled, independent of sleep mode. Refer to Section 22.

“Analog Comparator” on page 202 for details on how to configure the analog comparator.

36 ATmega328P [DATASHEET]

7810D–AVR–01/15

You might also like

- 9.2 Bod Disable: 35 Atmega328P (Datasheet)Document1 page9.2 Bod Disable: 35 Atmega328P (Datasheet)namerNo ratings yet

- Atmel 0037Document1 pageAtmel 0037namerNo ratings yet

- Power ModeDocument15 pagesPower ModeFenni Kristiani SarumahaNo ratings yet

- ResetDocument17 pagesResetVictor DiazNo ratings yet

- Nota de Aplicacion - PicoPower BasicsDocument7 pagesNota de Aplicacion - PicoPower Basicsgusti072No ratings yet

- Atmel 42142 SAM AT03258 Using Low Power Mode in SAM4E Microcontroller - Application NoteDocument13 pagesAtmel 42142 SAM AT03258 Using Low Power Mode in SAM4E Microcontroller - Application NoteReinNo ratings yet

- BLHeli - 32 Manual ARM Rev32.xDocument15 pagesBLHeli - 32 Manual ARM Rev32.xDavid LuñoNo ratings yet

- ATmega Power DownDocument3 pagesATmega Power DownagunxwibowoNo ratings yet

- Am116a ManualDocument11 pagesAm116a Manualyusufemirsamuk74ysNo ratings yet

- ESC ManualDocument3 pagesESC ManualHarold GulbisNo ratings yet

- BLHeli - 32 Manual ARM Rev32.xDocument18 pagesBLHeli - 32 Manual ARM Rev32.xriskyNo ratings yet

- STM32G4-System-Power Control PWRDocument47 pagesSTM32G4-System-Power Control PWRMax INo ratings yet

- AIM2 Stm32 Programming GuideDocument9 pagesAIM2 Stm32 Programming Guidesyawal75No ratings yet

- BLHeli - 32 Manual ARM Rev32.xDocument18 pagesBLHeli - 32 Manual ARM Rev32.xRonaldo PassanhaNo ratings yet

- XR80CX GB r1.2 27.03.2015Document4 pagesXR80CX GB r1.2 27.03.2015Jennifer Eszter SárközyNo ratings yet

- Watch Dog Timer and Sleep ModeDocument1 pageWatch Dog Timer and Sleep ModeMANIKANDANNo ratings yet

- Rotork Black Liquor Rev 6Document26 pagesRotork Black Liquor Rev 6Yrty KdfgNo ratings yet

- ASTAT Plus Manual PDFDocument35 pagesASTAT Plus Manual PDFJesús Martin V MinayaNo ratings yet

- AN5425 - Transfer Power ModeDocument28 pagesAN5425 - Transfer Power ModeAn TânNo ratings yet

- Future XLP ArticleDocument2 pagesFuture XLP ArticleOsama DurmusNo ratings yet

- Panel BacklightingDocument20 pagesPanel BacklightingEckard GuendelNo ratings yet

- Manual Mystery ESCDocument8 pagesManual Mystery ESCdruidhanetNo ratings yet

- Course: Microcontrollers and Interfacing Module: 2 - MSP430 Topic: Power Down Modes Faculty: MR R Sarath KumarDocument28 pagesCourse: Microcontrollers and Interfacing Module: 2 - MSP430 Topic: Power Down Modes Faculty: MR R Sarath Kumargokul kNo ratings yet

- Xsel KT Ket (Me0134 10b)Document436 pagesXsel KT Ket (Me0134 10b)bambangNo ratings yet

- Power Saving Schemes of The ARM CORETX M3Document3 pagesPower Saving Schemes of The ARM CORETX M3kumarklNo ratings yet

- Clock and Fuses: Prof. Prabhat Ranjan Dhirubhai Ambani Institute of Information and Communication Technology, GandhinagarDocument39 pagesClock and Fuses: Prof. Prabhat Ranjan Dhirubhai Ambani Institute of Information and Communication Technology, Gandhinagarpuneet0191No ratings yet

- NearZero - Quick Start and Manual - Firmware v2.0Document10 pagesNearZero - Quick Start and Manual - Firmware v2.0Deniz Melek TürkNo ratings yet

- BatteryDocument2 pagesBatteryNicholas AndersonNo ratings yet

- Setting Guide EOCRDocument3 pagesSetting Guide EOCRBambangsNo ratings yet

- Rotork Actuator Guide for Black Liquor Recovery BoilersDocument26 pagesRotork Actuator Guide for Black Liquor Recovery BoilersLeonardo Silva SilvaNo ratings yet

- Functional Range: EC 2: AMF RelayDocument20 pagesFunctional Range: EC 2: AMF RelayChandrashekhar UpparNo ratings yet

- Ds Manual Astat Plus Spain v2005Document35 pagesDs Manual Astat Plus Spain v2005dipcaeNo ratings yet

- Proflo Lubricator Monitor Sets Alarm for No FlowDocument10 pagesProflo Lubricator Monitor Sets Alarm for No FlowJeff LNo ratings yet

- Automatic Engine Control Unit Operators ManualDocument11 pagesAutomatic Engine Control Unit Operators ManualAhmad ArpaniNo ratings yet

- 2003apr25 Id MPR AnDocument12 pages2003apr25 Id MPR AnMohamedSalahNo ratings yet

- XR80C - XR80D: Milk Tank ControllersDocument4 pagesXR80C - XR80D: Milk Tank ControllersJennifer Eszter SárközyNo ratings yet

- BLHeli - 32 Manual ARM Rev32.x PDFDocument10 pagesBLHeli - 32 Manual ARM Rev32.x PDFaniket5941No ratings yet

- Esc YEP 150ADocument2 pagesEsc YEP 150AAltemarFernandesdeOliveiraNo ratings yet

- AT89C2051 Traffic Light ControllerDocument39 pagesAT89C2051 Traffic Light ControllerNagesh RayNo ratings yet

- Atmel 0043Document1 pageAtmel 0043namerNo ratings yet

- How To Megasquirt Your 2nd Gen RXDocument21 pagesHow To Megasquirt Your 2nd Gen RXChevy GorbachevNo ratings yet

- Automatic Engine Control Unit Operators Manual: Kutai Electronics Industry Co., LTDDocument11 pagesAutomatic Engine Control Unit Operators Manual: Kutai Electronics Industry Co., LTDalexanderNo ratings yet

- Esc Manualhw 01 v4Document2 pagesEsc Manualhw 01 v4Neil100% (1)

- Navi 7 Istcarb 033011 My 2010 Rev3Document8 pagesNavi 7 Istcarb 033011 My 2010 Rev3JONATHANCGNo ratings yet

- Motor ControlDocument5 pagesMotor ControlnooriusefNo ratings yet

- Agitation Cycle Management MethodsDocument4 pagesAgitation Cycle Management MethodsArvind WaghNo ratings yet

- 04 Delays, Counters, and TimersDocument47 pages04 Delays, Counters, and TimersFatimaAlarconBlancoNo ratings yet

- Unit 3 McuDocument23 pagesUnit 3 McuatulNo ratings yet

- Usblmc Cuh Ipg V1 (4) enDocument22 pagesUsblmc Cuh Ipg V1 (4) enLuis VascoNo ratings yet

- Troubleshooting From I566-E1-02 G (ML2)Document25 pagesTroubleshooting From I566-E1-02 G (ML2)احمدمحمد الخياطNo ratings yet

- Gcu 10 Manual enDocument11 pagesGcu 10 Manual enGhassan ABO ALINo ratings yet

- HW 01 PLDocument2 pagesHW 01 PLJennifer RiceNo ratings yet

- ZIAD Line Master Line Monitor Manual Apr88 OCRDocument33 pagesZIAD Line Master Line Monitor Manual Apr88 OCRBrookeClarkeNo ratings yet

- Astat Plus: GE Power ControlsDocument35 pagesAstat Plus: GE Power ControlsRafael CastilloNo ratings yet

- TD 0034Document2 pagesTD 0034homayoun khosravaniNo ratings yet

- 07 - Manual GC 6000Document33 pages07 - Manual GC 6000Leonardo Rodrigues dos SantosNo ratings yet

- Electronic Speed ControlDocument3 pagesElectronic Speed ControlGaneshkumar Krishna ShettyNo ratings yet

- Automatic Gen.-Set Controller For AMF and Mains Parallel OperationDocument56 pagesAutomatic Gen.-Set Controller For AMF and Mains Parallel Operationdudu_vitoria92% (12)

- 12.2.2 EIMSK - External Interrupt Mask RegisterDocument1 page12.2.2 EIMSK - External Interrupt Mask RegisternamerNo ratings yet

- Atmel 0053Document1 pageAtmel 0053namerNo ratings yet

- Atmel 0052Document1 pageAtmel 0052namerNo ratings yet

- Atmel 0054Document1 pageAtmel 0054namerNo ratings yet

- Atmel 0051Document1 pageAtmel 0051namerNo ratings yet

- Interrupts: 11.1 Interrupt Vectors in Atmega328PDocument1 pageInterrupts: 11.1 Interrupt Vectors in Atmega328PnamerNo ratings yet

- Atmel 0043Document1 pageAtmel 0043namerNo ratings yet

- Bit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisterDocument1 pageBit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisternamerNo ratings yet

- Bootrst Ivsel Reset Address Interrupt Vectors Start AddressDocument1 pageBootrst Ivsel Reset Address Interrupt Vectors Start AddressnamerNo ratings yet

- Atmel 0041Document1 pageAtmel 0041namerNo ratings yet

- 10.9 Register Description: Section 5. "About Code Examples" On Page 8Document1 page10.9 Register Description: Section 5. "About Code Examples" On Page 8namerNo ratings yet

- Bit 3 - WDE: Watchdog System Reset EnableDocument1 pageBit 3 - WDE: Watchdog System Reset EnablenamerNo ratings yet

- Power Management and Sleep ModesDocument1 pagePower Management and Sleep ModesnamerNo ratings yet

- Atmel 0039Document1 pageAtmel 0039namerNo ratings yet

- Atmel 0042Document1 pageAtmel 0042namerNo ratings yet

- Atmel 0038Document1 pageAtmel 0038namerNo ratings yet

- Atmel 0044Document1 pageAtmel 0044namerNo ratings yet

- 8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisterDocument1 page8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisternamerNo ratings yet

- Atmel 0040Document1 pageAtmel 0040namerNo ratings yet

- Atmel 0045Document1 pageAtmel 0045namerNo ratings yet

- Calibrate internal oscillator for higher accuracyDocument1 pageCalibrate internal oscillator for higher accuracynamerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- Atmel 0033Document1 pageAtmel 0033namerNo ratings yet

- 8.8 External Clock: Frequency CKSEL3..0Document1 page8.8 External Clock: Frequency CKSEL3..0namerNo ratings yet

- SlotServer Configuration ManualDocument37 pagesSlotServer Configuration ManualJose SierraNo ratings yet

- Android Interview Cheat Sheet — Part I (29 min readDocument26 pagesAndroid Interview Cheat Sheet — Part I (29 min readNikolett Szabados-SoósNo ratings yet

- Docu53884 PDFDocument13 pagesDocu53884 PDFtesyouNo ratings yet

- Objective C TutorialDocument121 pagesObjective C TutorialDao Nguyen MinhNo ratings yet

- JDBC and Database ApplicationsDocument185 pagesJDBC and Database ApplicationsabhishekNo ratings yet

- ScaNv6 instructorPPT Chapter4Document30 pagesScaNv6 instructorPPT Chapter4sochea domjsNo ratings yet

- IEDScout ExamplesDocument16 pagesIEDScout Examplesbdiaconu20048672100% (1)

- CPI15Document24 pagesCPI15sprasadn66No ratings yet

- Huawei - Datasheet - E9000 Blade ServerDocument16 pagesHuawei - Datasheet - E9000 Blade Servermohammad mizabiNo ratings yet

- Windows Server 2003 R2 Enterprise 64 Bit Free Download - PCappsdadDocument7 pagesWindows Server 2003 R2 Enterprise 64 Bit Free Download - PCappsdadsidharth kumar100% (1)

- 01-19 ERPS (G 8032) ConfigurationDocument82 pages01-19 ERPS (G 8032) ConfigurationMartine OneNo ratings yet

- 7 0 Saa Aix Inst GuideDocument288 pages7 0 Saa Aix Inst GuideRodolfo MilanoNo ratings yet

- 06 Nutiny-Nuc029 PWMDocument25 pages06 Nutiny-Nuc029 PWMDharmendra SavaliyaNo ratings yet

- The Spoken Tutorial ProjectDocument2 pagesThe Spoken Tutorial ProjectDineshNo ratings yet

- Datasheet XPG SX8200 en 20180316Document2 pagesDatasheet XPG SX8200 en 20180316rumi1975No ratings yet

- Fire CS1140 ManualDocument8 pagesFire CS1140 ManualshebabgNo ratings yet

- Setting Dolphin EmulatorDocument3 pagesSetting Dolphin EmulatorFarhanNo ratings yet

- DHCP & DNS Implementation along with PAT ConfigurationDocument28 pagesDHCP & DNS Implementation along with PAT ConfigurationKoushik Q SarkarNo ratings yet

- BADI - MATERIAL - CHECK Which Can Be Use For Our RequirementDocument5 pagesBADI - MATERIAL - CHECK Which Can Be Use For Our RequirementRupakbhattacNo ratings yet

- Delta - Ia Hmi - Dop B10S411 S511 E515 - Q - TC en SC Tur - 20160714 PDFDocument8 pagesDelta - Ia Hmi - Dop B10S411 S511 E515 - Q - TC en SC Tur - 20160714 PDFMohsin JunejaNo ratings yet

- Computer Architecture and OrganizationDocument2 pagesComputer Architecture and OrganizationShah HussainNo ratings yet

- What Is RMANDocument6 pagesWhat Is RMANsaravanand1983No ratings yet

- Juj 103 - Literasi KomputerDocument8 pagesJuj 103 - Literasi KomputerAdnnyl NnymNo ratings yet

- HDL Lab Manual For VTU Syllabus (10ECL48)Document64 pagesHDL Lab Manual For VTU Syllabus (10ECL48)Ravikiran B A100% (4)

- 5 Capacity PlanningDocument35 pages5 Capacity PlanninginderNo ratings yet

- RTU FAT Test Book for Lucy RMUDocument15 pagesRTU FAT Test Book for Lucy RMUMallampati RamakrishnaNo ratings yet

- En Productsheet I3sixty RDocument4 pagesEn Productsheet I3sixty RNicoleta NiţăNo ratings yet

- Prashant Resume UpdatedDocument1 pagePrashant Resume UpdatedSharanayya HiremathNo ratings yet

- Tutorial Letter 201/1/2013: Semester 1 COS1512Document14 pagesTutorial Letter 201/1/2013: Semester 1 COS1512Lina Slabbert-van Der WaltNo ratings yet

- 940fn Service ManualDocument66 pages940fn Service Manualnmavor9783No ratings yet