Professional Documents

Culture Documents

Atmel 0044

Uploaded by

namerOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Atmel 0044

Uploaded by

namerCopyright:

Available Formats

10.8.

2 Overview

Atmel® ATmega328P has an enhanced watchdog timer (WDT). The WDT is a timer counting cycles of a separate on-chip

128kHz oscillator. The WDT gives an interrupt or a system reset when the counter reaches a given time-out value. In normal

operation mode, it is required that the system uses the WDR - watchdog timer reset - instruction to restart the counter before

the time-out value is reached. If the system doesn't restart the counter, an interrupt or system reset will be issued.

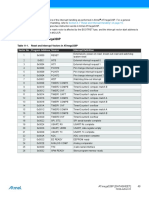

Figure 10-7. Watchdog Timer

128kHz Watchdog

Oscillator Prescaler

OSC/2K

OSC/4K

OSC/8K

OSC/16K

OSC/32K

OSC/64K

OSC/128K

OSC/256K

OSC/512K

OSC/1024K

WDP0

WDP1

WATCHDOG WDP2

RESET WDP3

WDE

MCU RESET

WDIF

INTERRUPT

WDIE

In interrupt mode, the WDT gives an interrupt when the timer expires. This interrupt can be used to wake the device from

sleep-modes, and also as a general system timer. One example is to limit the maximum time allowed for certain operations,

giving an interrupt when the operation has run longer than expected. In system reset mode, the WDT gives a reset when the

timer expires. This is typically used to prevent system hang-up in case of runaway code. The third mode, Interrupt and

system reset mode, combines the other two modes by first giving an interrupt and then switch to system reset mode. This

mode will for instance allow a safe shutdown by saving critical parameters before a system reset.

The watchdog always on (WDTON) fuse, if programmed, will force the watchdog timer to system reset mode. With the fuse

programmed the system reset mode bit (WDE) and interrupt mode bit (WDIE) are locked to 1 and 0 respectively. To further

ensure program security, alterations to the watchdog set-up must follow timed sequences.

The sequence for clearing WDE and changing time-out configuration is as follows:

1. In the same operation, write a logic one to the watchdog change enable bit (WDCE) and WDE. A logic one must

be written to WDE regardless of the previous value of the WDE bit.

2. Within the next four clock cycles, write the WDE and watchdog prescaler bits (WDP) as desired, but with the

WDCE bit cleared. This must be done in one operation.

44 ATmega328P [DATASHEET]

7810D–AVR–01/15

You might also like

- Atmega 2560 Ingles (061-090)Document30 pagesAtmega 2560 Ingles (061-090)Yovan MamaniNo ratings yet

- Clocking Reference SystemDocument21 pagesClocking Reference SystemrashbronNo ratings yet

- 25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118Document39 pages25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118ManunoghiNo ratings yet

- 25AA640A/25LC640A: 64K SPI Bus Serial EEPROMDocument36 pages25AA640A/25LC640A: 64K SPI Bus Serial EEPROMmarino246No ratings yet

- X5328, X5329 (Replaces X25328, X25329) : CPU Supervisor With 32kbit SPI EEPROMDocument21 pagesX5328, X5329 (Replaces X25328, X25329) : CPU Supervisor With 32kbit SPI EEPROMRisoSilvaNo ratings yet

- 2.5V To 6.0V Micropower CMOS Op Amp: FeaturesDocument32 pages2.5V To 6.0V Micropower CMOS Op Amp: FeaturesJuan Carlos Ramirez FuentesNo ratings yet

- A-Data: Synchronous DRAM 1M X 16 Bit X 4 Banks General Description FeaturesDocument9 pagesA-Data: Synchronous DRAM 1M X 16 Bit X 4 Banks General Description FeaturesJim LiebNo ratings yet

- W49f002u 12BDocument28 pagesW49f002u 12BUniversidad Tecnológica De TorreónNo ratings yet

- 2 (1) M Words X 8 (16) Bits X 4 Banks (64-MBIT) Synchronous Dynamic RamDocument68 pages2 (1) M Words X 8 (16) Bits X 4 Banks (64-MBIT) Synchronous Dynamic RamФат Хыу НгуенNo ratings yet

- Datashet Etron TechDocument54 pagesDatashet Etron TechAndres OrjuelaNo ratings yet

- Data SheetDocument102 pagesData SheetzzNo ratings yet

- 512m Sdram B Die As4c32m16sb-7tcn-7tin-6tin Rev 1.0 June 2016Document55 pages512m Sdram B Die As4c32m16sb-7tcn-7tin-6tin Rev 1.0 June 2016zaffzero0No ratings yet

- OscillatorDocument36 pagesOscillatorguyihhhNo ratings yet

- Ic PDFDocument36 pagesIc PDFdharamNo ratings yet

- Unit 3 McuDocument23 pagesUnit 3 McuatulNo ratings yet

- 10.9 Register Description: Section 5. "About Code Examples" On Page 8Document1 page10.9 Register Description: Section 5. "About Code Examples" On Page 8namerNo ratings yet

- ddr4 Pi Model PDFDocument18 pagesddr4 Pi Model PDFAnh Viet NguyenNo ratings yet

- U2741BDocument9 pagesU2741BSlavko MitrovicNo ratings yet

- Datasheet ENC28J60Document102 pagesDatasheet ENC28J60alin76usNo ratings yet

- 8K/16K 5.0V Microwire Serial EEPROM: Features: Package TypesDocument20 pages8K/16K 5.0V Microwire Serial EEPROM: Features: Package Typesfarhood ranjbarkhanghahNo ratings yet

- DS1307 PDFDocument14 pagesDS1307 PDFtestzopNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesAbdullah TheNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and Featuresprabu maulanaNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesMuneeb Ahmad NasirNo ratings yet

- DS1307 Reloj TinyRTC DatasheetDocument14 pagesDS1307 Reloj TinyRTC DatasheetDavid Leonardo Higuera CamargoNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and Featuresjames andrewNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesSamirNo ratings yet

- DS1307 I2c Based RTC DatasheetDocument14 pagesDS1307 I2c Based RTC Datasheetnaveen_teja1No ratings yet

- Spi Eeprom PDFDocument44 pagesSpi Eeprom PDFEma HarmaNo ratings yet

- SV6030P Single-Chip 802.11 B/G/N MAC/BB/Radio With SDIO/SPI - SLAVE InterfaceDocument28 pagesSV6030P Single-Chip 802.11 B/G/N MAC/BB/Radio With SDIO/SPI - SLAVE Interfaceapi-432313169No ratings yet

- APW8813/A: Features General DescriptionDocument31 pagesAPW8813/A: Features General DescriptionDanielle ButlerNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesDocument2 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description Benefits and FeaturesSebastian Parsaulian SamosirNo ratings yet

- 128M (8Mx16) GDDR SDRAM: HY5DU281622ETDocument34 pages128M (8Mx16) GDDR SDRAM: HY5DU281622ETBoris LazarchukNo ratings yet

- AK4384 AsahiKaseiMicrosystemsDocument24 pagesAK4384 AsahiKaseiMicrosystemstaninavcoNo ratings yet

- AK93C45A / 55A / 65A / 75A: 1K / 2K / 4K / 8kbit Serial CMOS EEPROMDocument14 pagesAK93C45A / 55A / 65A / 75A: 1K / 2K / 4K / 8kbit Serial CMOS EEPROMmansoorhayatNo ratings yet

- Parallelism (2) & Heterogeneous Computing & Future PerspetivesDocument50 pagesParallelism (2) & Heterogeneous Computing & Future Perspetivesacer smithNo ratings yet

- ch2 3assemblyDocument33 pagesch2 3assemblyChawki WikiNo ratings yet

- TPS51916 Complete DDR2, DDR3, DDR3L and DDR4 Memory Power Solution Synchronous Buck Controller, 2-A LDO, Buffered ReferenceDocument38 pagesTPS51916 Complete DDR2, DDR3, DDR3L and DDR4 Memory Power Solution Synchronous Buck Controller, 2-A LDO, Buffered ReferenceAndhi UznhNo ratings yet

- Multiple Switch Detection Interface With Suppressed Wake-Up: Technical DataDocument32 pagesMultiple Switch Detection Interface With Suppressed Wake-Up: Technical Datakatty cumbeNo ratings yet

- High Level DesignDocument49 pagesHigh Level DesignFortilab FortilabNo ratings yet

- Brkarc 3465Document182 pagesBrkarc 3465astyamixNo ratings yet

- AT25080A, 160A, 320A, 640A Rev04Document23 pagesAT25080A, 160A, 320A, 640A Rev04Bobby HancockNo ratings yet

- 4K, 512 X 8 Bit: FN8126.2 Data Sheet March 16, 2006Document21 pages4K, 512 X 8 Bit: FN8126.2 Data Sheet March 16, 2006Angel LugoNo ratings yet

- 93C86Document20 pages93C86cgmannerheimNo ratings yet

- Myson Technology: MTV212A32 (Rev. 1.2) 8051 Embedded Monitor Controller Mask ROM TypeDocument24 pagesMyson Technology: MTV212A32 (Rev. 1.2) 8051 Embedded Monitor Controller Mask ROM TypeJose Angel TorrealbaNo ratings yet

- CAT25C11/03/05/09/17: 1K/2K/4K/8K/16K SPI Serial CMOS E Prom FeaturesDocument10 pagesCAT25C11/03/05/09/17: 1K/2K/4K/8K/16K SPI Serial CMOS E Prom FeaturesAgnaldo Oliveira SantosNo ratings yet

- Basic Watchdog Timer: (Arduino Uno/Atmega328) by Nicolas LarsenDocument3 pagesBasic Watchdog Timer: (Arduino Uno/Atmega328) by Nicolas LarsenDavid ParraNo ratings yet

- Device Programming: 8.5.1 Erasure and ReprogrammingDocument16 pagesDevice Programming: 8.5.1 Erasure and ReprogrammingABID SIALNo ratings yet

- H9TQ17ABJTMCUR HynixSemiconductorDocument183 pagesH9TQ17ABJTMCUR HynixSemiconductorSfawaNo ratings yet

- 8K/16K 5.0V Microwire Serial EEPROM: FeaturesDocument12 pages8K/16K 5.0V Microwire Serial EEPROM: FeaturesStephensonNo ratings yet

- 3-Wire Serial Eeproms: FeaturesDocument18 pages3-Wire Serial Eeproms: FeaturesAriana ScheiderNo ratings yet

- TPS51216-EP Complete DDR2, DDR3 and DDR3L Memory Power Solution Synchronous Buck Controller, 2-A LDO, Buffered ReferenceDocument34 pagesTPS51216-EP Complete DDR2, DDR3 and DDR3L Memory Power Solution Synchronous Buck Controller, 2-A LDO, Buffered ReferenceJymy VegaNo ratings yet

- DS1388Document19 pagesDS1388mar_barudjNo ratings yet

- 96Khz 24-Bit ∆Σ Adc: General DescriptionDocument17 pages96Khz 24-Bit ∆Σ Adc: General DescriptionAlbertoNo ratings yet

- 1K/2K/4K 2.5V Microwire Serial EEPROM: Features: Package TypesDocument20 pages1K/2K/4K 2.5V Microwire Serial EEPROM: Features: Package TypesJoão PauloNo ratings yet

- Midas3.0 BMDocument139 pagesMidas3.0 BMMirosław WalasikNo ratings yet

- K4E641612D SamsungsemiconductorDocument36 pagesK4E641612D SamsungsemiconductorTor TuraNo ratings yet

- Three-Wire Serial EEPROM: 1. FeaturesDocument17 pagesThree-Wire Serial EEPROM: 1. FeatureskppsadiNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Atmel 0053Document1 pageAtmel 0053namerNo ratings yet

- Bootrst Ivsel Reset Address Interrupt Vectors Start AddressDocument1 pageBootrst Ivsel Reset Address Interrupt Vectors Start AddressnamerNo ratings yet

- Atmel 0051Document1 pageAtmel 0051namerNo ratings yet

- 12.2.2 EIMSK - External Interrupt Mask RegisterDocument1 page12.2.2 EIMSK - External Interrupt Mask RegisternamerNo ratings yet

- Interrupts: 11.1 Interrupt Vectors in Atmega328PDocument1 pageInterrupts: 11.1 Interrupt Vectors in Atmega328PnamerNo ratings yet

- 10.9 Register Description: Section 5. "About Code Examples" On Page 8Document1 page10.9 Register Description: Section 5. "About Code Examples" On Page 8namerNo ratings yet

- Atmel 0043Document1 pageAtmel 0043namerNo ratings yet

- Atmel 0045Document1 pageAtmel 0045namerNo ratings yet

- Bit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisterDocument1 pageBit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisternamerNo ratings yet

- Atmel 0038Document1 pageAtmel 0038namerNo ratings yet

- Atmel 0042Document1 pageAtmel 0042namerNo ratings yet

- Atmel 0036Document1 pageAtmel 0036namerNo ratings yet

- Atmel 0041Document1 pageAtmel 0041namerNo ratings yet

- Atmel 0037Document1 pageAtmel 0037namerNo ratings yet

- 8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisterDocument1 page8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisternamerNo ratings yet

- Power Management and Sleep ModesDocument1 pagePower Management and Sleep ModesnamerNo ratings yet

- Atmel 0040Document1 pageAtmel 0040namerNo ratings yet

- 9.2 Bod Disable: 35 Atmega328P (Datasheet)Document1 page9.2 Bod Disable: 35 Atmega328P (Datasheet)namerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- Atmel 0033Document1 pageAtmel 0033namerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- 8.8 External Clock: Frequency CKSEL3..0Document1 page8.8 External Clock: Frequency CKSEL3..0namerNo ratings yet

- Dynamics Study MaterialDocument57 pagesDynamics Study Materialanik sarkerNo ratings yet

- Cutawaytechnical453465436 5464356 345634 653456 34563 4563563 645635634 6Document8 pagesCutawaytechnical453465436 5464356 345634 653456 34563 4563563 645635634 6rseresfer34533373563No ratings yet

- MFI 2 - Unit 3 - SB - L+SDocument10 pagesMFI 2 - Unit 3 - SB - L+SHoan HoàngNo ratings yet

- Tyre Industry in IndiaDocument14 pagesTyre Industry in IndiaH Janardan PrabhuNo ratings yet

- Sensors & Transducers: (Code: EI 401)Document4 pagesSensors & Transducers: (Code: EI 401)Mayukh BiswasNo ratings yet

- Service Manual: RP-6000 MK6 LTD RP-6000 MK6 BDocument44 pagesService Manual: RP-6000 MK6 LTD RP-6000 MK6 BFivor EdwardsNo ratings yet

- IJETR022563Document5 pagesIJETR022563erpublicationNo ratings yet

- Materi Asking and Offering For HelpDocument9 pagesMateri Asking and Offering For HelpFranky ArdanaNo ratings yet

- Elements, Compounds, MixturesDocument35 pagesElements, Compounds, MixturesNorvieNo ratings yet

- Opti Turn Tu 2004 V ManualDocument80 pagesOpti Turn Tu 2004 V ManualCharu NavneetNo ratings yet

- ASTM A581 A581M-95bDocument3 pagesASTM A581 A581M-95bFeteneNo ratings yet

- Planning & Cost Control Engineer (Primavera & MS Project) : Aouache FaridDocument3 pagesPlanning & Cost Control Engineer (Primavera & MS Project) : Aouache FaridFarid FaridNo ratings yet

- Research Papers On Climate Change Global WarmingDocument4 pagesResearch Papers On Climate Change Global Warminggw1nm9nbNo ratings yet

- WPP Jak Campus - Defect All Level - 18042023Document15 pagesWPP Jak Campus - Defect All Level - 18042023bbm FebriNo ratings yet

- Servo Controlled FBW With Power Boost Control, Operations & Maint. ManualDocument126 pagesServo Controlled FBW With Power Boost Control, Operations & Maint. ManualKota NatarajanNo ratings yet

- My Family (Speaking Cards)Document1 pageMy Family (Speaking Cards)Maria Marynuch100% (1)

- L23 - Axial Flow CompressorDocument17 pagesL23 - Axial Flow CompressorRohan GuptaNo ratings yet

- Classic Plan: Dog/Cat BedDocument3 pagesClassic Plan: Dog/Cat BedRobson DiasNo ratings yet

- Module 5: Safety and Health at Work: Participant's HandbookDocument24 pagesModule 5: Safety and Health at Work: Participant's HandbookChristian Surio RamosNo ratings yet

- Ddrive Transmission ReportDocument43 pagesDdrive Transmission Reportelah150% (2)

- Agricultural Extension and CommunicationDocument173 pagesAgricultural Extension and CommunicationAlfredo Conde100% (1)

- IPC 4552 Cuprins - ENIG PDFDocument3 pagesIPC 4552 Cuprins - ENIG PDFMarlon CornejoNo ratings yet

- Bryophytes MorphologyDocument9 pagesBryophytes Morphologyrachna singh0% (1)

- LESSON 2 Facilities Location StrategiesDocument2 pagesLESSON 2 Facilities Location StrategiesElle LeeNo ratings yet

- IPC-S-816 SMT Process Guideline ChecklistDocument4 pagesIPC-S-816 SMT Process Guideline Checklistmigant23uNo ratings yet

- Full Download Test Bank For Environmental Economics and Management Theory Policy and Applications 6th Edition Callan PDF Full ChapterDocument27 pagesFull Download Test Bank For Environmental Economics and Management Theory Policy and Applications 6th Edition Callan PDF Full Chapterscissionrideau941m100% (20)

- SCM 025-108 M2Document8 pagesSCM 025-108 M2kazdanoNo ratings yet

- Genesis of KupferschieferDocument15 pagesGenesis of KupferschieferMaricela GarciaNo ratings yet

- Sorsogon State College Engineering & ArchitectureDocument11 pagesSorsogon State College Engineering & ArchitectureArianne Mae De Vera GallonNo ratings yet

- Research Report 2011 Asses Water ChambalDocument41 pagesResearch Report 2011 Asses Water Chambalsamyak sambhareNo ratings yet