Professional Documents

Culture Documents

Atmel 0053

Uploaded by

namerOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Atmel 0053

Uploaded by

namerCopyright:

Available Formats

12.

External Interrupts

The external interrupts are triggered by the INT0 and INT1 pins or any of the PCINT23..0 pins. Observe that, if enabled, the

interrupts will trigger even if the INT0 and INT1 or PCINT23..0 pins are configured as outputs. This feature provides a way of

generating a software interrupt. The pin change interrupt PCI2 will trigger if any enabled PCINT23..16 pin toggles. The pin

change interrupt PCI1 will trigger if any enabled PCINT14..8 pin toggles. The pin change interrupt PCI0 will trigger if any

enabled PCINT7..0 pin toggles. The PCMSK2, PCMSK1 and PCMSK0 registers control which pins contribute to the pin

change interrupts. Pin change interrupts on PCINT23..0 are detected asynchronously. This implies that these interrupts can

be used for waking the part also from sleep modes other than Idle mode.

The INT0 and INT1 interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the

specification for the external interrupt control register A – EICRA. When the INT0 or INT1 interrupts are enabled and are

configured as level triggered, the interrupts will trigger as long as the pin is held low. Note that recognition of falling or rising

edge interrupts on INT0 or INT1 requires the presence of an I/O clock, described in Section 8.1 “Clock Systems and their

Distribution” on page 24. Low level interrupt on INT0 and INT1 is detected asynchronously. This implies that this interrupt

can be used for waking the part also from sleep modes other than idle mode. The I/O clock is halted in all sleep modes

except Idle mode.

Note that if a level triggered interrupt is used for wake-up from power-down, the required level must be held long enough for

the MCU to complete the wake-up to trigger the level interrupt. If the level disappears before the end of the start-up time, the

MCU will still wake up, but no interrupt will be generated. The start-up time is defined by the SUT and CKSEL fuses as

described in Section 8. “System Clock and Clock Options” on page 24.

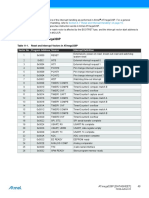

12.1 Pin Change Interrupt Timing

An example of timing of a pin change interrupt is shown in Figure 12-1.

Figure 12-1. Timing of Pin Change Interrupts

pin_lat pin_sync pcint_in_(0) 0 pcint_sync pcint_setflag

PCINT(0) D Q

PCIF

LE x

PCINT(0) in PCMSK(x)

clk

clk

clk

PCINT(0)

pin_lat

pin_sync

pcint_in_(0)

pcint_syn

pcint_setflag

PCIF

ATmega328P [DATASHEET] 53

7810D–AVR–01/15

You might also like

- 10 Interrupt v22Document29 pages10 Interrupt v22Pipat NakasenoNo ratings yet

- Microprocessor Architectures and Systems: RISC, CISC and DSPFrom EverandMicroprocessor Architectures and Systems: RISC, CISC and DSPRating: 4 out of 5 stars4/5 (1)

- EE 308 Apr. 19, 2002Document12 pagesEE 308 Apr. 19, 2002asprillaNo ratings yet

- The PIC Microcontroller: Your Personal Introductory CourseFrom EverandThe PIC Microcontroller: Your Personal Introductory CourseRating: 1 out of 5 stars1/5 (2)

- Golam Mostafa: Atmega8 Risc Microcontroller Interfacing and System DesignDocument60 pagesGolam Mostafa: Atmega8 Risc Microcontroller Interfacing and System DesignRuchit SankhesaraNo ratings yet

- Power Point PresentationDocument17 pagesPower Point PresentationVNo ratings yet

- 12.2.6 PCMSK2 - Pin Change Mask Register 2Document1 page12.2.6 PCMSK2 - Pin Change Mask Register 2kachalNo ratings yet

- 12.2.4 PCICR - Pin Change Interrupt Control RegisterDocument1 page12.2.4 PCICR - Pin Change Interrupt Control RegisterkachalNo ratings yet

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocument8 pagesCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocument8 pagesCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- Pin No. Pin Name Description Alternate FunctionDocument7 pagesPin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- Encoder Check PLC ProgramsDocument3 pagesEncoder Check PLC Programsanacer55No ratings yet

- Description Alternate FunctionDocument8 pagesDescription Alternate FunctionnareshhhhhNo ratings yet

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocument8 pagesCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- Sdsafgdshgfvnbvnvnvnb: Description Alternate FunctionDocument8 pagesSdsafgdshgfvnbvnvnvnb: Description Alternate FunctionnareshhhhhNo ratings yet

- Description Alternate Function: SFDFDGFBGFDocument8 pagesDescription Alternate Function: SFDFDGFBGFnareshhhhhNo ratings yet

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocument8 pagesCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- Pin No. Pin Name Description Alternate FunctionDocument6 pagesPin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- XC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBDocument8 pagesXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBnareshhhhhNo ratings yet

- VCV CXB CCNBFVBFCGXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBDocument8 pagesVCV CXB CCNBFVBFCGXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBnareshhhhhNo ratings yet

- Atmel 9157 Automotive Microcontrollers ATtiny88 DatasheetDocument221 pagesAtmel 9157 Automotive Microcontrollers ATtiny88 DatasheetAdrian GarciaNo ratings yet

- Mcp23008 App NoteDocument10 pagesMcp23008 App NoteHarold LeeNo ratings yet

- ATmega 328 PDocument345 pagesATmega 328 PAna AndreiNo ratings yet

- Xddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgfvnbvnvnvn B: Descriptio N Alternate FunctionDocument8 pagesXddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgfvnbvnvnvn B: Descriptio N Alternate FunctionnareshhhhhNo ratings yet

- Input Capture Mode PIC32Document24 pagesInput Capture Mode PIC32Oscar Mauricio Gomez JaimesNo ratings yet

- ATmega GPIODocument17 pagesATmega GPIOredgabriel23No ratings yet

- Programable Elements I InterruptsDocument17 pagesProgramable Elements I InterruptsOliver Ochoa GarciaNo ratings yet

- Atmel 8271 8 Bit Avr Microcontroller Atmega48a 48pa 88a 88pa 168a 168pa 328 328p - Datasheet - SummaryDocument39 pagesAtmel 8271 8 Bit Avr Microcontroller Atmega48a 48pa 88a 88pa 168a 168pa 328 328p - Datasheet - SummarycarlosNo ratings yet

- DELL Inspiron N4020Document88 pagesDELL Inspiron N4020Deddy SuyantoNo ratings yet

- 4x4 Matrix KeypadDocument12 pages4x4 Matrix KeypadVikram ReddyNo ratings yet

- Prominiv3 0 PDFDocument1 pageProminiv3 0 PDFfacugomezNo ratings yet

- Atmel 8271 8 Bit AVR Microcontroller ATmega48A 48PA 88A 88PA 168A 168PA 328 328P - Datasheet - Summary PDFDocument50 pagesAtmel 8271 8 Bit AVR Microcontroller ATmega48A 48PA 88A 88PA 168A 168PA 328 328P - Datasheet - Summary PDFspuzzarNo ratings yet

- ATmega328 Pin Diagram Cheat SheetDocument1 pageATmega328 Pin Diagram Cheat SheeterxetoNo ratings yet

- 8-Bit Microcontroller With 4K Bytes Quickflash Memory At80F51Document5 pages8-Bit Microcontroller With 4K Bytes Quickflash Memory At80F51RAJKUMARNo ratings yet

- DatasheetDocument29 pagesDatasheetProfesor RosokNo ratings yet

- ATmega 16 U 2Document22 pagesATmega 16 U 2luisNo ratings yet

- Atmel 8271 8 Bit AVR Microcontroller ATmega48A 48PA 88A 88PA 168A 168PA 328 328P - Datasheet - SummaryDocument31 pagesAtmel 8271 8 Bit AVR Microcontroller ATmega48A 48PA 88A 88PA 168A 168PA 328 328P - Datasheet - SummaryAndres PerezNo ratings yet

- Avr ArchitectureDocument29 pagesAvr ArchitectureOdoch HerbertNo ratings yet

- 8-Bit Microcontroller With 8K Bytes In-System Programmable Flash Atmega48/V Atmega88/V Atmega168/V PreliminaryDocument359 pages8-Bit Microcontroller With 8K Bytes In-System Programmable Flash Atmega48/V Atmega88/V Atmega168/V PreliminaryAdrian BritoNo ratings yet

- Chapter 2 Micro ArchitectureDocument20 pagesChapter 2 Micro ArchitectureShanker KalaivaniNo ratings yet

- An Introduction To The PIC Microcontroller: EE2801 - Lecture 19Document9 pagesAn Introduction To The PIC Microcontroller: EE2801 - Lecture 19Reddy BabuNo ratings yet

- BO039M1920M DatasheetDocument21 pagesBO039M1920M DatasheetJohn LyalNo ratings yet

- Datasheet Micro M65582AMF-105FPDocument46 pagesDatasheet Micro M65582AMF-105FPsel_mor100% (1)

- At 89c2051 DataDocument20 pagesAt 89c2051 Datarangana rathnayakaNo ratings yet

- ATmega 328 PDocument17 pagesATmega 328 PEduardo SantosNo ratings yet

- Exp6 TTL Nand PDFDocument4 pagesExp6 TTL Nand PDFJohn wickNo ratings yet

- Atmel 7810 Automotive Microcontrollers ATmega328P - Datasheet PDFDocument294 pagesAtmel 7810 Automotive Microcontrollers ATmega328P - Datasheet PDFnagendra2195No ratings yet

- EE6008 Unit 2Document11 pagesEE6008 Unit 2TakeItEasyDude TIEDNo ratings yet

- 90us82 162Document305 pages90us82 162Sorin AlexandruNo ratings yet

- PIC Simple Signal GeneratorDocument5 pagesPIC Simple Signal GeneratorDumindu JayawardeneNo ratings yet

- Arduino Pro Mini (DEV-11113) : TXD RXDDocument2 pagesArduino Pro Mini (DEV-11113) : TXD RXDMeghaNo ratings yet

- Lec 8 NotesDocument9 pagesLec 8 NotesAlan BensonNo ratings yet

- 8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesDocument15 pages8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesGomzalez Bin GembozNo ratings yet

- Pic Micro ControllerDocument83 pagesPic Micro ControllerDenise Nelson100% (3)

- Micro ControllerDocument21 pagesMicro Controllerkrishn_blazeNo ratings yet

- CD4013B CMOS Dual D-Type Flip-Flop: 1 Features 3 DescriptionDocument28 pagesCD4013B CMOS Dual D-Type Flip-Flop: 1 Features 3 DescriptionjwestmisterNo ratings yet

- CD4013B CMOS Dual D-Type Flip-Flop: 1 Features 3 DescriptionDocument30 pagesCD4013B CMOS Dual D-Type Flip-Flop: 1 Features 3 DescriptionDama DamaNo ratings yet

- Overview/Application: Shenzhen Huai Zhi Technology Co.,LimitedDocument26 pagesOverview/Application: Shenzhen Huai Zhi Technology Co.,LimitedBurak CNo ratings yet

- ATmega8 RegisterInfo v0 2Document12 pagesATmega8 RegisterInfo v0 2api-3699101No ratings yet

- Atmel 0051Document1 pageAtmel 0051namerNo ratings yet

- Interrupts: 11.1 Interrupt Vectors in Atmega328PDocument1 pageInterrupts: 11.1 Interrupt Vectors in Atmega328PnamerNo ratings yet

- Bootrst Ivsel Reset Address Interrupt Vectors Start AddressDocument1 pageBootrst Ivsel Reset Address Interrupt Vectors Start AddressnamerNo ratings yet

- 12.2.2 EIMSK - External Interrupt Mask RegisterDocument1 page12.2.2 EIMSK - External Interrupt Mask RegisternamerNo ratings yet

- Bit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisterDocument1 pageBit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisternamerNo ratings yet

- Atmel 0043Document1 pageAtmel 0043namerNo ratings yet

- Atmel 0038Document1 pageAtmel 0038namerNo ratings yet

- 8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisterDocument1 page8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisternamerNo ratings yet

- 10.9 Register Description: Section 5. "About Code Examples" On Page 8Document1 page10.9 Register Description: Section 5. "About Code Examples" On Page 8namerNo ratings yet

- Atmel 0042Document1 pageAtmel 0042namerNo ratings yet

- Atmel 0036Document1 pageAtmel 0036namerNo ratings yet

- Atmel 0041Document1 pageAtmel 0041namerNo ratings yet

- Atmel 0037Document1 pageAtmel 0037namerNo ratings yet

- Atmel 0045Document1 pageAtmel 0045namerNo ratings yet

- Atmel 0044Document1 pageAtmel 0044namerNo ratings yet

- Power Management and Sleep ModesDocument1 pagePower Management and Sleep ModesnamerNo ratings yet

- Atmel 0040Document1 pageAtmel 0040namerNo ratings yet

- 9.2 Bod Disable: 35 Atmega328P (Datasheet)Document1 page9.2 Bod Disable: 35 Atmega328P (Datasheet)namerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- Atmel 0033Document1 pageAtmel 0033namerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- 8.8 External Clock: Frequency CKSEL3..0Document1 page8.8 External Clock: Frequency CKSEL3..0namerNo ratings yet

- Laguna Tech MANUAL F5R ENGINE - f5r700 PDFDocument120 pagesLaguna Tech MANUAL F5R ENGINE - f5r700 PDFJeanclaude NgangueNo ratings yet

- On-Off VS ModulationDocument3 pagesOn-Off VS ModulationCarlos WayNo ratings yet

- Siemens Optipoint Manual Accessories MultilanguagesDocument177 pagesSiemens Optipoint Manual Accessories MultilanguagesHaefelin ArnaudNo ratings yet

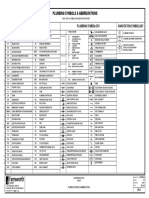

- Plumbing Symbols & AbbreviationsDocument8 pagesPlumbing Symbols & AbbreviationsThel Cruz100% (1)

- Network Theorems ExperimentDocument3 pagesNetwork Theorems ExperimentReddyvari Venugopal100% (1)

- Pilot Circuits: Service Training Manual CM 760/780Document5 pagesPilot Circuits: Service Training Manual CM 760/780victor laraNo ratings yet

- QCVN 09-2013 National Technical Regulation On Energy Efficiency Buildings (Eng)Document56 pagesQCVN 09-2013 National Technical Regulation On Energy Efficiency Buildings (Eng)Law ArveyNo ratings yet

- Induction Machines and Synchronous Machines (3-2-0)Document2 pagesInduction Machines and Synchronous Machines (3-2-0)Imran JkNo ratings yet

- Technical Specification STS-6000K-H1 13.8kV 60Hz For 200 - 215KTL - V6.0Document18 pagesTechnical Specification STS-6000K-H1 13.8kV 60Hz For 200 - 215KTL - V6.0Antonio CanalesNo ratings yet

- Congelador PanasonicDocument4 pagesCongelador PanasonicEnno EisenkolbNo ratings yet

- SPRacingF3 Manual LatestDocument9 pagesSPRacingF3 Manual Latestasl68yNo ratings yet

- E WasteDocument1 pageE WasteIkmal AhmadNo ratings yet

- Silicon NPN Power Transistors: Inchange Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Inchange Semiconductor Product Specificationvali2daduicaNo ratings yet

- DL PU酗尸: Products Ma■UalDocument24 pagesDL PU酗尸: Products Ma■UalMahmoudNo ratings yet

- QuotationDocument2 pagesQuotationsittichai saelimNo ratings yet

- SAMSUNG (Chassis KS1)Document12 pagesSAMSUNG (Chassis KS1)Dario David DimaroNo ratings yet

- FD600CAMDocument14 pagesFD600CAMjosue jetavionicsNo ratings yet

- Yamaha Mio M3 Parts - 01 - LNS125 MIO M3 CYLINDERDocument1 pageYamaha Mio M3 Parts - 01 - LNS125 MIO M3 CYLINDERbangtopiNo ratings yet

- Quanta Da0z8vmb8e0 R1aDocument44 pagesQuanta Da0z8vmb8e0 R1aRene Ruiz100% (1)

- Chieftec Aps 650cbDocument26 pagesChieftec Aps 650cbbatamazurNo ratings yet

- GSM900 Dual-Band Selective Repeater 200mw SGR-R310 User ManualDocument15 pagesGSM900 Dual-Band Selective Repeater 200mw SGR-R310 User ManualIan MauhayNo ratings yet

- HE800DIQ716CDocument8 pagesHE800DIQ716CRicardo NunesNo ratings yet

- Macro CellDocument29 pagesMacro Cellvasece4537577No ratings yet

- Byv 32Document5 pagesByv 32chawkigenieNo ratings yet

- Airless TireDocument12 pagesAirless TireLaxmipriya SenapatiNo ratings yet

- SSH Buku IDocument335 pagesSSH Buku IVoteJokowiNo ratings yet

- TM M672320 340Document2 pagesTM M672320 340Ara AkramNo ratings yet

- ML411A Solar Marine LanternDocument12 pagesML411A Solar Marine Lanternjetr19754106No ratings yet

- HydraulicPowerUnit PowerTransmissionDocument4 pagesHydraulicPowerUnit PowerTransmissionCesar Ruben SosaNo ratings yet

- 10 III March 2022Document6 pages10 III March 2022Rehana TahasildarNo ratings yet