Professional Documents

Culture Documents

Atmel 0042

Uploaded by

namerOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Atmel 0042

Uploaded by

namerCopyright:

Available Formats

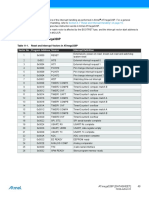

10.

4 External Reset

An external reset is generated by a low level on the RESET pin. Reset pulses longer than the minimum pulse width (see

Section 28.6 “System and Reset Characteristics” on page 261) will generate a reset, even if the clock is not running. Shorter

pulses are not guaranteed to generate a reset. When the applied signal reaches the reset threshold voltage – VRST – on its

positive edge, the delay counter starts the MCU after the time-out period – tTOUT – has expired. The external reset can be

disabled by the RSTDISBL fuse, see Table 27-7 on page 244.

Figure 10-4. External Reset During Operation

VCC

RESET V RST

tTOUT

TIME-OUT

INTERNAL

RESET

10.5 Brown-out Detection

Atmel® ATmega328P has an on-chip brown-out detection (BOD) circuit for monitoring the VCC level during operation by

comparing it to a fixed trigger level. The trigger level for the BOD can be selected by the BODLEVEL fuses. The trigger level

has a hysteresis to ensure spike free brown-out detection. The hysteresis on the detection level should be interpreted as

VBOT+ = VBOT + VHYST/2 and VBOT– = VBOT – VHYST/2.When the BOD is enabled, and VCC decreases to a value below the

trigger level (VBOT- in Figure 10-5), the brown-out reset is immediately activated. When VCC increases above the trigger level

(VBOT+ in Figure 10-5), the delay counter starts the MCU after the time-out period tTOUT has expired.

The BOD circuit will only detect a drop in VCC if the voltage stays below the trigger level for longer than tBOD given in Section

28.6 “System and Reset Characteristics” on page 261.

Figure 10-5. Brown-out Reset During Operation

VCC

VBOT+

VBOT-

RESET

tTOUT

TIME-OUT

INTERNAL

RESET

42 ATmega328P [DATASHEET]

7810D–AVR–01/15

You might also like

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Atmel 0043Document1 pageAtmel 0043namerNo ratings yet

- LCD Panel Claa320wb02Document29 pagesLCD Panel Claa320wb02ВМалиновNo ratings yet

- Reset ICDocument8 pagesReset ICÁrpád HimpliNo ratings yet

- Section 8. 70055cDocument20 pagesSection 8. 70055cjpjenifferNo ratings yet

- An2017 Different Ways To Reset st7 Microcontroller Stmicroelectronics 1Document10 pagesAn2017 Different Ways To Reset st7 Microcontroller Stmicroelectronics 1Maxwell KaranjaNo ratings yet

- M48T02 150pciDocument15 pagesM48T02 150pciImran YaminNo ratings yet

- 1.5A USB-Friendly Li-Ion Battery Charger and Power-Path Management ICDocument33 pages1.5A USB-Friendly Li-Ion Battery Charger and Power-Path Management ICanarchie2008No ratings yet

- 3. ΔΙΑΔΙΚΑΣΙΑ RESET (Highest priority interrupt) AVR: Power-on Reset. External ResetDocument16 pages3. ΔΙΑΔΙΚΑΣΙΑ RESET (Highest priority interrupt) AVR: Power-on Reset. External ResetNick TarasNo ratings yet

- SIPROTEC 5 - Configuration: Technical DataDocument10 pagesSIPROTEC 5 - Configuration: Technical DatasuadNo ratings yet

- AVR190: Power Up Considerations: 8-Bit Microcontroller Application NoteDocument4 pagesAVR190: Power Up Considerations: 8-Bit Microcontroller Application NoteRichard KrillNo ratings yet

- Atmel 0041Document1 pageAtmel 0041namerNo ratings yet

- VT8000 Room Controllers: VTR8350/VT8350 Application GuideDocument96 pagesVT8000 Room Controllers: VTR8350/VT8350 Application GuidehtanhNo ratings yet

- Datasheet Bit3715 PMW Monitor LCD AcerDocument11 pagesDatasheet Bit3715 PMW Monitor LCD AcershibatoyanNo ratings yet

- Bit 3251Document7 pagesBit 3251Paulo Roberto s freireNo ratings yet

- MSP430 Microcontroller Basics Chapter 8.1Document6 pagesMSP430 Microcontroller Basics Chapter 8.1Jag JagNo ratings yet

- Bit 3715Document11 pagesBit 3715Rocko RattNo ratings yet

- Watch TimerDocument4 pagesWatch Timerwtn2013No ratings yet

- Bq4847/bq4847y: RTC Module With CPU SupervisorDocument5 pagesBq4847/bq4847y: RTC Module With CPU Supervisorelhandasya MedicalNo ratings yet

- Data SheetDocument29 pagesData SheetАндрей АлексеевNo ratings yet

- AN1353 Application Note: ASD ST62000C Software Description For Cooling Thermostat ApplicatonsDocument17 pagesAN1353 Application Note: ASD ST62000C Software Description For Cooling Thermostat ApplicatonsDan EsentherNo ratings yet

- Datasheet - HK rt8110 7327105 PDFDocument14 pagesDatasheet - HK rt8110 7327105 PDFLuis CarlosNo ratings yet

- 8.2 Clock Sources: 8.1.4 Asynchronous Timer Clock - CLKDocument1 page8.2 Clock Sources: 8.1.4 Asynchronous Timer Clock - CLKsalarNo ratings yet

- BQ2000Document27 pagesBQ2000German GodiNo ratings yet

- Bit 3713Document11 pagesBit 3713Jan RiskenNo ratings yet

- BQ 20 Z 70Document17 pagesBQ 20 Z 70Vukica IvicNo ratings yet

- AM5888SDocument10 pagesAM5888SproctepNo ratings yet

- DELL Inspiron N4020Document88 pagesDELL Inspiron N4020Deddy SuyantoNo ratings yet

- Data SheetDocument6 pagesData SheetΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- User's Manual: Brake Chopper Unit (Bcu) ApplicationDocument28 pagesUser's Manual: Brake Chopper Unit (Bcu) ApplicationCatalin PelinNo ratings yet

- DatasheetDocument9 pagesDatasheetLuis Caba RamirezNo ratings yet

- UD01138d BCU ABFIFF01 V002Document27 pagesUD01138d BCU ABFIFF01 V002Catalin PelinNo ratings yet

- BESCHREIBUNG KD01 VTS01 EngDocument12 pagesBESCHREIBUNG KD01 VTS01 EngIainNo ratings yet

- Microcontroller-Based System For Voltage Monitoring, Protection and Recovery Using Proteus VSM SoftwareDocument5 pagesMicrocontroller-Based System For Voltage Monitoring, Protection and Recovery Using Proteus VSM SoftwareFuh ValleryNo ratings yet

- ZK3201 Control Panel User's ManualDocument49 pagesZK3201 Control Panel User's Manualmenale libayeNo ratings yet

- ECN3021Document10 pagesECN3021Wasang Juwi PracihnoNo ratings yet

- 05 AVR Timer-Counter AVRDocument95 pages05 AVR Timer-Counter AVRPriscillaNo ratings yet

- 4M (512K 8/256K 16) BIT: Flash MemoryDocument55 pages4M (512K 8/256K 16) BIT: Flash MemorytecrgoNo ratings yet

- Fully Controlled RectifierDocument18 pagesFully Controlled RectifierVipin_amNo ratings yet

- How To Check 3v1Document12 pagesHow To Check 3v1jonas consina100% (2)

- 25AA640/25LC640: 64K SPI Bus Serial EEPROMDocument24 pages25AA640/25LC640: 64K SPI Bus Serial EEPROMnguyenluongdpNo ratings yet

- Relevador Motor 7SK82 - P1H132886Document7 pagesRelevador Motor 7SK82 - P1H132886jose jaime vazquez barbozaNo ratings yet

- Pin No. Pin Name Description Alternate FunctionDocument7 pagesPin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- CN803Document7 pagesCN803RogeriomgoNo ratings yet

- 10 Vertical Take Off and Landing ControlDocument27 pages10 Vertical Take Off and Landing ControlkalyanNo ratings yet

- Tiny Predictive Fan Failure Detector: Features General DescriptionDocument14 pagesTiny Predictive Fan Failure Detector: Features General DescriptionAkoKhalediNo ratings yet

- SA5888Document8 pagesSA5888albinicue1No ratings yet

- LB1845 DDocument9 pagesLB1845 DFernando LizarragaNo ratings yet

- QNET VTOL User ManualDocument27 pagesQNET VTOL User ManualSuryabhan SinghNo ratings yet

- Vel motorDCDocument28 pagesVel motorDCProfessor RASIANo ratings yet

- Laptop 8Document7 pagesLaptop 8أحمد الأمينNo ratings yet

- Sluuba 6Document21 pagesSluuba 6davo aslanyanNo ratings yet

- 988611457NK448908 Vehicle Scan ReportDocument5 pages988611457NK448908 Vehicle Scan ReportVictor Daniel Piñeros ZubietaNo ratings yet

- Tlv8Xxxevm-019 Evaluation Modules: User S GuideDocument9 pagesTlv8Xxxevm-019 Evaluation Modules: User S GuideToni BioscaNo ratings yet

- P1J625216 - Configurator DesignDocument5 pagesP1J625216 - Configurator Designjohann.castiblancobNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Atmel 0053Document1 pageAtmel 0053namerNo ratings yet

- Atmel 0051Document1 pageAtmel 0051namerNo ratings yet

- Bootrst Ivsel Reset Address Interrupt Vectors Start AddressDocument1 pageBootrst Ivsel Reset Address Interrupt Vectors Start AddressnamerNo ratings yet

- 12.2.2 EIMSK - External Interrupt Mask RegisterDocument1 page12.2.2 EIMSK - External Interrupt Mask RegisternamerNo ratings yet

- Interrupts: 11.1 Interrupt Vectors in Atmega328PDocument1 pageInterrupts: 11.1 Interrupt Vectors in Atmega328PnamerNo ratings yet

- Bit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisterDocument1 pageBit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisternamerNo ratings yet

- 10.9 Register Description: Section 5. "About Code Examples" On Page 8Document1 page10.9 Register Description: Section 5. "About Code Examples" On Page 8namerNo ratings yet

- Atmel 0037Document1 pageAtmel 0037namerNo ratings yet

- Atmel 0041Document1 pageAtmel 0041namerNo ratings yet

- Atmel 0038Document1 pageAtmel 0038namerNo ratings yet

- Atmel 0033Document1 pageAtmel 0033namerNo ratings yet

- Atmel 0036Document1 pageAtmel 0036namerNo ratings yet

- 8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisterDocument1 page8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisternamerNo ratings yet

- Atmel 0045Document1 pageAtmel 0045namerNo ratings yet

- 9.2 Bod Disable: 35 Atmega328P (Datasheet)Document1 page9.2 Bod Disable: 35 Atmega328P (Datasheet)namerNo ratings yet

- Power Management and Sleep ModesDocument1 pagePower Management and Sleep ModesnamerNo ratings yet

- Atmel 0044Document1 pageAtmel 0044namerNo ratings yet

- Atmel 0040Document1 pageAtmel 0040namerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- 8.8 External Clock: Frequency CKSEL3..0Document1 page8.8 External Clock: Frequency CKSEL3..0namerNo ratings yet