Professional Documents

Culture Documents

Bit 3 - WDE: Watchdog System Reset Enable

Uploaded by

namerOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bit 3 - WDE: Watchdog System Reset Enable

Uploaded by

namerCopyright:

Available Formats

• Bit 3 - WDE: Watchdog System Reset Enable

WDE is overridden by WDRF in MCUSR. This means that WDE is always set when WDRF is set. To clear WDE, WDRF

must be cleared first. This feature ensures multiple resets during conditions causing failure, and a safe start-up after the

failure.

• Bit 5, 2..0 - WDP3..0: Watchdog Timer Prescaler 3, 2, 1 and 0

The WDP3..0 bits determine the watchdog timer prescaling when the watchdog timer is running. The different prescaling

values and their corresponding time-out periods are shown in Table 10-3.

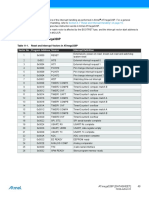

Table 10-3. Watchdog Timer Prescale Select

WDP3 WDP2 WDP1 WDP0 Number of WDT Oscillator Cycles Typical Time-out at VCC = 5.0V

0 0 0 0 2K (2048) cycles 16ms

0 0 0 1 4K (4096) cycles 32ms

0 0 1 0 8K (8192) cycles 64ms

0 0 1 1 16K (16384) cycles 0.125s

0 1 0 0 32K (32768) cycles 0.25s

0 1 0 1 64K (65536) cycles 0.5s

0 1 1 0 128K (131072) cycles 1.0s

0 1 1 1 256K (262144) cycles 2.0s

1 0 0 0 512K (524288) cycles 4.0s

1 0 0 1 1024K (1048576) cycles 8.0s

1 0 1 0

1 0 1 1

1 1 0 0

Reserved

1 1 0 1

1 1 1 0

1 1 1 1

48 ATmega328P [DATASHEET]

7810D–AVR–01/15

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Atmel 0053Document1 pageAtmel 0053namerNo ratings yet

- Bootrst Ivsel Reset Address Interrupt Vectors Start AddressDocument1 pageBootrst Ivsel Reset Address Interrupt Vectors Start AddressnamerNo ratings yet

- Atmel 0051Document1 pageAtmel 0051namerNo ratings yet

- 12.2.2 EIMSK - External Interrupt Mask RegisterDocument1 page12.2.2 EIMSK - External Interrupt Mask RegisternamerNo ratings yet

- Interrupts: 11.1 Interrupt Vectors in Atmega328PDocument1 pageInterrupts: 11.1 Interrupt Vectors in Atmega328PnamerNo ratings yet

- Atmel 0043Document1 pageAtmel 0043namerNo ratings yet

- 10.9 Register Description: Section 5. "About Code Examples" On Page 8Document1 page10.9 Register Description: Section 5. "About Code Examples" On Page 8namerNo ratings yet

- Atmel 0045Document1 pageAtmel 0045namerNo ratings yet

- Bit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisterDocument1 pageBit 1 - EXTRF: External Reset Flag: 10.9.2 WDTCSR - Watchdog Timer Control RegisternamerNo ratings yet

- Atmel 0038Document1 pageAtmel 0038namerNo ratings yet

- Atmel 0042Document1 pageAtmel 0042namerNo ratings yet

- Atmel 0036Document1 pageAtmel 0036namerNo ratings yet

- Atmel 0041Document1 pageAtmel 0041namerNo ratings yet

- Atmel 0037Document1 pageAtmel 0037namerNo ratings yet

- 8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisterDocument1 page8.10 Timer/Counter Oscillator: 8.12.1 OSCCAL - Oscillator Calibration RegisternamerNo ratings yet

- Atmel 0040Document1 pageAtmel 0040namerNo ratings yet

- Atmel 0044Document1 pageAtmel 0044namerNo ratings yet

- 9.2 Bod Disable: 35 Atmega328P (Datasheet)Document1 page9.2 Bod Disable: 35 Atmega328P (Datasheet)namerNo ratings yet

- 8.8 External Clock: Frequency CKSEL3..0Document1 page8.8 External Clock: Frequency CKSEL3..0namerNo ratings yet

- Power Management and Sleep ModesDocument1 pagePower Management and Sleep ModesnamerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- Section 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244Document1 pageSection 8.12.1 "OSCCAL - Oscillator Calibration Register" On Page 32 Table 28-1 On Page 260 Section 27.4 "Calibration Byte" On Page 244namerNo ratings yet

- Atmel 0033Document1 pageAtmel 0033namerNo ratings yet