Professional Documents

Culture Documents

TC6215 N-And P-Channel Enhancement-Mode Dual MOSFET: Features General Description

Uploaded by

felipekillerOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TC6215 N-And P-Channel Enhancement-Mode Dual MOSFET: Features General Description

Uploaded by

felipekillerCopyright:

Available Formats

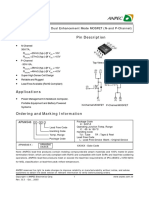

TC6215

N- and P-Channel

Enhancement-Mode Dual MOSFET

Features General Description

► Back to back gate-source Zener diodes

The Supertex TC6215 consists of high voltage, low threshold N-channel

► Guaranteed RDS(ON) at 4.0V gate drive

and P-channel MOSFETs in an 8-Lead SOIC (TG) package. Both

► Low threshold

MOSFETs have integrated back to back gate-source Zener diode clamps

► Low on-resistance

and guaranteed RDS(ON) ratings down to 4.0V gate drive allowing them to

► Independent N- and P-channels

be driven directly with standard 5.0V CMOS logic.

► Electrically isolated N- and P-channels

► Low input capacitance

These low threshold enhancement-mode (normally-off) transistors utilize

► Fast switching speeds

an advanced vertical DMOS structure and Supertex’s well-proven silicon-

► Free from secondary breakdowns

gate manufacturing process. This combination produces devices with the

► Low input and output leakage

power handling capabilities of bipolar transistors and with the high input

Applications impedance and positive temperature coefficient inherent in MOS devices.

Characteristic of all MOS structures, these devices are free from thermal

► High voltage pulsers

runaway and thermally-induced secondary breakdown.

► Amplifiers

► Buffers

Supertex’s vertical DMOS FETs are ideally suited to a wide range of

► Piezoelectric transducer drivers

switching and amplifying applications where very low threshold voltage,

► General purpose line drivers

high breakdown voltage, high input impedance, low input capacitance,

► Logic level interfaces

and fast switching speeds are desired.

Ordering Information

Package Option BVDSS/BVDGS RDS(ON) (Max)

Device 8-Lead SOIC

4.90x3.90mm body N-Channel P-Channel N-Channel P-Channel

1.75mm height (max) (V) (V) (Ω) (Ω)

1.27mm pitch

TC6215 TC6215TG-G 150 -150 4.0 7.0

-G indicates package is RoHS compliant (‘Green’)

Absolute Maximum Ratings Pin Configuration

DP

Parameter Value DP

DN

Drain-to-source voltage BVDSS DN

Drain-to-gate voltage BVDGS GP

SP

Gate-to-source voltage ±20V GN

SN

Operating and storage temperature -55°C to + 150°C 8-Lead SOIC (TG)

(top view)

Soldering temperature* 300°C

Absolute Maximum Ratings are those values beyond which damage to the device

Product Marking

may occur. Functional operation under these conditions is not implied. Continuous

YYWW

YY = Year Sealed

operation of the device at the absolute rating level may affect device reliability. All

WW = Week Sealed

voltages are referenced to device ground.

C6215 L = Lot Number

* Distance of 1.6mm from case for 10 seconds. LLLL = “Green” Packaging

Package may or may not include the following marks: Si or

8-Lead SOIC (TG)

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

TC6215

N-Channel Electrical Characteristics (T = 25°C unless otherwise specified) A

Sym Parameter Min Typ Max Units Conditions

BVDSS Drain-to-source breakdown voltage 150 - - V VGS = 0V, ID = 1.0mA

VGS(th) Gate threshold voltage 1.0 - 2.0 V VGS = VDS, ID =1.0mA

ΔVGS(th) Change in VGS(th) with temperature - - -4.5 mV/OC VGS = VDS, ID = 1.0mA

VZGS Gate-source back to back Zener voltage ±14 - ±25 V IGS = ±1.0mA

- - 5.0 µA VGS = 0V, VDS = Max Rating

IDSS Zero gate voltage drain current VDS = 0.8 Max Rating,

- - 1.0 mA

VGS = 0V, TA = 125°C

- 2.0 - VGS = 4.5V, VDS = 25V

ID(ON) On-state drain current A

- 3.8 - VGS = 10V, VDS = 25V

- - 4.0 VGS = 4.0V, ID = 0.5A

RDS(ON) Static drain-to-source on-state resistance - - 5.0 Ω VGS = 5.0V, ID = 2.0A

- - 4.0 VGS = 10V, ID = 2.0A

ΔRDS(ON) Change in RDS(ON) with temperature - - 1.0 %/OC VGS = 5.0V, ID = 2.0A

GFS Forward transconductance 560 - - mmho VDS = 10V, ID = 0.5A

CISS Input capacitance - 120 -

VGS = 0V,

COSS Common source output capacitance - 33 - pF VDS = 25V,

f = 1.0MHz

CRSS Reverse transfer capacitance - 11 -

td(ON) Turn-on delay time - 2.5 -

tr Rise time - 2.3 - VDD = 25V,

ns ID = 1.0A,

td(OFF) Turn-off delay time - 17.2 - RGEN = 25Ω

tf Fall time - 11.3 -

VSD Diode forward voltage drop - - 1.4 V VGS = 0V, ISD = 0.5A

trr Reverse recovery time - 90 - ns VGS = 0V, ISD = 0.5A

Notes:

1. All DC parameters 100% tested at 25°C unless otherwise stated. (Pulsed test: 300µs pulse at 2% duty cycle.)

2. All AC parameters sample tested.

N-Channel Switching Waveforms and Test Circuit

VDD

10V

90% RL

Input Pulse

Generator OUTPUT

10%

0V

t(ON) t(OFF) RGEN

td(ON) tr td(OFF) tf D.U.T.

VDD

Input

10% 10%

Output

0V 90% 90%

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

2

TC6215

P-Channel Electrical Characteristics (T = 25°C unless otherwise specified)

A

Sym Parameter Min Typ Max Units Conditions

BVDSS Drain-to-source breakdown voltage -150 - - V VGS = 0V, ID = -1.0mA

VGS(th) Gate threshold voltage -1.0 - -2.0 V VGS = VDS, ID =-1.0mA

ΔVGS(th) Change in VGS(th) with temperature - - 4.5 mV/OC VGS = VDS, ID = -1.0mA

VZGS Gate-source back to back Zener voltage ±14 - ±25 V IGS = ±1.0mA

- - -5.0 µA VGS = 0V, VDS = Max Rating

IDSS Zero gate voltage drain current VDS = 0.8 Max Rating,

- - -1.0 mA

VGS = 0V, TA = 125°C

- -1.5 - VGS = -4.5V, VDS = -25V

ID(ON) On-state drain current A

- -3.0 - VGS = -10V, VDS = -25V

- - 7.5 VGS = -4.0V, ID = -0.25A

RDS(ON) Static drain-to-source on-state resistance - - 9.0 Ω VGS = -5.0V, ID = -1.0A

- - 7.0 VGS = -10V, ID = -2.0A

ΔRDS(ON) Change in RDS(ON) with temperature - - 1.0 %/OC VGS = -5.0V, ID = -0.25A

GFS Forward transconductance 290 - - mmho VDS = -10V, ID = -0.25A

CISS Input capacitance - 127 -

VGS = 0V,

COSS Common source output capacitance - 29 - pF VDS = -25V,

f = 1.0MHz

CRSS Reverse transfer capacitance - 9.0 -

td(ON) Turn-on delay time - 2.4 -

tr Rise time - 2.3 - VDD = -25V,

ns ID = -1.0A,

td(OFF) Turn-off delay time - 16.2 - RGEN = 25Ω

tf Fall time - 11.1 -

VSD Diode forward voltage drop - - -1.4 V VGS = 0V, ISD = -0.25A

trr Reverse recovery time - 80 - ns VGS = 0V, ISD = -0.25A

Notes:

1. All DC parameters 100% tested at 25°C unless otherwise stated. (Pulsed test: 300µs pulse at 2% duty cycle.)

2. All AC parameters sample tested.

P-Channel Switching Waveforms and Test Circuit

0V Pulse

10%

Generator

Input

RGEN

90%

-10V D.U.T.

t(ON t(OFF)

)

td(ON) tr td(OFF) tf Input

0V OUTPUT

90% 90%

Output

RL

VDD 10% 10%

VDD

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

3

TC6215

Block Diagram

SN 1 8 DN

GN 2 7 DN

N-Channel

SP 3 6 DP

GP 4 5 DP

P-Channel

8-Lead SOIC

(top view)

Typical Performance Curves

N-Channel Output Characteristics

P-Channel Output Characteristics 4.5

VGS =10V

-4.0

4.0

VGS=-10V VGS =8V

VGS =7V

-3.5 VGS =-8V

3.5

VGS=-7V

VGS =6V

-3.0 3.0

VGS=-6V

ID (amperes)

-2.5 2.5 VGS =5V

ID (amperes)

VGS=-5V

-2.0 2.0

-1.5 1.5 VGS =4V

VGS=-4V

-1.0 1.0

VGS=-3V VGS =3V

-0.5 0.5

VGS=-2V VGS =2V

0.0 0.0

0 -5 -10 -15 -20 -25 -30 -35 -40 -45 -50 0 5 10 15 20 25 30 35 40 45 50

VDS (volts) VDS (volts)

P-Channel Saturation Characteristics N-Channel Saturation Characteristics

4.0

-2.2

VGS=-10V

VGS=-8V VGS=10V

-2.0 3.5

VGS=-6V VGS=8V

-1.8 VGS=-5V

VGS=6V

3.0

-1.6

-1.4 2.5 VGS=5V

ID (amperes)

ID (amperes)

VGS=-4V

-1.2

2.0

-1.0

VGS=4V

1.5

-0.8

VGS=-3V

-0.6 1.0

-0.4 VGS=3V

0.5

-0.2

VGS=-2V

VGS=2V

0.0 0.0

0 -1 -2 -3 -4 -5 -6 -7 -8 -9 -10 0 1 2 3 4 5 6 7 8 9 10

VDS (volts) VDS (volts)

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

4

TC6215

8-Lead SOIC (Narrow Body) Package Outline (TG)

4.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

D θ1

E1

L2 Gauge

Note 1 Plane

(Index Area

D/2 x E1/2)

L Seating

θ

1 L1

Plane

Top View View B

A View B

Note 1

h

h

A A2

Seating

Plane

A1 e b

Side View A

View A-A

Note:

1. This chamfer feature is optional. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier;

an embedded metal marker; or a printed indicator.

Symbol A A1 A2 b D E E1 e h L L1 L2 θ θ1

MIN 1.35* 0.10 1.25 0.31 4.80* 5.80* 3.80* 0.25 0.40 0O 5O

Dimension 1.27 1.04 0.25

NOM - - - - 4.90 6.00 3.90 - - - -

(mm) BSC REF BSC

MAX 1.75 0.25 1.65* 0.51 5.00* 6.20* 4.00* 0.50 1.27 8O 15O

JEDEC Registration MS-012, Variation AA, Issue E, Sept. 2005.

* This dimension is not specified in the original JEDEC drawing. The value listed is for reference only.

Drawings are not to scale.

Supertex Doc. #: DSPD-8SOLGTG, Version H101708.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline

information go to http://www.supertex.com/packaging.html.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an

adequate “product liability indemnification insurance agreement.” Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the

replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications

are subject to change without notice. For the latest product specifications refer to the Supertex inc. website: http//www.supertex.com.

©2008 All rights reserved. Unauthorized use or reproduction is prohibited.

1235 Bordeaux Drive, Sunnyvale, CA 94089

Doc.# DSFP-TC6215 Tel: 408-222-8888

A122208 www.supertex.com

5

You might also like

- TN0606 N-Channel Enhancement-Mode Vertical DMOS FET: Features General DescriptionDocument5 pagesTN0606 N-Channel Enhancement-Mode Vertical DMOS FET: Features General DescriptionMuhammad ZahidNo ratings yet

- Datasheet MOSFET - 2N7000 - Supertex IIIDocument6 pagesDatasheet MOSFET - 2N7000 - Supertex IIICristian Daniel BerettaNo ratings yet

- 2N7002 N-Channel Enhancement-Mode Vertical Dmos Fets: Features General DescriptionDocument5 pages2N7002 N-Channel Enhancement-Mode Vertical Dmos Fets: Features General DescriptionG U I 2 KNo ratings yet

- 2N7000 N-Channel Enhancement-Mode Vertical Dmos Fets: Features General DescriptionDocument5 pages2N7000 N-Channel Enhancement-Mode Vertical Dmos Fets: Features General DescriptionNìcòlàs HedNo ratings yet

- Low Threshold DMOS FETs for Logic Level InterfacesDocument4 pagesLow Threshold DMOS FETs for Logic Level InterfacesSaikumarNo ratings yet

- EPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 ADocument6 pagesEPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 AЕвгений ИвановNo ratings yet

- N-Channel Vertical DMOS FET Spec SheetDocument3 pagesN-Channel Vertical DMOS FET Spec SheetThe ProgrammerNo ratings yet

- 2N7008Document3 pages2N7008efrenimaNo ratings yet

- EPC2036 - Enhancement Mode Power Transistor: V, 100 V R, 73 M I, 1.7 ADocument6 pagesEPC2036 - Enhancement Mode Power Transistor: V, 100 V R, 73 M I, 1.7 ALuisNo ratings yet

- EPC2020 Datasheet PDFDocument6 pagesEPC2020 Datasheet PDFblackslash82No ratings yet

- EPC2020 - Enhancement Mode Power Transistor: V, 60 V R, 2.2 mΩ I, 90 ADocument6 pagesEPC2020 - Enhancement Mode Power Transistor: V, 60 V R, 2.2 mΩ I, 90 Ablackslash82No ratings yet

- tph3206psb 20171130Document13 pagestph3206psb 20171130Gan XuekaiNo ratings yet

- VN10K N-Channel Enhancement-Mode Vertical DMOS FET: Features General DescriptionDocument5 pagesVN10K N-Channel Enhancement-Mode Vertical DMOS FET: Features General DescriptionJuan ArciniegasNo ratings yet

- 2n7002 SupertexDocument5 pages2n7002 Supertexjimmy146No ratings yet

- EPC2035 - Enhancement Mode Power Transistor: V, 60 V R, 45 M I, 1.7 ADocument6 pagesEPC2035 - Enhancement Mode Power Transistor: V, 60 V R, 45 M I, 1.7 AEdwin GualavisiNo ratings yet

- Httpswww.infineon.comdgdlInfineon BTT6010 1ERA DS v01 00 en.pdffileId=5546d46269e1c019016a21e7f3ce0d72#Page11Document46 pagesHttpswww.infineon.comdgdlInfineon BTT6010 1ERA DS v01 00 en.pdffileId=5546d46269e1c019016a21e7f3ce0d72#Page11muhammetNo ratings yet

- Vp0104 Vp0106 Vp0109 P-Channel Enhancement-Mode Vertical Dmos FetsDocument4 pagesVp0104 Vp0106 Vp0109 P-Channel Enhancement-Mode Vertical Dmos FetsGabriel RacovskyNo ratings yet

- A3946 Datasheet PDFDocument14 pagesA3946 Datasheet PDFcarlos.ramNo ratings yet

- EPC2020 - Enhancement Mode Power Transistor: V, 60 V R, 2.2 mΩ I, 90 ADocument6 pagesEPC2020 - Enhancement Mode Power Transistor: V, 60 V R, 2.2 mΩ I, 90 AEdwin GualavisiNo ratings yet

- Tph3202P Series: 600V Gan Fet To-220 SeriesDocument14 pagesTph3202P Series: 600V Gan Fet To-220 SeriesshounakroyNo ratings yet

- Rail to Rail Single Op Amp Drives 32Ω LoadsDocument3 pagesRail to Rail Single Op Amp Drives 32Ω LoadsKSNo ratings yet

- Ob 2223 HCDocument11 pagesOb 2223 HCRivaldyNo ratings yet

- DS3695 Multipoint RS485 RS422 Transceivers RepeatersDocument17 pagesDS3695 Multipoint RS485 RS422 Transceivers RepeatersJuan Gil Roca100% (1)

- Ordering Information: BV / R I BV (Max) (Min) TO-92 TO-243AA Die Order Number / PackageDocument4 pagesOrdering Information: BV / R I BV (Max) (Min) TO-92 TO-243AA Die Order Number / PackagerafinNo ratings yet

- VN2460 N-Channel Enhancement-Mode Vertical DMOS FET: Features General DescriptionDocument6 pagesVN2460 N-Channel Enhancement-Mode Vertical DMOS FET: Features General DescriptionClear PassNo ratings yet

- NE5230, SA5230, SE5230 Low Voltage Operational Amplifier: PDIP 8 N Suffix CASE 626 SOIC 8 D Suffix CASE 751Document18 pagesNE5230, SA5230, SE5230 Low Voltage Operational Amplifier: PDIP 8 N Suffix CASE 626 SOIC 8 D Suffix CASE 751Marcelo OemNo ratings yet

- DS2413 DatasheetDocument18 pagesDS2413 DatasheetDaniel RegoNo ratings yet

- VN0606 N-Channel Enhancement-Mode Vertical DMOS FET: Features General DescriptionDocument3 pagesVN0606 N-Channel Enhancement-Mode Vertical DMOS FET: Features General Descriptiony lNo ratings yet

- TC1413/TC1413N: 3A High-Speed MOSFET DriversDocument24 pagesTC1413/TC1413N: 3A High-Speed MOSFET DriverskarimNo ratings yet

- SM3331PSQG: Features Pin DescriptionDocument10 pagesSM3331PSQG: Features Pin DescriptionJesus MendezNo ratings yet

- Datasheet Bd9422efvDocument28 pagesDatasheet Bd9422efvj0rge avendañoNo ratings yet

- High Performance, Single Synchronous Step-Down Controller For Notebook Power SupplyDocument27 pagesHigh Performance, Single Synchronous Step-Down Controller For Notebook Power Supplyzigmund zigmundNo ratings yet

- For New Designs: Off-Line Quasi-Resonant Switching RegulatorsDocument9 pagesFor New Designs: Off-Line Quasi-Resonant Switching RegulatorsMEHMET AKMANNo ratings yet

- IRF6775MTR1PBFDocument10 pagesIRF6775MTR1PBFCesar martinezNo ratings yet

- Irf6775mpbf PDFDocument10 pagesIrf6775mpbf PDFMárcio FerreiraNo ratings yet

- SM4802DSK: Features Pin DescriptionDocument12 pagesSM4802DSK: Features Pin DescriptionRobson SilvaNo ratings yet

- SM 4303 PSKDocument11 pagesSM 4303 PSKIrvin Adan Lujan HernandezNo ratings yet

- SM3116NAF/SM3116NAFP: Pin Description FeaturesDocument10 pagesSM3116NAF/SM3116NAFP: Pin Description FeaturesRodney RibeiroNo ratings yet

- Ordering Information: Order Number / Package BV / R I BV (Max) (Min) TO-92Document4 pagesOrdering Information: Order Number / Package BV / R I BV (Max) (Min) TO-92sifibrNo ratings yet

- Infineon IRL3705N DS v01 - 02 ENDocument9 pagesInfineon IRL3705N DS v01 - 02 ENFrancisco Mendoza BalderasNo ratings yet

- DP2269Document7 pagesDP2269GABRIEL AMORIM ARAUJONo ratings yet

- Fdd390N15Alz: N-Channel Powertrench MosfetDocument9 pagesFdd390N15Alz: N-Channel Powertrench Mosfetserrano.flia.coNo ratings yet

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument8 pagesN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataErroz RosadiNo ratings yet

- SM4378NSKP SinopowerDocument12 pagesSM4378NSKP SinopowerLorena FigueroaNo ratings yet

- LMH0344 3Gbps HD/SD SDI Adaptive Cable Equalizer: PreliminaryDocument8 pagesLMH0344 3Gbps HD/SD SDI Adaptive Cable Equalizer: PreliminaryMartinNo ratings yet

- SM4833NSK SinopowerDocument11 pagesSM4833NSK SinopowerKuni KazeNo ratings yet

- fdp054n10 PDFDocument8 pagesfdp054n10 PDFAldi DwprstwnNo ratings yet

- APM4548K: Features Pin DescriptionDocument13 pagesAPM4548K: Features Pin DescriptionMauricio MartinNo ratings yet

- Irfi4019h 117PDocument8 pagesIrfi4019h 117PhazelmaedznNo ratings yet

- Auirfz 44 NDocument9 pagesAuirfz 44 NFrancisco BandresNo ratings yet

- APM4546Document13 pagesAPM4546Ridho MawardiNo ratings yet

- High Effi Ciency 1A/2A Current-Mode Synchronous Buck Converter, 1MhzDocument19 pagesHigh Effi Ciency 1A/2A Current-Mode Synchronous Buck Converter, 1MhzFeroz KhanNo ratings yet

- Pdt003a0x3-Srz LynxDocument39 pagesPdt003a0x3-Srz LynxefixlukasNo ratings yet

- Current Mode PWM Controller With Frequency Shuffling ME8202Document12 pagesCurrent Mode PWM Controller With Frequency Shuffling ME8202Kukla LossNo ratings yet

- Medium Power Surface Mount Products: Semiconductor Technical DataDocument10 pagesMedium Power Surface Mount Products: Semiconductor Technical DataStuxnetNo ratings yet

- NX4020HDocument4 pagesNX4020Holeg nakhimovichNo ratings yet

- SEMICONDUCTOR TECHNICAL DATA SHEETDocument11 pagesSEMICONDUCTOR TECHNICAL DATA SHEETJOSENo ratings yet

- The RF Mosfet Line N-Channel Enhancement-Mode Lateral MOSFETDocument12 pagesThe RF Mosfet Line N-Channel Enhancement-Mode Lateral MOSFETAlberto HertzNo ratings yet

- Identification of Nonlinear Systems: Volterra Series SimplificationDocument4 pagesIdentification of Nonlinear Systems: Volterra Series SimplificationfelipekillerNo ratings yet

- TC6215 N-And P-Channel Enhancement-Mode Dual MOSFET: Features General DescriptionDocument5 pagesTC6215 N-And P-Channel Enhancement-Mode Dual MOSFET: Features General DescriptionfelipekillerNo ratings yet

- Identification of Nonlinear Systems: Volterra Series SimplificationDocument4 pagesIdentification of Nonlinear Systems: Volterra Series SimplificationfelipekillerNo ratings yet

- Proweld Pickling Paste 20121019Document17 pagesProweld Pickling Paste 20121019felipekillerNo ratings yet

- Hardness Testing of Metals Proficiency Testing Program Round 13Document30 pagesHardness Testing of Metals Proficiency Testing Program Round 13felipekillerNo ratings yet

- Proweld Pickling Paste 20121019Document17 pagesProweld Pickling Paste 20121019felipekillerNo ratings yet

- Proweld Pickling Paste 20121019Document17 pagesProweld Pickling Paste 20121019felipekillerNo ratings yet

- Hardness Testing of Metals Proficiency Testing Program Round 13Document30 pagesHardness Testing of Metals Proficiency Testing Program Round 13felipekillerNo ratings yet

- Hardness Testing of Metals Proficiency Testing Program Round 13Document30 pagesHardness Testing of Metals Proficiency Testing Program Round 13felipekillerNo ratings yet

- National Talent Search Examination Path to SuccessDocument25 pagesNational Talent Search Examination Path to SuccessSudhanshuNo ratings yet

- Structural beam drawingsDocument1 pageStructural beam drawingsnathan kNo ratings yet

- Stoichiometry and Gravimetric Analysis of Strontium CarbonateDocument4 pagesStoichiometry and Gravimetric Analysis of Strontium CarbonateIbelise MederosNo ratings yet

- CrankcaseDocument7 pagesCrankcaseCharlie BellNo ratings yet

- TMS470 Assembly Language Tools User' S GuideDocument336 pagesTMS470 Assembly Language Tools User' S GuideMadhu CkNo ratings yet

- Understanding Gases Through Kinetic TheoryDocument20 pagesUnderstanding Gases Through Kinetic TheoryJaimeNo ratings yet

- XFOILDocument2 pagesXFOILbwwatsonNo ratings yet

- Wave Motion on a StringDocument17 pagesWave Motion on a StringAnkit JhaNo ratings yet

- EE5220 Project TRV CBRatings ReportDocument22 pagesEE5220 Project TRV CBRatings ReportsasikalasivakumarNo ratings yet

- Jackson 4 10 Homework Solution PDFDocument5 pagesJackson 4 10 Homework Solution PDFarmhein64No ratings yet

- The Van Der Pauw Method of Measurements in High-TcDocument12 pagesThe Van Der Pauw Method of Measurements in High-TcNolbert Renzo Umpire IncaNo ratings yet

- JBM Report (20331) MEDocument30 pagesJBM Report (20331) MEKshitijKumarNo ratings yet

- Vingcard ManualDocument202 pagesVingcard ManualPenta Guard50% (10)

- CFM To LFM CalculationDocument7 pagesCFM To LFM Calculationudilevy100% (1)

- Mac Green Button EN PDFDocument5 pagesMac Green Button EN PDFVanessa ManriqueNo ratings yet

- HeatDocument31 pagesHeatnicky1213a100% (1)

- High Grade Water Soluble SOP For FertigationDocument2 pagesHigh Grade Water Soluble SOP For FertigationRómulo Del ValleNo ratings yet

- Solar Assisted Air Conditioning of Buildings - An OverviewDocument16 pagesSolar Assisted Air Conditioning of Buildings - An OverviewoilladdaNo ratings yet

- Bullheading Calculation Example Pressure ScheduleDocument10 pagesBullheading Calculation Example Pressure ScheduleazizsarshoghNo ratings yet

- Introduction to Weibull Analysis for Reliability ImprovementDocument2 pagesIntroduction to Weibull Analysis for Reliability ImprovementCesar ChpNo ratings yet

- 11th Science Maths Answer KeyDocument15 pages11th Science Maths Answer KeyBhavesh AsapureNo ratings yet

- M.Sc. MATHEMATICS MODEL PAPERDocument22 pagesM.Sc. MATHEMATICS MODEL PAPERRatnesh RanjanNo ratings yet

- Multi-Hole Orifice CalculationDocument10 pagesMulti-Hole Orifice Calculationadrianrrcc100% (1)

- PSTrace 5.6 Manual 2Document100 pagesPSTrace 5.6 Manual 2Juan Daniel Sarmiento AbelloNo ratings yet

- Pureroutines: SmoothnessDocument11 pagesPureroutines: SmoothnessJohn PauloNo ratings yet

- Configure NTP Server on Cisco WLC via CLIDocument3 pagesConfigure NTP Server on Cisco WLC via CLImbayeNo ratings yet

- 14EIT72 Instrumentation System Design UNIT-V - P&I Diagrams and Instrument InstallationDocument38 pages14EIT72 Instrumentation System Design UNIT-V - P&I Diagrams and Instrument Installationksjanarthanan_sriNo ratings yet

- Metal-Catalyzed Epoxidations of Alkenes With Hydrogen PeroxideDocument18 pagesMetal-Catalyzed Epoxidations of Alkenes With Hydrogen PeroxidechidambaramrNo ratings yet

- Royal College Grade 08 Geography First Term Paper English MediumDocument7 pagesRoyal College Grade 08 Geography First Term Paper English MediumNimali Dias67% (3)

- 12TH CS TERM 2 - PythonDocument8 pages12TH CS TERM 2 - PythonAnbuchelvan VKNo ratings yet