Professional Documents

Culture Documents

Experiment No.: 7: Advanced Digital System Design

Uploaded by

samrudhiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Experiment No.: 7: Advanced Digital System Design

Uploaded by

samrudhiCopyright:

Available Formats

ADVANCED DIGITAL SYSTEM DESIGN

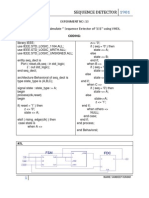

EXPERIMENT NO. : 7

Design a Sequence Detector which detects a sequence 1001 using MEALY

AIM: and MOORE FSM using VHDL and Verify them by using XILINX Simulator.

The Objective of this experiment is to design sequence detector using Mealy

and Moore circuit for sequence 1001 in Xilinx 14.1 ISE Design suite tool, and to

OBJECTIVE: test the circuit using test bench where outputs are observed for different

inputs.

STATE

DIAGRAM:

VHDL CODE: VHDL code for “1001” using MEALY circuit:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY MEALY IS

PORT (X, CLK: IN STD_LOGIC;

Z: OUT STD_LOGIC);

END MEALY;

ARCHITECTURE Behavioral OF MEALY IS

TYPE State IS (A, B, C, D);

Department of Electronics & Telecommunication Engineering, RGCER, Nagpur Page 1 of 8

ADVANCED DIGITAL SYSTEM DESIGN

SIGNAL Y: State;

BEGIN

PROCESS (X, CLK)

BEGIN

IF (CLK = ‘1’ and CLK’EVENT)

THEN

CASE Y IS

WHEN A=> IF (X=’0’)

THEN Y<=A;

Z<= ‘0’;

ELSE Y<=B;

Z<= ‘0’;

END IF;

WHEN B=> IF (X=’0’)

THEN Y<=C;

Z<= ‘0’;

ELSE Y<=B;

Z<= ‘0’;

END IF;

WHEN C=> IF (X=’0’)

THEN Y<=D;

Z<= ‘0’;

ELSE Y<=B;

Z<= ‘0’;

END IF;

WHEN D=> IF (X=’0’)

THEN Y<=A;

Z<= ‘0’;

ELSE Y<=B;

Department of Electronics & Telecommunication Engineering, RGCER, Nagpur Page 2 of 8

ADVANCED DIGITAL SYSTEM DESIGN

Z<= ‘1’;

END IF;

WHEN OTHERS=> NULL;

END CASE;

END IF;

END PROCESS;

END behavioral;

VHDL code for “1001” using MOORE circuit:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY MOORE IS

PORT (X, CLK: IN STD_LOGIC;

Z: OUT STD_LOGIC);

END MOORE;

ARCHITECTURE Behavioral OF MOORE IS

TYPE State IS (A, B, C, D, E);

SIGNAL Y: State;

BEGIN

PROCESS (X, CLK)

BEGIN

IF (CLK = ‘1’ and CLK’EVENT)

THEN

CASE Y IS

WHEN A=> IF (X=’0’)

THEN Y<=A;

Department of Electronics & Telecommunication Engineering, RGCER, Nagpur Page 3 of 8

ADVANCED DIGITAL SYSTEM DESIGN

ELSE Y<=B;

END IF;

Z<= ‘0’;

WHEN B=> IF (X=’0’)

THEN Y<=C;

ELSE Y<=B;

END IF;

Z<= ‘0’;

WHEN C=> IF (X=’0’)

THEN Y<=D;

ELSE Y<=B;

END IF;

Z<= ‘0’;

WHEN D=> IF (X=’0’)

THEN Y<=A;

ELSE Y<=E;

END IF;

Z<= ‘0’;

WHEN E=> IF (X=’0’)

THEN Y<=C;

ELSE Y<=B;

END IF;

Z<= ‘1’;

WHEN OTHERS=> NULL;

END CASE;

END IF;

END PROCESS;

END behavioral;

Department of Electronics & Telecommunication Engineering, RGCER, Nagpur Page 4 of 8

ADVANCED DIGITAL SYSTEM DESIGN

TEST BENCH: Test Bench for MEALY circuit:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY TEST IS

END TEST;

ARCHITECTURE behavior OF TEST IS

COMPONENT MEALY

PORT (CLK, X: IN STD_LOGIC;

Z: OUT STD_LOGIC);

END COMPONENT;

SIGNAL CLK: STD_LOGIC:= '0';

SIGNAL X: STD_LOGIC:= '0';

SIGNAL Z: STD_LOGIC;

CONSTANT CLK_period: TIMEB := 100 ns;

BEGIN

uut: MEALY PORT MAP (CLK => CLK, X => X, Z => Z);

CLK_process: PROCESS

BEGIN

CLK <= '0';

WAIT FOR CLK_period/2;

CLK <= '1';

WAIT FOR CLK_period/2;

END PROCESS;

stim_proc: PROCESS

BEGIN

Department of Electronics & Telecommunication Engineering, RGCER, Nagpur Page 5 of 8

ADVANCED DIGITAL SYSTEM DESIGN

X<='1';

WAIT FOR 100 NS;

X<='0';

WAIT FOR 100 NS;

X<='0';

WAIT FOR 100 NS;

X<='1';

WAIT FOR 100 NS;

END PROCESS;

END;

Test Bench for MOORE circuit:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY TEST IS

END TEST;

ARCHITECTURE behavior OF TEST IS

COMPONENT MOORE

PORT (CLK, X: IN STD_LOGIC;

Z: OUT STD_LOGIC);

END COMPONENT;

SIGNAL CLK: STD_LOGIC:= '0';

SIGNAL X: STD_LOGIC:= '0';

SIGNAL Z: STD_LOGIC;

CONSTANT CLK_period: TIME := 100 ns;

Department of Electronics & Telecommunication Engineering, RGCER, Nagpur Page 6 of 8

ADVANCED DIGITAL SYSTEM DESIGN

BEGIN

uut: MOORE PORT MAP (CLK => CLK, X => X, Z => Z);

CLK_process: PROCESS

BEGIN

CLK <= '0';

WAIT FOR CLK_period/2;

CLK <= '1';

WAIT FOR CLK_period/2;

END PROCESS;

stim_proc: PROCESS

BEGIN

X<='1';

WAIT FOR 100 NS;

X<='0';

WAIT FOR 100 NS;

X<='0';

WAIT FOR 100 NS;

X<='1';

WAIT FOR 100 NS;

END PROCESS;

END;

Department of Electronics & Telecommunication Engineering, RGCER, Nagpur Page 7 of 8

ADVANCED DIGITAL SYSTEM DESIGN

MEALY CIRCUIT:

SIMULATION

RESULTS:

MOORE CIRCUIT:

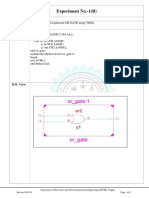

MEALY CIRCUIT:

RTL

SCHEMATIC:

MOORE CIRCUIT:

RESULT/ Thus we have successfully design sequence detector using Mealy and Moore

CONCLUSION: circuit using XILINX tools and verified the simulation result.

ROLL NO.: 17

NAME &

NAME: SAMRUDHI CHARDE MARKS SIGNATURE

OUT OF 15 OF SUBJECT

TEACHER Prof. Pradnya

SEM/ BRANCH: VII/ETC-A Maturkar

Department of Electronics & Telecommunication Engineering, RGCER, Nagpur Page 8 of 8

You might also like

- Practica No6 - Grupo#7Document11 pagesPractica No6 - Grupo#7Josue BanchonNo ratings yet

- VHDL Cheat SheetDocument2 pagesVHDL Cheat SheetWilson WangNo ratings yet

- VHDL Cheat SheetDocument2 pagesVHDL Cheat SheetDaniloMoceriNo ratings yet

- Diseño ImprimirDocument4 pagesDiseño ImprimirRenato ValverdeNo ratings yet

- Exam1 (Example With Solutions)Document5 pagesExam1 (Example With Solutions)Rüya Gïbî100% (1)

- Trabajo de Diseño02Document10 pagesTrabajo de Diseño02Victor yurivilca lazoNo ratings yet

- Trabajo de Diseño02Document10 pagesTrabajo de Diseño02Alvaro SegoviaNo ratings yet

- FPGA应用举例Document12 pagesFPGA应用举例lieshi2958100% (1)

- Experiment-1: Simulation Result For Half Adder and Full Adder CircuitDocument7 pagesExperiment-1: Simulation Result For Half Adder and Full Adder CircuitHimanshu Rajan jainNo ratings yet

- Some VHDL CodesDocument11 pagesSome VHDL CodesFABIO DAVID HERNANDEZ MARTINEZNo ratings yet

- Code VHDL Trascodeur 7 SegmentsDocument5 pagesCode VHDL Trascodeur 7 SegmentsBen Ahmed AbdelhamidNo ratings yet

- VHDL Slides For Cstruct Mux & DecoderDocument30 pagesVHDL Slides For Cstruct Mux & DecoderLiron lNo ratings yet

- Bài 1: thiết kế mạch giải mã 3 -8Document7 pagesBài 1: thiết kế mạch giải mã 3 -8Thắng TrầnNo ratings yet

- ECE380 Digital Logic: Design of Finite State Machines Using CAD ToolsDocument6 pagesECE380 Digital Logic: Design of Finite State Machines Using CAD Toolspurwant10168No ratings yet

- RegistruDocument2 pagesRegistruMoniNo ratings yet

- Actividad PrácticaDocument4 pagesActividad PrácticaJL RodriguezNo ratings yet

- CodigoDocument4 pagesCodigoJL RodriguezNo ratings yet

- Using Case Statement VHDL Code:: Assignment 2Document15 pagesUsing Case Statement VHDL Code:: Assignment 2innovatorinnovatorNo ratings yet

- Up Counter 7 Segment Display Using Clock Divider CircuitDocument7 pagesUp Counter 7 Segment Display Using Clock Divider CircuitRavindra Mathanker50% (2)

- Electiva - CIRCUITOS SECUENCIALES EN VHDLDocument5 pagesElectiva - CIRCUITOS SECUENCIALES EN VHDLfer gutiNo ratings yet

- hw1 PDFDocument3 pageshw1 PDFDevaraj SubrmanayamNo ratings yet

- Experiment No.1: A Binary To Gray ConverterDocument26 pagesExperiment No.1: A Binary To Gray ConverterVarun SharmaNo ratings yet

- VHDL Quick Guide PDFDocument2 pagesVHDL Quick Guide PDFMorian CalderónNo ratings yet

- Sequence Detector: Experiment No: 10 Activity: To Design and Simulate ' Sequence Detector of 101'' Using VHDLDocument2 pagesSequence Detector: Experiment No: 10 Activity: To Design and Simulate ' Sequence Detector of 101'' Using VHDLSaurabh KhandelwalNo ratings yet

- S1 Not (A Xor B) S2 Not D or (C and D) S S2 and (E Xor S1)Document11 pagesS1 Not (A Xor B) S2 Not D or (C and D) S S2 and (E Xor S1)oussama elkaissiNo ratings yet

- Semafor oDocument4 pagesSemafor oJosVe Lasteros ALferesNo ratings yet

- Diseño Digital ProblemasDocument36 pagesDiseño Digital ProblemasRenato ValverdeNo ratings yet

- Combinational Logic Circuits: Prof. David Márquez ViloriaDocument16 pagesCombinational Logic Circuits: Prof. David Márquez ViloriaJose Mateo Aristizabal DiazNo ratings yet

- Programa de Proyecto ALUDocument6 pagesPrograma de Proyecto ALUALAN RAUL ROMERO HERNANDEZNo ratings yet

- Dcs-Ii Lab File: - Anupam Sobti 17/EC/09Document19 pagesDcs-Ii Lab File: - Anupam Sobti 17/EC/09Ankit GoelNo ratings yet

- Write A Code For 7 - Segment Display ProgramDocument2 pagesWrite A Code For 7 - Segment Display Programeshwar_worldNo ratings yet

- 26 October - 20 November, 2009: VHDL & FPGA Architecturs Synthesis III - Advanced VHDLDocument44 pages26 October - 20 November, 2009: VHDL & FPGA Architecturs Synthesis III - Advanced VHDLJulio César Millán BarcoNo ratings yet

- 26 October - 20 November, 2009: VHDL & FPGA Architecturs Synthesis III - Advanced VHDLDocument44 pages26 October - 20 November, 2009: VHDL & FPGA Architecturs Synthesis III - Advanced VHDLJulio César Millán BarcoNo ratings yet

- Subiecte Tip Examen Vlsi1Document21 pagesSubiecte Tip Examen Vlsi1Iuli SirbuNo ratings yet

- Họ và tên: Lê Hồng Phú MSSV: 41801040 Bài tập 6 - buổi học 20211030Document8 pagesHọ và tên: Lê Hồng Phú MSSV: 41801040 Bài tập 6 - buổi học 20211030Hồng PhúNo ratings yet

- Impletar en VHDL La Siguiente Maquina de EstadosDocument10 pagesImpletar en VHDL La Siguiente Maquina de EstadosGian SusanaNo ratings yet

- Implemente Un Contador de 3 A 9, Si La Salida Del Contador Es Mayor Al Último Digito de Tu Código de Alumno Activa La SalidaDocument5 pagesImplemente Un Contador de 3 A 9, Si La Salida Del Contador Es Mayor Al Último Digito de Tu Código de Alumno Activa La SalidaFarromeque Eyzaguirre Luis EnriqueNo ratings yet

- 2) Verify The Behavior of Logic Gates Using Truth Tables (AND, OR, NOT, XOR, NAND, NOR, XNOR)Document9 pages2) Verify The Behavior of Logic Gates Using Truth Tables (AND, OR, NOT, XOR, NAND, NOR, XNOR)SyamPvpsitNo ratings yet

- ESProg 8 IIDocument8 pagesESProg 8 II20BCS010Anzil MuftiNo ratings yet

- Tugas8 - 2210191006 - Filosofi Dwibakti - LapsemDocument23 pagesTugas8 - 2210191006 - Filosofi Dwibakti - LapsemFD SyndromeNo ratings yet

- Mandelbrot ZoomDocument5 pagesMandelbrot ZoommorrisblausteinNo ratings yet

- Digital Technology - Lecture 7Document7 pagesDigital Technology - Lecture 7Jan Kisak RasmussenNo ratings yet

- Tutorial 1Document29 pagesTutorial 1A'ziz MoNo ratings yet

- Decodificador BCD A 7Document2 pagesDecodificador BCD A 7Luis Dela RosaNo ratings yet

- D FF CodeDocument2 pagesD FF Codebhslegion1498No ratings yet

- CA PracticalDocument11 pagesCA PracticalBidhan BaraiNo ratings yet

- Entity MOORE IsDocument1 pageEntity MOORE Issina esmaeilianNo ratings yet

- Unit 3: Combinational Circuit DesignDocument30 pagesUnit 3: Combinational Circuit DesignKarn AroraNo ratings yet

- HDL Experiment3Document3 pagesHDL Experiment3choudharyarjun1121No ratings yet

- Half AdderDocument11 pagesHalf AdderTahsin RahmanNo ratings yet

- FA (BHVR) - CodeDocument1 pageFA (BHVR) - Codebhslegion1498No ratings yet

- Interrogation 1: Nom: Prenom: ..Document3 pagesInterrogation 1: Nom: Prenom: ..capoNo ratings yet

- VHDFFDocument4 pagesVHDFFAmirul AsyrafNo ratings yet

- CodeDocument3 pagesCodeRayen AskriNo ratings yet

- Divisor de Frecuencia de 50 MHZ A 10 HZDocument8 pagesDivisor de Frecuencia de 50 MHZ A 10 HZAlexis Espinoza HilarioNo ratings yet

- VHDL Tutorial: Nand GatesDocument11 pagesVHDL Tutorial: Nand GatessikopikoNo ratings yet

- Ddec 7Document1 pageDdec 7Henry VenturaNo ratings yet

- Name String Mobilenumber String Username String Password StringDocument2 pagesName String Mobilenumber String Username String Password Stringsamrudhi0% (1)

- Itemtype Details in A File: ProblemDocument2 pagesItemtype Details in A File: ProblemsamrudhiNo ratings yet

- Fixed Length FormatDocument3 pagesFixed Length FormatsamrudhiNo ratings yet

- File Handling IntroductionDocument2 pagesFile Handling Introductionsamrudhi50% (4)

- Fixed Length FormatDocument3 pagesFixed Length FormatsamrudhiNo ratings yet

- Experiment No.: 10Document5 pagesExperiment No.: 10samrudhiNo ratings yet

- FactorialDocument1 pageFactorialsamrudhiNo ratings yet

- HTMLDocument1 pageHTMLsamrudhiNo ratings yet

- 97 JavabeansDocument60 pages97 Javabeanskunal2104No ratings yet

- ServerDocument1 pageServerSamrudhiNo ratings yet

- In The StoryDocument2 pagesIn The StorysamrudhiNo ratings yet

- Sunlife Job DescriptionDocument3 pagesSunlife Job DescriptionsamrudhiNo ratings yet

- European Telecommunications Standards Institute 2G Cellular Networks FinlandDocument1 pageEuropean Telecommunications Standards Institute 2G Cellular Networks FinlandsamrudhiNo ratings yet

- IBPS PO Syllabus PDFDocument3 pagesIBPS PO Syllabus PDFsadafmirzaNo ratings yet

- Programming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)Document227 pagesProgramming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)michelrojar74% (39)

- Irjet V4i5282 PDFDocument4 pagesIrjet V4i5282 PDFBilla NehruNo ratings yet

- Experiment No.-1 (B) : Date of Performance:13/7/18Document2 pagesExperiment No.-1 (B) : Date of Performance:13/7/18samrudhiNo ratings yet

- Mini Electronics ProjectDocument224 pagesMini Electronics Projectriju100% (1)

- Capgemini Placement Papers 2012Document2 pagesCapgemini Placement Papers 2012SamrudhiNo ratings yet

- EC2015 7semand8th PDFDocument47 pagesEC2015 7semand8th PDFnadeemq_0786No ratings yet

- 5Kw RF Power Amplifier: - Preliminary SpecificationDocument4 pages5Kw RF Power Amplifier: - Preliminary SpecificationMohamed belhasanNo ratings yet

- Raf2582 Raf2585Document2 pagesRaf2582 Raf2585Muhammad MustafaNo ratings yet

- Pioneer SK 909lDocument19 pagesPioneer SK 909lErnandesTorresBarbosaNo ratings yet

- Expt-5 Lab Manual TE LabDocument10 pagesExpt-5 Lab Manual TE LabRuham RofiqueNo ratings yet

- b7 Transmission Lines 2 - Comm TheoremDocument37 pagesb7 Transmission Lines 2 - Comm Theoremhafiz azmanNo ratings yet

- PPC LDF4 Install Inst - Hand ToolDocument2 pagesPPC LDF4 Install Inst - Hand ToolTower_DocNo ratings yet

- 056-022 Switchgear ControlDocument4 pages056-022 Switchgear ControlSon Do100% (1)

- Project Report On Electronic StethoscopeDocument85 pagesProject Report On Electronic StethoscopeMohit Rana87% (23)

- SattCon 05-OP Programmers ManualDocument4 pagesSattCon 05-OP Programmers ManualGilbert H. Quiroga G.0% (1)

- JSSC 1968 1049925Document9 pagesJSSC 1968 1049925GowthamNo ratings yet

- Sy7208 PDFDocument4 pagesSy7208 PDFBuzatu GianiNo ratings yet

- ISP Technologies DAAT Power Amplifier Technology White Paper PDFDocument9 pagesISP Technologies DAAT Power Amplifier Technology White Paper PDFHumberto D PertuzNo ratings yet

- Chapter 3 - Input and OutputDocument61 pagesChapter 3 - Input and Outputannie69007No ratings yet

- PLCDocument87 pagesPLCAnoop RaviNo ratings yet

- 28Nm and Below, New Path and Beyond: Danny Rittman PHDDocument15 pages28Nm and Below, New Path and Beyond: Danny Rittman PHDAbhesh Kumar TripathiNo ratings yet

- Aoc Le32w136 LCD TVDocument82 pagesAoc Le32w136 LCD TVmanlu1001565100% (1)

- LCD TV 47LG70 Service ManualDocument36 pagesLCD TV 47LG70 Service Manualrhignite100% (1)

- Routine Production Testing of Voltage RegulatorsDocument2 pagesRoutine Production Testing of Voltage RegulatorssoltaniNo ratings yet

- LIS331DLH DatasheetDocument38 pagesLIS331DLH DatasheetSergio GonzalezNo ratings yet

- EE101L Experiment 8Document8 pagesEE101L Experiment 8Mark Franz TemplonuevoNo ratings yet

- F15 Maintenance MANUALDocument420 pagesF15 Maintenance MANUALSøren Andersen0% (1)

- Features and Benefits of Zuken PCB Design SoftwareDocument8 pagesFeatures and Benefits of Zuken PCB Design SoftwarejackNo ratings yet

- Datasheet ADF-3502 PrimeLine Navigation 05juni09Document2 pagesDatasheet ADF-3502 PrimeLine Navigation 05juni09Arun SasiNo ratings yet

- Lec 17Document20 pagesLec 17Nikhil NaikNo ratings yet

- Camara Domo CNB LBM20SDocument1 pageCamara Domo CNB LBM20STecnoSmartNo ratings yet

- G.Narayanamma Institute of Technology & Science: (Autonomous) (For Women) Course PlanDocument3 pagesG.Narayanamma Institute of Technology & Science: (Autonomous) (For Women) Course PlanLeela KrishnaNo ratings yet

- TIs Medical Technology JournalDocument34 pagesTIs Medical Technology JournalFawadNo ratings yet

- JESD282B01Document185 pagesJESD282B01Duram_Han_2546No ratings yet

- Chapter 8Document7 pagesChapter 8Salvador FayssalNo ratings yet

- Automatic Train Collision and Accident Avoidance SystemDocument22 pagesAutomatic Train Collision and Accident Avoidance SystemAbdul RazzakNo ratings yet