Professional Documents

Culture Documents

N-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference Data

Uploaded by

reparacionesdmaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

N-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference Data

Uploaded by

reparacionesdmaCopyright:

Available Formats

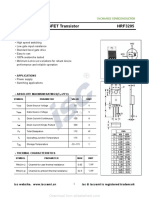

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

FEATURES SYMBOL QUICK REFERENCE DATA

• ’Trench’ technology d

• Low on-state resistance VDSS = 200 V

• Fast switching

• Low thermal resistance ID = 5.2 A

g

RDS(ON) ≤ 400 mΩ

s

GENERAL DESCRIPTION

N-channel, enhancement mode field-effect power transistor using Trench technology, intended for use in off-line

switched mode power supplies, T.V. and computer monitor power supplies, d.c. to d.c. converters, motor control circuits

and general purpose switching applications.

The PHX9NQ20T is supplied in the SOT186A (FPAK) conventional leaded package

PINNING SOT186A (FPAK) SOT186 (FPAK)

PIN DESCRIPTION

case case

1 gate

2 drain

3 source

case isolated 1 2 3 1 2 3

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VDSS Drain-source voltage Tj = 25 ˚C to 175˚C - 200 V

VDGR Drain-gate voltage Tj = 25 ˚C to 175˚C; RGS = 20 kΩ - 200 V

VGS Gate-source voltage - ± 20 V

ID Continuous drain current Ths = 25 ˚C; VGS = 10 V - 5.2 A

Ths = 100 ˚C; VGS = 10 V - 3.3 A

IDM Pulsed drain current Ths = 25 ˚C - 21 A

PD Total power dissipation Ths = 25 ˚C - 25 W

Tj, Tstg Operating junction and - 55 150 ˚C

storage temperature

November 2000 1 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

EAS Non-repetitive avalanche Unclamped inductive load, IAS = 7.2A; - 93 mJ

energy tp = 100 µs; Tj prior to avalanche = 25˚C;

VDD ≤ 25 V; RGS = 50 Ω; VGS = 10 V; refer

to fig;15

IAS Peak non-repetitive - 8.7 A

avalanche current

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Rth j-hs Thermal resistance junction - - 5 K/W

to mounting base

Rth j-a Thermal resistance junction SOT186A package, in free air - 55 - K/W

to ambient

ELECTRICAL CHARACTERISTICS

Tj= 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V(BR)DSS Drain-source breakdown VGS = 0 V; ID = 0.25 mA; 200 - - V

voltage Tj = -55˚C 178 - - V

VGS(TO) Gate threshold voltage VDS = VGS; ID = 1 mA 2 3 4 V

Tj = 150˚C 1 - - V

Tj = -55˚C - 6 V

RDS(ON) Drain-source on-state VGS = 10 V; ID = 4.5 A - 300 400 mΩ

resistance Tj = 150˚C - - 0.94 Ω

gfs Forward transconductance VDS = 25 V; ID = 4.5 A 3.8 6 - S

IGSS Gate source leakage current VGS = ± 10 V; VDS = 0 V - 10 100 nA

IDSS Zero gate voltage drain VDS = 200 V; VGS = 0 V - 0.05 10 µA

current Tj = 150˚C - - 500 µA

Qg(tot) Total gate charge ID = 9 A; VDD = 160 V; VGS = 10 V - 24 - nC

Qgs Gate-source charge - 4 - nC

Qgd Gate-drain (Miller) charge - 12 - nC

td on Turn-on delay time VDD = 100 V; RD = 10 Ω; - 8 - ns

tr Turn-on rise time VGS = 10 V; RG = 5.6 Ω - 19 - ns

td off Turn-off delay time Resistive load - 25 - ns

tf Turn-off fall time - 15 - ns

Ld Internal drain inductance Measured from drain lead to centre of die - 4.5 - nH

Ls Internal source inductance Measured from source lead to source - 7.5 - nH

bond pad

Ciss Input capacitance VGS = 0 V; VDS = 25 V; f = 1 MHz - 959 - pF

Coss Output capacitance - 93 - pF

Crss Feedback capacitance - 54 - pF

November 2000 2 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IS Continuous source current - - 8.7 A

(body diode)

ISM Pulsed source current (body - - 35 A

diode)

VSD Diode forward voltage IF = 9 A; VGS = 0 V - 0.85 1.2 V

trr Reverse recovery time IF = 9 A; -dIF/dt = 100 A/µs; - 92 - ns

Qrr Reverse recovery charge VGS = -10 V; VR = 25 V - 0.5 - µC

ISOLATION LIMITING VALUE & CHARACTERISTIC

Ths = 25 ˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Visol R.M.S. isolation voltage from all SOT186A package; f = 50-60 Hz; - 2500 V

three terminals to external sinusoidal waveform; R.H. ≤ 65%;

heatsink clean and dustfree

Visol Repetitive peak voltage from all SOT186 package; R.H. ≤ 65%; - 1500 V

three terminals to external clean and dustfree

heatsink

Cisol Capacitance from pin 2 to f = 1 MHz - 10 - pF

external heatsink

November 2000 3 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

Normalised Power Derating Transient thermal impedance, Zth j-a (K/W)

PD% 10

120

with heatsink compound

110

D = 0.5

100

90 0.2

80 1

0.1

70

0.05

60

50 0.02

40 0.1

30

20 single pulse

10

0 0.01

0 20 40 60 80 100 120 140 1E-06 1E-05 1E-04 1E-03 1E-02 1E-01 1E+00 1E+01

Ths / C Pulse width, tp (s)

Fig.1. Normalised power dissipation. Fig.4. Transient thermal impedance.

PD% = 100⋅PD/PD 25 ˚C = f(Tmb) Zth j-mb = f(t); parameter D = tp/T

ID% Normalised Current Derating Drain Current, ID (A)

120 10

with heatsink compound Tj = 25 C VGS = 10V 6V

110 9

8V

100 8

90 5.5 V

7

80

6

70

60 5

50 4 5V

40 3

30

2

20 4.5 V

1

10

0 0

0 20 40 60 80 100 120 140 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

Ths / C Drain-Source Voltage, VDS (V)

Fig.2. Normalised continuous drain current. Fig.5. Typical output characteristics, Tj = 25 ˚C.

ID% = 100⋅ID/ID 25 ˚C = f(Tmb); VGS ≥ 10 V ID = f(VDS)

Peak Pulsed Drain Current, IDM (A)

100 Drain-Source On Resistance, RDS(on) (Ohms)

0.5

4.5 V 5V Tj = 25 C

RDS(on) = VDS/ ID 0.45

0.4

10 0.35

tp = 10 us 0.3 5.5 V

0.25 6V

100us

0.2

1 1 ms

0.15 VGS = 10V

D.C. 10 ms 8V

0.1

100 ms

0.05

0.1 0

1 10 100 1000 0 1 2 3 4 5 6 7 8 9 10

Drain-Source Voltage, VDS (V) Drain Current, ID (A)

Fig.3. Safe operating area Fig.6. Typical on-state resistance, Tj = 25 ˚C.

ID & IDM = f(VDS); IDM single pulse; parameter tp RDS(ON) = f(ID)

November 2000 4 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

Drain current, ID (A) Threshold Voltage, VGS(TO) (V)

10 4.5

9 4

8

3.5

7

3

6

2.5

5

2

4

150 C 1.5

3

2 Tj = 25 C 1

1 0.5

0 0

0 1 2 3 4 5 6 -60 -40 -20 0 20 40 60 80 100 120 140 160

Gate-source voltage, VGS (V) Junction Temperature, Tj (C)

Fig.7. Typical transfer characteristics. Fig.10. Gate threshold voltage.

ID = f(VGS) VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

Transconductance, gfs (S) Drain current, ID (A)

14 1.0E-01

13

12

11 1.0E-02

10

9 Tj = 25 C minimum

8 1.0E-03

7

typical

6 150 C

1.0E-04

5

4 maximum

3 1.0E-05

2

1

0 1.0E-06

0 1 2 3 4 5 6 7 8 9 10 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5

ID / (A) Gate-source voltage, VGS (V)

Fig.8. Typical transconductance, Tj = 25 ˚C. Fig.11. Sub-threshold drain current.

gfs = f(ID) ID = f(VGS); conditions: Tj = 25 ˚C

Normalised On-state Resistance

2.5

Capacitances, Ciss, Coss, Crss (pF)

10000

2

Ciss

1.5 1000

1

Coss

100

0.5

Crss

0 10

-60 -40 -20 0 20 40 60 80 100 120 140 160 0.1 1 10 100

Junction Temperature, Tj C Drain-Source Voltage, VDS (V)

Fig.9. Normalised drain-source on-state resistance. Fig.12. Typical capacitances, Ciss, Coss, Crss.

RDS(ON)/RDS(ON)25 ˚C = f(Tj) C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

November 2000 5 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

Gate-source voltage, VGS (V)

15 Maximum Avalanche Current, IAS (A)

14 ID = 9 A 10

13 Tj = 25 C

12

VDD = 40 V

11

10 25 C

9 VDD = 160 V

8

7 1 Tj prior to avalanche = 150 C

6

5

4

3

2

1

0 0.1

0 5 10 15 20 25 30 35 0.001 0.01 0.1 1 10

Gate charge, QG (nC) Avalanche time, tAV (ms)

Fig.13. Typical turn-on gate-charge characteristics. Fig.15. Maximum permissible non-repetitive

VGS = f(QG) avalanche current (IAS) versus avalanche time (tAV);

unclamped inductive load

Source-Drain Diode Current, IF (A)

10

9

VGS = 0 V

8

7

6 150 C

5 Tj = 25 C

4

3

2

1

0

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2

Source-Drain Voltage, VSDS (V)

Fig.14. Typical reverse diode current.

IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

November 2000 6 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

MECHANICAL DATA

Dimensions in mm Plastic single-ended package; isolated heatsink mounted; 1 mounting hole; 3 lead TO-220 SOT186A

Net Mass: 2 g

E A

P A1

q

D1

T

L2 L1

K

Q

b1

L b2

1 2 3

b w M c

e

e1

0 5 10 mm

scale

DIMENSIONS (mm are the original dimensions)

(1) (2)

UNIT A A1 b b1 b2 c D D1 E e e1 j K L L1 L2 P Q q T w

max.

mm 4.6 2.9 0.9 1.1 1.4 0.7 15.8 6.5 10.3 2.7 0.6 14.4 3.30 3.2 2.6 3.0

2.54 5.08 3 2.5 0.4

4.0 2.5 0.7 0.9 1.2 0.4 15.2 6.3 9.7 2.3 0.4 13.5 2.79 3.0 2.3 2.6

Notes

1. Terminal dimensions within this zone are uncontrolled. Terminals in this zone are not tinned.

2. Both recesses are ∅ 2.5 × 0.8 max. depth

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

SOT186A TO-220 97-06-11

Fig.16. SOT186A; The seating plane is electrically isolated from all terminals.

Notes

1. Observe the general handling precautions for electrostatic-discharge sensitive devices (ESDs) to prevent

damage to MOS gate oxide.

2. Refer to mounting instructions for F-pack envelopes.

3. Epoxy meets UL94 V0 at 1/8".

November 2000 7 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

MECHANICAL DATA

Dimensions in mm Plastic single-ended package; isolated heatsink mounted;

1 mounting hole; 3 lead TO-220 exposed tabs SOT186

Net Mass: 2 g

E

E1 A

P m A1

D1

L1

Q

b1

L

L2

1 2 3

b w M c

e

e1

0 5 10 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT A A1 b b1 c D D1 E E1 e e1 L L1(1) L2 m P Q q w

mm 4.4 2.9 0.9 1.5 0.55 17.0 7.9 10.2 5.7 14.3 4.8 0.9 3.2 1.4 4.4

2.54 5.08 10 0.4

4.0 2.5 0.7 1.3 0.38 16.4 7.5 9.6 5.3 13.5 4.0 0.5 3.0 1.2 4.0

Note

1. Terminal dimensions within this zone are uncontrolled. Terminals in this zone are not tinned.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

SOT186 TO-220 97-06-11

Fig.17. SOT186; The seating plane is electrically isolated from all terminals.

Notes

1. Observe the general handling precautions for electrostatic-discharge sensitive devices (ESDs) to prevent

damage to MOS gate oxide.

2. Refer to mounting instructions for F-pack envelopes.

3. Epoxy meets UL94 V0 at 1/8".

November 2000 8 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor PHX9NQ20T , PHF9NQ20T

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 2000

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

November 2000 9 Rev 1.100

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

You might also like

- N-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataRobert sibueaNo ratings yet

- N-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataLenin Cadillo GutierrezNo ratings yet

- IRF540Document9 pagesIRF540paul mathewNo ratings yet

- Datasheet 6Document9 pagesDatasheet 6Ivanor Ipanaque CordovaNo ratings yet

- N-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataingucvNo ratings yet

- N-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataNixon MaldonadoNo ratings yet

- IRFZ24NDocument8 pagesIRFZ24NarcatusNo ratings yet

- Important Notice: Kind RegardsDocument8 pagesImportant Notice: Kind Regardscarlosjamal95No ratings yet

- BUK 9575 - Interruptor de PotênciaDocument8 pagesBUK 9575 - Interruptor de PotênciaTiago LeonhardtNo ratings yet

- Powermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataRio CandrapurwitaNo ratings yet

- Powermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataCarlos Morales AvilaNo ratings yet

- PDF Philips 26610Document11 pagesPDF Philips 26610ecsa tallerNo ratings yet

- HGP105N15SLDocument6 pagesHGP105N15SLمحمد الراويNo ratings yet

- Buk9635-100a 1Document7 pagesBuk9635-100a 1Raul OsoNo ratings yet

- Isc N-Channel MOSFET Transistor STD10NM60N: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor STD10NM60N: INCHANGE SemiconductorY. Leonel MolinaNo ratings yet

- Trenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference DataDocument8 pagesTrenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference DataNicki LarsonNo ratings yet

- N-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDaniel Orlando Carballo FernándezNo ratings yet

- CRST065N08N Datasheet - Moto ElétricaDocument10 pagesCRST065N08N Datasheet - Moto ElétricaDenis OliveiraNo ratings yet

- Transistor MosfetDocument2 pagesTransistor MosfetFlavin MedinaNo ratings yet

- 70L02GHDocument8 pages70L02GHJtzabalaNo ratings yet

- P75N02LDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP75N02LDG: N-Channel Enhancement Mode MOSFETAriel Rodrigo MuñozNo ratings yet

- Enhancement Mode Power MOSFET: NCE N-ChannelDocument7 pagesEnhancement Mode Power MOSFET: NCE N-ChannelRichard MachadoNo ratings yet

- Isc N-Channel MOSFET Transistor HRF3205: FeaturesDocument2 pagesIsc N-Channel MOSFET Transistor HRF3205: FeaturesAnjitNo ratings yet

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaNo ratings yet

- Mosfet (70t03gh)Document4 pagesMosfet (70t03gh)Allan Souza SantanaNo ratings yet

- Powermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/BDocument7 pagesPowermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/Bmaykel valdezNo ratings yet

- Powermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedDocument9 pagesPowermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedEmmanuel ZambranoNo ratings yet

- Irfz44n PDFDocument2 pagesIrfz44n PDFDenilson Gonzales VilchezNo ratings yet

- Advanced Power Electronics Corp.: AP70T03GH/JDocument4 pagesAdvanced Power Electronics Corp.: AP70T03GH/JVolodiyaNo ratings yet

- 70T03GH AdvancedPowerElectronics PDFDocument4 pages70T03GH AdvancedPowerElectronics PDFAdriano Neoaver TavaresNo ratings yet

- Advanced Power Electronics Corp.: AP70T03GH/JDocument4 pagesAdvanced Power Electronics Corp.: AP70T03GH/JkikinNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionzakreaNo ratings yet

- IRF840 AdvancedPowerElectronicsDocument4 pagesIRF840 AdvancedPowerElectronicssheikh sheharyarNo ratings yet

- phn210 Doble MosfetDocument7 pagesphn210 Doble Mosfetmarino246No ratings yet

- Isc N-Channel MOSFET Transistor SPP17N80C3 ISPP17N80C3: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor SPP17N80C3 ISPP17N80C3: INCHANGE SemiconductorMiguel CorderoNo ratings yet

- 9T16GH MOSFET CANAL N SMDDocument4 pages9T16GH MOSFET CANAL N SMDVictorManuelBernalBlancoNo ratings yet

- CRJQ190N65GCFDocument9 pagesCRJQ190N65GCFVadim PopovichNo ratings yet

- Advanced Power Electronics Corp.: AP18T10AGH/J-HFDocument4 pagesAdvanced Power Electronics Corp.: AP18T10AGH/J-HFAlejadro FierroNo ratings yet

- SSM40N03P: DescriptionDocument6 pagesSSM40N03P: DescriptionspotNo ratings yet

- STD38NH02L: N-CHANNEL 24V - 0.011 - 38A Dpak/Ipak Stripfet™ Iii Power MosfetDocument13 pagesSTD38NH02L: N-CHANNEL 24V - 0.011 - 38A Dpak/Ipak Stripfet™ Iii Power MosfetJose luisNo ratings yet

- 10n65a 10n65afDocument6 pages10n65a 10n65afYeo LeoNo ratings yet

- Isc N-Channel MOSFET Transistor 2SK3505: FeaturesDocument2 pagesIsc N-Channel MOSFET Transistor 2SK3505: FeaturesFale MensNo ratings yet

- Hgp045ne4sl - V1.0 DS-101416Document6 pagesHgp045ne4sl - V1.0 DS-101416selandrinoNo ratings yet

- Advanced Power Electronics Corp.: AP15N03GH-HFDocument7 pagesAdvanced Power Electronics Corp.: AP15N03GH-HFEhsan MohammadiNo ratings yet

- Advanced Power Electronics Corp.: AP9870GH-HFDocument7 pagesAdvanced Power Electronics Corp.: AP9870GH-HFAlejandro MarceloNo ratings yet

- skst065n08n skss063n08nDocument10 pagesskst065n08n skss063n08nStefan IuscoNo ratings yet

- AP 40T03GP - Advandced Power Electronic CorpDocument4 pagesAP 40T03GP - Advandced Power Electronic CorpStevenNo ratings yet

- AP9972GSPDocument6 pagesAP9972GSPSantiago DiosdadoNo ratings yet

- Advanced Power Electronics Corp.: AP0403GHDocument5 pagesAdvanced Power Electronics Corp.: AP0403GHIulius CezarNo ratings yet

- Irf 540Document8 pagesIrf 540Tom TweedleNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Description: Standard 0.8 A TriacsDocument8 pagesDescription: Standard 0.8 A TriacsreparacionesdmaNo ratings yet

- BTB08-600BW3G, BTB08-800BW3G Triacs: Silicon Bidirectional ThyristorsDocument6 pagesBTB08-600BW3G, BTB08-800BW3G Triacs: Silicon Bidirectional ThyristorsreparacionesdmaNo ratings yet

- Features General Description Features General Description: 20V N-Channel MOSFETDocument5 pagesFeatures General Description Features General Description: 20V N-Channel MOSFETreparacionesdmaNo ratings yet

- Product Summary:, 80A FeaturesDocument1 pageProduct Summary:, 80A FeaturesreparacionesdmaNo ratings yet

- Service Manual: LCD Colour Television LC-32WD1E/S/RU LC-37WD1E/S/RU LC-42WD1E/S/RU LC-32WT1E LC-37WT1E Models Lc-42Wt1EDocument202 pagesService Manual: LCD Colour Television LC-32WD1E/S/RU LC-37WD1E/S/RU LC-42WD1E/S/RU LC-32WT1E LC-37WT1E Models Lc-42Wt1EreparacionesdmaNo ratings yet

- William Stallings Computer Organization and Architecture 10 EditionDocument38 pagesWilliam Stallings Computer Organization and Architecture 10 EditionSomya AgrawalNo ratings yet

- Catálogo VDODocument11 pagesCatálogo VDOalex aedoNo ratings yet

- Control Products CatalogDocument50 pagesControl Products Catalogmk saravananNo ratings yet

- HSSN AssignmentDocument23 pagesHSSN AssignmentChungMing LingNo ratings yet

- Galaxy Owners Manual dx55vDocument10 pagesGalaxy Owners Manual dx55vbellscb100% (1)

- Carlo - Gavazzi G34405543230 Datasheet Transceiver For Digital SignalsDocument3 pagesCarlo - Gavazzi G34405543230 Datasheet Transceiver For Digital SignalsGoran MladenovicNo ratings yet

- 110004774-10 170KV 630dia 1T With CK BaseDocument5 pages110004774-10 170KV 630dia 1T With CK Basetragi oyeNo ratings yet

- MIL-HDBK-1012 - 1 Electronic Facilities EngineeringDocument127 pagesMIL-HDBK-1012 - 1 Electronic Facilities EngineeringnayalalonNo ratings yet

- Signal Sampling: - Sampling Is Converting A Signal Into A Signal - CategoriesDocument57 pagesSignal Sampling: - Sampling Is Converting A Signal Into A Signal - Categoriesimranchaudhry12No ratings yet

- Hybrid Universal Analog Digital Voltage Regulator Operation ManualDocument6 pagesHybrid Universal Analog Digital Voltage Regulator Operation ManualJose MarcialNo ratings yet

- Design and Implementation of An Rfid Based Automated Students Attendance System R BasasDocument6 pagesDesign and Implementation of An Rfid Based Automated Students Attendance System R BasasCielle negreteNo ratings yet

- Vlsi LP& SyllabusDocument2 pagesVlsi LP& SyllabusanittadevadasNo ratings yet

- Liebert: Exm Ups 10-250 kVA/kW Efficient, Scalable, Intelligent Power Optimized For Midsize ITDocument8 pagesLiebert: Exm Ups 10-250 kVA/kW Efficient, Scalable, Intelligent Power Optimized For Midsize ITEmmanuel RenteriaNo ratings yet

- Line Follower Robot ProjectDocument45 pagesLine Follower Robot ProjectJeffery YipNo ratings yet

- CC848836981 Pulsar Edge Product Manual r04 PDFDocument184 pagesCC848836981 Pulsar Edge Product Manual r04 PDFDiogo Faria LimaNo ratings yet

- TENCON2016Document6 pagesTENCON2016Nagaraj NeradhalaNo ratings yet

- PLC ManualDocument69 pagesPLC ManualMohamed SaleemNo ratings yet

- RFX Wireless Interface System Manual: Document 51012 06/26/2003 RevDocument44 pagesRFX Wireless Interface System Manual: Document 51012 06/26/2003 Revjohn castilloNo ratings yet

- EE Times - Addressing Signal Electromigration (EM) in Today's Complex Digital DesignsDocument9 pagesEE Times - Addressing Signal Electromigration (EM) in Today's Complex Digital DesignsferrariNo ratings yet

- Display TechnologiesDocument8 pagesDisplay TechnologiesAshley MainaNo ratings yet

- Resume Murugan ParamasivamDocument5 pagesResume Murugan ParamasivamPower MuruganNo ratings yet

- EE6501 Power System AnalysisDocument161 pagesEE6501 Power System AnalysisMahendiran CrNo ratings yet

- Vdocuments - MX - Mimaki cg130 FX Service ManualDocument142 pagesVdocuments - MX - Mimaki cg130 FX Service ManualCarlos PaezNo ratings yet

- CH 29Document22 pagesCH 29Qassem MohaidatNo ratings yet

- Lesson Plan DPSDDocument5 pagesLesson Plan DPSD1627sakthiNo ratings yet

- MCCB & AcbDocument42 pagesMCCB & AcbSandeep MenonNo ratings yet

- Sylvania Lc370ss9 LCD TV SMDocument61 pagesSylvania Lc370ss9 LCD TV SMstechs02100% (1)

- Octansiii Ug Part 2 Octans Surface Ug Mu-octiii-003-ADocument32 pagesOctansiii Ug Part 2 Octans Surface Ug Mu-octiii-003-ApankajNo ratings yet

- CSR8675 Bluetooth Audio Platform: QualcommDocument2 pagesCSR8675 Bluetooth Audio Platform: QualcommJames ChoongNo ratings yet

- FALLSEM2012-13 CP0991 03-Aug-2012 RM01Document4 pagesFALLSEM2012-13 CP0991 03-Aug-2012 RM01Ankit BhattNo ratings yet