Professional Documents

Culture Documents

3 Mosfet

Uploaded by

Alexis Utha0 ratings0% found this document useful (0 votes)

11 views36 pagesSmita Bhagwat will present on the topic of field-effect transistors and power devices. The presentation will cover the difference between BJT and FET transistors, the construction and operation of enhancement-mode MOSFETs, biasing techniques including the common-source amplifier, and an overview of power devices like SCRs and TRIACs. The presentation is intended for a basic electronics engineering course at Vishwakarma Institute of Information Technology, where Smita Bhagwat is an assistant professor in the electronics and telecommunication engineering department.

Original Description:

Original Title

3_MOSFET

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentSmita Bhagwat will present on the topic of field-effect transistors and power devices. The presentation will cover the difference between BJT and FET transistors, the construction and operation of enhancement-mode MOSFETs, biasing techniques including the common-source amplifier, and an overview of power devices like SCRs and TRIACs. The presentation is intended for a basic electronics engineering course at Vishwakarma Institute of Information Technology, where Smita Bhagwat is an assistant professor in the electronics and telecommunication engineering department.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

11 views36 pages3 Mosfet

Uploaded by

Alexis UthaSmita Bhagwat will present on the topic of field-effect transistors and power devices. The presentation will cover the difference between BJT and FET transistors, the construction and operation of enhancement-mode MOSFETs, biasing techniques including the common-source amplifier, and an overview of power devices like SCRs and TRIACs. The presentation is intended for a basic electronics engineering course at Vishwakarma Institute of Information Technology, where Smita Bhagwat is an assistant professor in the electronics and telecommunication engineering department.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 36

Presentation Topic

Name of the course :- Basic Electronics Engineering

Faculty Name:- Smita Bhagwat- Bannapure

Faculty official (VIIT) mail Id:- smita.bhagwat@viit.ac.in

Department of E&TC Engineering

BRACT’S, Vishwakarma Institute of Information Technology, Pune-48

(An Autonomous Institute affiliated to Savitribai Phule Pune University)

(NBA and NAAC accredited, ISO 9001:2015 certified)

Unit – 03:Field-Effect Transistor

(MOSFET) & Power Devices

Mrs. Smita Bhagwat Bannapure

Assistant Professor

Department of E&TC

VIIT, Pune-411048

Smita Bhagwat E&TC dept., VIIT, Pune 48 2

Acknowledgement

▪ All figures and text in this presentation are

taken from book “Electronic Devices –

Conventional Current Version,” 9th Ed., by

Thomas L. Floyd.

Smita Bhagwat E&TC dept., VIIT, Pune 48 3

Outline

▪ Difference between BJT and FET

▪ E-MOSFET

▪ Construction,

▪ Working

▪ Characteristics

▪ Biasing techniques and CS Amplifier

▪ Power Devices- SCR and TRIAC

▪ Construction,

▪ Working

▪ Characteristics

▪ Application

Smita Bhagwat E&TC dept., VIIT, Pune 48 4

Difference Between BJT and FET

▪ BJT: Bipolar and FET: Unipolar

▪ BJT: Current controlled, FET: Voltage Controlled

▪ FETs are more temperature stable than BJT

▪ Size of FET is smaller than BJT

▪ High Input impedance and offer low gain

Smita Bhagwat E&TC dept., VIIT, Pune 48 5

Field Effect Transistor (FET):

Introduction

▪ Types of FETs :

Junction field-effect transistor (JFET)

metal-oxide-semiconductor field-effect transistor (MOSFET).

▪ Types of MOSFET:

depletion D-MOSFET

enhancement E-MOSFET

▪ In FET: An electric field control the conduction path of the output

current

▪ The MOSFETs are popular in the design and construction of

integrated circuits (ICs) for digital computers.

▪ Its thermal stability and low power dissipation makes it extremely

popular in computer circuit design and in VLSI technology

Smita Bhagwat E&TC dept., VIIT, Pune 48 6

EMOS-FET (Metal Oxide Semiconductor Field

Effect Transistor) : Construction

N-channel Enhancement-

• A slab of p-type silicon MOSFET

substrate and two n-type

regions forming the source

and drain terminals are

connected through

metallic contacts to n-

doped regions,

• The channel is absent

between the two n-doped

regions.

• The SiO2 layer is present

to isolate the gate metallic

platform from the region

between the drain and

source Smita Bhagwat E&TC dept., VIIT, Pune 48 7

E-MOSFET: Symbols and Water Analogy

Smita Bhagwat E&TC dept., VIIT, Pune 48 8

Operation and Characteristics

• N-channel EMOSFET

• With VDS at +ve voltage,

• VGS at 0 V,

• SS connected to the source,

• There are two reverse-

biased p-n junctions

between the n-doped

regions and the p-substrate

to oppose the IDS

• The absence of an n-

channel will result in a zero

current.

Smita Bhagwat E&TC dept., VIIT, Pune 48 9

Channel Formation in E-MOSFET

• VDS and VGS are positive

voltage greater than 0 V,

establishing the drain and gate

at a positive potential with

respect to the source.

• The positive potential at the

gate will pressure the holes

(since like charges repel) in the

p-substrate along the edge of

the SiO2 layer to leave the area

and enter deeper regions of the

p-substrate.

• However, the electrons in the p-

substrate will be attracted to

the positive gate and

accumulate near the SiO2 layer.

Smita Bhagwat E&TC dept., VIIT, Pune 48 10

▪ The insulating property of SiO2 layer will prevent the

electrons from being absorbed at the gate terminal.

▪ As VGS increases, the concentration of electrons near the

SiO2 surface increases until the induced n-type region can

support a measurable flow between drain and source.

▪ The level of VGS that results in the significant increase in

drain current is called the threshold voltage (VT).

▪ Since the channel is nonexistent with VGS 0 V and

“enhanced” by the application of a positive gate-to-source

voltage, this type of MOSFET is called an enhancement-type

MOSFET.

Smita Bhagwat E&TC dept., VIIT, Pune 48 11

Recap

▪ Difference between BJT and FET

▪ Introduction to FET and its types

▪ Construction of E-MOSFET

▪ Working of E-MOSFET

Smita Bhagwat E&TC dept., VIIT, Pune 48 12

Points to be covered

▪ Pinch-off process

▪ Transfer characteristics

▪ Drain Characteristics

▪ P-channel E-MOSFET

▪ Configurations (CS, CG, CD)

Smita Bhagwat E&TC dept., VIIT, Pune 48 13

Fig. Pinch-Off Process VGS >VT and

VDS> VDS(sat)

• The density of free carriers in the

induced channel will increase, which

increases drain current.

• However, if VGS =constant and

increase the level of

VDS> (VGS-VGSTh), the drain current

will eventually reach a saturation

level

• The leveling off of ID is due to a

pinching-off process depicted by the

narrower channel at the drain end of

the induced channel as shown in Fig.

Smita Bhagwat E&TC dept., VIIT, Pune 48 14

▪ As V DS> (VGS-VT) , Voltage VDG increases.

▪ The gate will become less and less positive with

respect to the drain.

▪ This reduction in Gate voltage reduces the

attractive forces for free carriers (electrons) in

this region of the induced channel, causing a

reduction in the effective channel width.

▪ Eventually, the channel will be reduced to the

point of pinch-off and a saturation condition will

be established

▪ In other words, any further increase in VDS at the

fixed value of VGS will not affect the saturation

level of ID until breakdown conditions are

encountered.

Smita Bhagwat E&TC dept., VIIT, Pune 48 15

Transfer Characteristics

Smita Bhagwat E&TC dept., VIIT, Pune 48 16

Calculation of parameter k

Smita Bhagwat E&TC dept., VIIT, Pune 48 17

Calculation of transconductance

parameter k

▪ W=width of substrate, L=length of substrate

▪ Mu= mobility of charge carriers

▪ Cox=Capacitance of oxide layer

Smita Bhagwat E&TC dept., VIIT, Pune 48 18

Drain Characteristics

Smita Bhagwat E&TC dept., VIIT, Pune 48 19

Drain Characteristics

▪ For a fixed value of VT, and the higher the level of

VGS, the saturation level for VDS is also more, as

shown by the locus of saturation levels.

▪ In fact, the saturation level for VDS is related to the

level of applied VGS by applying Kirchhoff’s voltage

law to the terminal voltages of the MOSFET.

Smita Bhagwat E&TC dept., VIIT, Pune 48 20

For VGS < VT, ID=0mA

▪ The spacing between the levels of VGS increased as the

magnitude of VGS increased, resulting in ever-increasing

increments in drain current.

▪ The squared term results in the nonlinear (curved)

relationship between ID and VGS.

▪ The k term is a constant that is a function of the construction

of the device.

▪ The value of k can be determined from the following equation

where ID(on) and VGS(on) are the values for each at a

particular point on the characteristics of the device.

Smita Bhagwat E&TC dept., VIIT, Pune 48 21

Calculation of k from datasheet values

(Example)

VT= 2V, ID(on)=10mA, VGS(on)=8V, VGS=4V

Smita Bhagwat E&TC dept., VIIT, Pune 48 22

p-Channel Enhancement-Type

MOSFETs

Smita Bhagwat E&TC dept., VIIT, Pune 48 23

▪ Example 2

▪ Solution

Smita Bhagwat E&TC dept., VIIT, Pune 48 24

MOSFET amplifier configurations

Smita Bhagwat E&TC dept., VIIT, Pune 48 25

Comparison

Smita Bhagwat E&TC dept., VIIT, Pune 48 26

Summary

▪ Common-Source (CS) configuration

– best suited for the bulk of gain

▪ Common-Source (CS) configuration with Rs in the source

– improved performance but reduced gain

▪ Common-Gate (CG) configuration

– low input resistance

– excellent high-frequency performance

– unity-gain current amplifier

– cascode amplifier

▪ Common-Drain (CD) or Source follower

– voltage buffer for connecting a high-resistance source to

– a low –resistance load

– output stage in a multi-stage amplifier

Smita Bhagwat E&TC dept., VIIT, Pune 48 27

▪ Biasing Technique

▪ Voltage Divider Bias

– E-MOSFETs must have a VGS >VGS(th),

Smita Bhagwat E&TC dept., VIIT, Pune 48 28

Example 2:

Smita Bhagwat E&TC dept., VIIT, Pune 48 29

Smita Bhagwat E&TC dept., VIIT, Pune 48 30

Example 3:

Smita Bhagwat E&TC dept., VIIT, Pune 48 31

Example 4:

Smita Bhagwat E&TC dept., VIIT, Pune 48 32

Smita Bhagwat E&TC dept., VIIT, Pune 48 33

Smita Bhagwat E&TC dept., VIIT, Pune 48 34

E-MOSFET CS AMPLIFIER

▪ A common-source n-channel E-MOSFET with

voltage-divider bias with an ac source

capacitive coupled to the gate.

▪ The gate is biased with a

positive voltage such

that VGS > VGS(th).

Smita Bhagwat E&TC dept., VIIT, Pune 48 35

▪ The signal voltage produces a swing in Vgs

above and below its Q-point value, VGSQ.

▪ This, in turn, causes a swing in Id above and

below its Q-point value, IDQ, as illustrated

in Figure.

▪ Operation is entirely in the enhancement

mode.

Smita Bhagwat E&TC dept., VIIT, Pune 48 36

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Presentation Topic: Name of The CourseDocument36 pagesPresentation Topic: Name of The CourseAlexis UthaNo ratings yet

- ElectronicsDocument22 pagesElectronicsVARSHITH REDDY JNo ratings yet

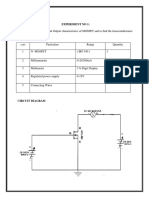

- 1 To 5 ManualDocument30 pages1 To 5 ManualRoshan DodiyaNo ratings yet

- Mosfet CharacteristicsDocument10 pagesMosfet CharacteristicsAnonymous eWMnRr70qNo ratings yet

- Special Class 6 April 2020Document25 pagesSpecial Class 6 April 2020sivaenotesNo ratings yet

- ECE221 MOSFETs-I SRMAP PDFDocument30 pagesECE221 MOSFETs-I SRMAP PDFRajeshNo ratings yet

- Electronic Devices & Circuits: Khurram Bughio Lecturer Electrical Engineering, MUETDocument29 pagesElectronic Devices & Circuits: Khurram Bughio Lecturer Electrical Engineering, MUETNoor SabaNo ratings yet

- Mosfet 1Document27 pagesMosfet 1Jadhav BhagavatNo ratings yet

- EE305Document19 pagesEE305api-3853441No ratings yet

- Hyuga SimulationDocument8 pagesHyuga SimulationJimmy MachariaNo ratings yet

- 05961633Document9 pages05961633dabalejoNo ratings yet

- Final MosfetDocument33 pagesFinal MosfetabdallaNo ratings yet

- DCID Experiment MergedDocument94 pagesDCID Experiment MergedSumer SainiNo ratings yet

- Analog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Document16 pagesAnalog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Udai SinghNo ratings yet

- MOSFET biasing-FinalDocument29 pagesMOSFET biasing-FinalsathviksolletiNo ratings yet

- Expt 13 - JFET-CharaceristicsDocument8 pagesExpt 13 - JFET-CharaceristicssamarthNo ratings yet

- Bel 06 Field Effect TransistorDocument17 pagesBel 06 Field Effect TransistorBharavi K SNo ratings yet

- FET and IGBT DevicesDocument22 pagesFET and IGBT DevicesShafaq EjazNo ratings yet

- Electronic Devices & Circuits (EDC) PE-124: Prepared By: Engr. Shafaq EjazDocument22 pagesElectronic Devices & Circuits (EDC) PE-124: Prepared By: Engr. Shafaq EjazShafaq EjazNo ratings yet

- Pe 1Document92 pagesPe 1niteshNo ratings yet

- Igbt Notes 2Document22 pagesIgbt Notes 2gomathyNo ratings yet

- Mosfet CharacteristicsDocument10 pagesMosfet CharacteristicsAnonymous eWMnRr70qNo ratings yet

- Tutorials Analog 2Document5 pagesTutorials Analog 2fatihah hashimNo ratings yet

- Det115 - Electronic Devices: Field-Effect Transistor (Fet) - MosfetDocument27 pagesDet115 - Electronic Devices: Field-Effect Transistor (Fet) - Mosfetksreddy2002No ratings yet

- ch6 2Document31 pagesch6 2avishek aviNo ratings yet

- FETDocument91 pagesFETpawan_32No ratings yet

- Unit1 Mosfet RevDocument36 pagesUnit1 Mosfet RevMohak KumarNo ratings yet

- Module 2Document51 pagesModule 2eswarsenthil2004No ratings yet

- Application Note en 20180726 PDFDocument22 pagesApplication Note en 20180726 PDFĐỗ Văn ThủyNo ratings yet

- Jfet, D-Mosfet, E-Mosfet, Vmos, CmosDocument47 pagesJfet, D-Mosfet, E-Mosfet, Vmos, CmosDAVU REVANTH NAGNo ratings yet

- Analysis On IGBT DevelopmentsDocument6 pagesAnalysis On IGBT DevelopmentsGopal Chandra MahatoNo ratings yet

- MOS IC Technology GuideDocument45 pagesMOS IC Technology GuidemojnkuNo ratings yet

- 3-2power Electronics Lab ManualDocument50 pages3-2power Electronics Lab ManualSivareddy MudiyalaNo ratings yet

- MOSFET TransistorDocument17 pagesMOSFET TransistorOmer BallakNo ratings yet

- FET Charcateristics (CS Configuration)Document6 pagesFET Charcateristics (CS Configuration)Bhanu KodaliNo ratings yet

- Experiment No 3a MOSFET CharacteristicsDocument5 pagesExperiment No 3a MOSFET CharacteristicsManikandan P Engineering EEE100% (1)

- MOSFET Module5Document16 pagesMOSFET Module5Rahul sandireddyNo ratings yet

- De 19cse33Document102 pagesDe 19cse33Raghav ReddyNo ratings yet

- B.E. FETs and Other Components NotesDocument12 pagesB.E. FETs and Other Components NotesLaxman SalianNo ratings yet

- 3 Power MosfetDocument23 pages3 Power MosfetSayan DasNo ratings yet

- BJTs Small SignalsDocument17 pagesBJTs Small SignalsBokang MaphatheNo ratings yet

- Center For Advanced Studies in Engineering, Islamabad Electronics LabDocument9 pagesCenter For Advanced Studies in Engineering, Islamabad Electronics LabHussain HadiNo ratings yet

- MOS Theory, SPICE, CMOS Fabrication LectureDocument70 pagesMOS Theory, SPICE, CMOS Fabrication LecturePrayat Anil HegdeNo ratings yet

- Lecture 8Document35 pagesLecture 8Suja GanesanNo ratings yet

- FET/MOSFET Characteristics: ObjectiveDocument13 pagesFET/MOSFET Characteristics: ObjectiveZeeshan RafiqNo ratings yet

- Unit 2Document69 pagesUnit 2KISHAN SHUKLANo ratings yet

- Expt - 11: JFET CharacteristicsDocument8 pagesExpt - 11: JFET CharacteristicssamarthNo ratings yet

- AEC Lab ManualDocument75 pagesAEC Lab Manualphalanetra100% (1)

- Field Effect Transistor: UNIT-4Document70 pagesField Effect Transistor: UNIT-4I am FineNo ratings yet

- Course: Electronic Circuit Design Lab No: 08 Title: Characterization of The MOS Transistor CID: - DateDocument6 pagesCourse: Electronic Circuit Design Lab No: 08 Title: Characterization of The MOS Transistor CID: - DateAamir ChohanNo ratings yet

- cta.3136Document12 pagescta.3136Liana DimaNo ratings yet

- Unit 1.1 Introduction To Analog ElectronicsDocument10 pagesUnit 1.1 Introduction To Analog ElectronicschettiyathNo ratings yet

- MosfetDocument32 pagesMosfetMayank AgarwalNo ratings yet

- Department of Technical Education Andhra Pradesh: EC302.37 TO 38 1Document22 pagesDepartment of Technical Education Andhra Pradesh: EC302.37 TO 38 1parrotpanduNo ratings yet

- JFETs and MOSFETSDocument17 pagesJFETs and MOSFETSBokang MaphatheNo ratings yet

- Mosfets BasicsDocument7 pagesMosfets Basicsodl_123No ratings yet

- Characteristics of BJTs and MOSFETs (39Document10 pagesCharacteristics of BJTs and MOSFETs (39Umar AkhtarNo ratings yet

- Mos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorDocument14 pagesMos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorKumar Amit VermaNo ratings yet

- Notes-Unit 3 - Instrumental Methods of AnalysisDocument40 pagesNotes-Unit 3 - Instrumental Methods of AnalysisAlexis UthaNo ratings yet

- Notes-Unit 2 - Chemistry of Engineering Materials (2020)Document61 pagesNotes-Unit 2 - Chemistry of Engineering Materials (2020)Alexis UthaNo ratings yet

- Notes - Unit 1 - Water Technology (2020)Document28 pagesNotes - Unit 1 - Water Technology (2020)Rakesh SawaiNo ratings yet

- DSA Sample Oral QuestionsDocument1 pageDSA Sample Oral QuestionsAlexis UthaNo ratings yet

- Hydraulic Accumulator Presentation PDFDocument18 pagesHydraulic Accumulator Presentation PDFHanna Najm100% (1)

- Lab 09 - Power SuppliesDocument47 pagesLab 09 - Power SuppliescrackintheshatNo ratings yet

- BEE3133 Electrical Power Systems: Transmission Line ParametersDocument84 pagesBEE3133 Electrical Power Systems: Transmission Line ParametersLittle CandyNo ratings yet

- MAX485 module titleDocument2 pagesMAX485 module titleBubai BhattacharyyaNo ratings yet

- Transducers: An IntroductionDocument61 pagesTransducers: An IntroductionHari Narayanan ACNo ratings yet

- Virtualization Guide - SUSE Linux Enterprise Server 12 SP2Document366 pagesVirtualization Guide - SUSE Linux Enterprise Server 12 SP2juniorexNo ratings yet

- Instructions: Electronic Unit For BD35F/50F/35K Compressors, 101N0212, 101N0340 and 101N0650, 12/24V DCDocument2 pagesInstructions: Electronic Unit For BD35F/50F/35K Compressors, 101N0212, 101N0340 and 101N0650, 12/24V DCDong NguyenNo ratings yet

- Navtex System - User & Installation ManualDocument51 pagesNavtex System - User & Installation ManualEster Angel NdrahaNo ratings yet

- XFBDocument2 pagesXFBMikeCao1384No ratings yet

- LP100A Assembly ManualDocument50 pagesLP100A Assembly ManualGopakumar KNo ratings yet

- LG HRX550 User ManualDocument106 pagesLG HRX550 User ManualpaulkupasNo ratings yet

- Owner's Manual: Integrated High Definition LCD TelevisionDocument62 pagesOwner's Manual: Integrated High Definition LCD TelevisionManuel MartinezNo ratings yet

- 40 Seaters Phonetic Speech LaboratoryDocument11 pages40 Seaters Phonetic Speech LaboratoryBernardo BasmayorNo ratings yet

- Lab 3 - Gas Sensor (Iman, Faiz, Anas)Document10 pagesLab 3 - Gas Sensor (Iman, Faiz, Anas)ahmad faizNo ratings yet

- RH Pacemaker Sap Whitepaper PDFDocument45 pagesRH Pacemaker Sap Whitepaper PDFSamNo ratings yet

- Light ProjectDocument17 pagesLight Projectapi-310899958No ratings yet

- Timer Programing of Atmega32Document8 pagesTimer Programing of Atmega32Stephanie Flores100% (1)

- Eng 306 - Doc 3 - 2020f - Extra ReadingDocument163 pagesEng 306 - Doc 3 - 2020f - Extra ReadingNguyen Anh TaiNo ratings yet

- 4906-9131 WP MC Av Non-Addr Wall MT RedDocument4 pages4906-9131 WP MC Av Non-Addr Wall MT Redjulian.florez.saNo ratings yet

- Annual Procrement PLanDocument42 pagesAnnual Procrement PLanMhelody Gutierrez BelmonteNo ratings yet

- Counterfeit Integrated CircuitsDocument15 pagesCounterfeit Integrated CircuitsPudi PudaNo ratings yet

- Helicopter Landing Gear SystemsDocument48 pagesHelicopter Landing Gear SystemsKarthik Bk100% (1)

- Business Moel of Oppo and XaiomiDocument5 pagesBusiness Moel of Oppo and XaiomiManveer SinghNo ratings yet

- DS1300-3 Series PDFDocument4 pagesDS1300-3 Series PDFdoraemon007No ratings yet

- TransformersDocument20 pagesTransformersgeltinNo ratings yet

- Cblm-Electric FanDocument48 pagesCblm-Electric FanLeon AtsilegnaveNo ratings yet

- 150kV GIS and Underground Cable Installation ServicesDocument7 pages150kV GIS and Underground Cable Installation ServicesReinhard Jesaya SimbolonNo ratings yet

- 515 AI01 AP Additive ControllerDocument4 pages515 AI01 AP Additive ControllerJose HuescaNo ratings yet

- FE800 Operator's ManualDocument52 pagesFE800 Operator's ManualZaw Khaing WinNo ratings yet

- RF Engineer ResumeDocument3 pagesRF Engineer ResumemadhubaddapuriNo ratings yet