Professional Documents

Culture Documents

Feedback Compensation Design For Switched Mode Power Supplies

Feedback Compensation Design For Switched Mode Power Supplies

Uploaded by

shrikris0 ratings0% found this document useful (0 votes)

14 views6 pagesOriginal Title

Feedback compensation design for switched mode power supplies

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

14 views6 pagesFeedback Compensation Design For Switched Mode Power Supplies

Feedback Compensation Design For Switched Mode Power Supplies

Uploaded by

shrikrisCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 6

238

FEEDBACK COMPENSATION DESIGN FOR SWITCHED MODE

POWER SUPPLIES WITH A RIGHT-HALF-PLANE (RHP) ZERO

K. Kittipeerachon, C. Bunlaksananusorn

Keywords: Feedback compensation design, Right-Half-Plane

(RHP) 2270, Switched Mode Power Supplies (SMPS)

Abstract

‘A boost and flyback converters opersting in Continuons

Conduction Mode (CCM) are notorious for their dificult

control loop stbilisation and slugaish response. This paper

describes Feedback compensation design ofthese converters.

Design of the two selected compensation circuits is illustrated

with a CCM boost converter, with experimental results given

to verity effectiveness of each compensation circuit

1_ Introduction

Switched Mode Power Supplies (SMPS) have become a

Standard power source for modem electronic equipment due

to their compactness and high effcieney. The SMPS maint

an output voltae to be within a prescribed limit throughout

their operating conditions, by means of feedback contol

Invariably, the SMPS feecback control is designed with the

objectives that the output voltage must be stable and well

regulated, and responds sensibly fast to disturbances such as a

sudden change in load euzent. Thote targets ean be schioved

by appropriate design of a compensation circuit in the

feednack lop.

SMPS feedback compensetion circuit design method is

Geseribed in [1], Performed in the frequency domain and

aided by Bode plots, the design essentlly involves

positioning of poles and zeros of the selected compensation

ircuit fo compensate the undesirable characteristics of a

power stage. The desired result is an open loop transfer

function that has high gain and reasonably high bandwith,

and that does not violate Nyquist’s stebilty criterion. Due co

its graphical nature and simplicity, this design method has

been widely adopted in practial compensation circuit design

[2.31 For a buck converter and ils derivative (e.g. forward

converter, half-bridge converter, etc), the feedback

compensation circuit can be designed to give the converter a

wide system bandwidth and thus a fast output voliage

response, while an adequate phase margin for stability is

‘maintained. The bandwidth of up toa quarter of a switching

Frequency is typical for this clas of converters. However, for

converters whose trnsfer functions include « Righ-llalf-

Plane (RHP) zero [4], such asa boost and flyback converters

‘operating in Continuous Conduetion Mode (CCM), an

200k KMAIT Tha

culty of Engineering, Ring Mongkut’

Bangkok 10520, Thailand, Fax: 662-326-4225, F-nail

g Institute of Technology Ladkcabang,

kbcnanin@kmitl.ac.th

additional 90° phase lag introduced by the RHP zero makes

the feedback loop more difficult to stabilise than their buck

counterparts. The bandwidth of thess converters is usually

limited to be below the frequency at which the RHP 2cr0

‘occurs to ensure stable operation of the converters. In the

realm of control engineering, # system with a RHP zcro is

referred to a5 @ nos-minimum phase sysiom [5], which is

known for its delayed and. sluggish response. Feedback

‘compensation design in [3,6-8] deals withthe design of buck-

type converters. In this paper, feedback compensation of

'SMPS with a non-minimum. phase characteristic is presented.

2 Feedback compensation circuit design

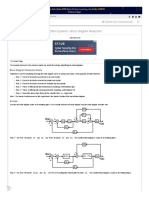

‘A conito block diagram of SMPS is shown in

“wg La | gym}

“| OE owen

Fig. 1A contol block diagram of SMPS

G,{s) nd G48) represent transfer functions of & power stage

(power circuit and PWM modulator combined) and a

‘feedback compensation circuit respectively. Vatiations of aa

input voltage, Vas), and output resistance, RAS), are the r¥0

‘major disturbances that cause an output voltage to be deviated

from the desited value, Vids). The SMPS feedback loop must

therefore be compensated to regulate the oupst voltage to be

‘within the limits allowed by the specification, when subjected

to these disturbances. Fo the diagram in figure 1, the transfer

forciion G(s) is predetermined from the chosen converter

topology, mode of operation (Continuous Conduction Mode,

CCM, er Discontinuoxs Conduction Mode, DCM), and

control method (voltage mode conbol or current mode

contol). Hence, feedback compensation design involves

selection ofa suitable compensation eireuit configuration and

Positioning of its poles and zeros t0 yield an open loop

transfer function, G,(s)G.C), the following desired frequency

‘characteristics

‘High gain at tow frequency region to provide tight output

voliage reguation|

A phase margin of at last 45° to ensure an adequate

stability margin

1nd Renrarticert with kind nermissinn

237

+A crossover frequency (or bandwidth), fof between one

tenh and one Tourth of a switehing fequency for a

system to respond sufficiently fst to disturbances

Feedback compensation to meet the shove requirements ean

be performed, without much difticulty, for # buck converter

and its derivative: However, forthe converters with a none

‘minimum phase characteristic, there cxists a trade-off

between the system bandwidth and sability in compensation

circuit design. Consider the transfer fanetion of a CCM boost

for flyback converters, which has a general form af

(si)

o

x,

(= KA

“GR a)

where , ©, and dgeqy are angular frequencies of an output

filter pole, ESR zero, and RHP zero respectively, and Q is a

quality factor. Asymptote Bode plots of equation (1) are

‘depicted in figure 2 forthe case where fui greter than f

Slopes of =I and 2 denote ~20dBdecade and ~404BVdecade

respectively

play

bel an

Fig. 2 Asymptote Bode plots of equation (1)

It can be seen that ¢ 90° phase lag contributed by the RHP

‘zero at fixye makes the phase of Gy(s) direct toward -180".

ius, in crapensaing Oy) ata afin ano of

phase margin requires that the crossover frequency, f, be

Seteced below faye The stunion wil be even one Hf the

RHP zor prvodesthe ESR zero, ie fae © f In ths case

the pace ng of Gy) aye wl open 270 and wl

he to be selec below the requncy of he ouput ker

poles

3 Compensation circuits

‘The compensation ciruit configuration is selected based oi

‘compensition strategies used. The most sixple strategy it (0

place a pole at low frequencies (required for improved output

‘voltage teulation) and rll off the open loop gain with f well

‘below f, of the power stage, where «sufficient phase margin

ig obtained. Despite ils” simplicity, chis compensation

technique is disodvaniageous in that the system bandwidth is

very limited and thus the output voltage response slugg’sh

Another compensation approach isto place poles and 220s to

compensate the undesirable characteristics of the power stage

This allows the system bandwidth to be extended to the

frequency close to figyr and considerable improvement in

‘output voltage response to be achioved, at the expense of

more design effor. required as compared with the first

approach, Though oiher compensation circuits may be used,

in this paper & single-pole and two-pole pve-zero

‘compensation circuits described below are seleted to realise

the former and later strategies respectively

3.1 Single-pote compensation circuit

‘A single-pole compentation circuit (figure 3(a) is expressed

by te transfer function

wre) @

zy

where K.-RyR and ay = 1/R,C). Asymptote Bode plots of

‘equation (2) are depicted in figure 3b). The circuit contains a

pole at fj, which is usually placed at low frequencies, a

requirement for good output voltage regulation. When used to

compensate a converter with a RHP zero, the crossover

frequency, f will be selected fo be at least $0% below f, in

figure 2 to avoid fy being tov close to f, that leads’ t0

deterioration of the phase margin, Feedback compensation

‘using the single-polecireit i iluseaed in section 4.1.

R

[6.48)| (eB)

oR

®

4

set

>

*

ob)

Fe 10) sek colts cnt) mete

238

3.2 Two-pole «wo-rero compensation circuit

A bwo-pole two-zero_ compensa

expressed by the transfer function

(Sea)

where KRY(Ry AR}, as = IARC, 2 = MRSC), Opt =

UiCa(RyRa)), and op = (RyFR,MRIRZC). Asymptote Bode

plots of equation (3) ere depicted in figure 4(b). Wren used to

‘compensate @ converter with a RHP zero, the first pole at fy

is placed at low frequencies, ¢ requirement for good ou:pit

voltage regulation, The two zeros al fy, and fy are placed at

frequencies near fy in Hgure 2 to nullify the effects oF the

‘output filter's double poles. The second pole at fy is placed at

frequencies near fin figure 2 to nullity the effects ofthe ESR.

zero. ‘The crossover frequency, f, will be selected t© not

exceed fxr in figure 210 avoid potential instability duc to an

accumulated phase lag of -180" caused by the pole at fy and

the RHP zero at fp, Feedback compensation using the t1o-

pole two-zero circuit is ilustrated in section 4.2.

cireuit (igure 4(@)) is

@

®

(6.00 60) ty eer

2G) (deseo)

4

° So lost

0

o

Fig. 4 (@) A eworpole two-20r0 compensation cireuit (si

asymptote Bode plots

4 Design Examples

Compensation cic

converter in figure S,

design i illustrated with a CCM boost

bee

Fig. 5 A CCM boost converer

‘The convertr's specifications are 9 follows: V, = 1OV, Vy =

15V, [y= IA to 3A, switching frequency (f) = 1OOKHZ. The

‘compensation circuit design is carried out for a maximum

load enrrent (R = 30). Te willbe later show thatthe resus

also valid when the load curent és minimum (R = 150),

‘Various unknowns of the boost converters transfer function

in equation (1) are determined as follows:

v (_s, 03) (toser0"

gate] Ae | a

wlacre, | anno soe!

~ Tite

ev VIC 2e41spgisn-10" K20010")

1

2eos7Co0«10")

arms

2aR,C

via wore

ail

ee 2x (as10")

yn’

wilevanonyes)

. 40ss¥ 6)

“rer (cover nono" 09) c@0))

‘An asympote magni plot of the boost power seis

dicted in figures 6(2) ard S(a). The estimated gains at fy,

and fu ate 12.4€B, -10.148, and 16.148 respectively

4.1 Design of single-pole compensation circuit

Asymplote magnitude plots, illustrating he single-pole

compensation circuit design, are shown in figure 6. AS sated

in section 3.1, the design of this.cxouit requites the crossover

frequency, f, be selected atleast 50% below f, of the power

stage. Here, fis chosen at 0.2f, or 1SOL2. AL f, G(s) is

found to have a gain of 12.44B; therefore the required gain of|

G.G) at this frequency is “12.4dB. The pole of Gs) at fy

rmust be placed at a frequency lower than f for the overall

system lo have high guin at low frequencies, Itis positioned at

0.04Hz and results in the low frequency gain of 60AB for

(6) and 72.40B for Gy()G(8), Having established the gain

frequency characteristic of G(s) eure G{b)), the

‘compensation circuit component values are ealeulated and

rounded off to the nearest standard values, obtaining Ry =

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5819)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 3 Phase Grid Connected PV Inverter PSIMDocument15 pages3 Phase Grid Connected PV Inverter PSIMshrikrisNo ratings yet

- CISPR15 2013 StandardDocument50 pagesCISPR15 2013 StandardshrikrisNo ratings yet

- Dynamic Analysis and Control Design of A Single-Phase UPS InverterDocument12 pagesDynamic Analysis and Control Design of A Single-Phase UPS InvertershrikrisNo ratings yet

- DSP-controlled Photovoltaic Inverter For Universal Application in Research and EducationDocument7 pagesDSP-controlled Photovoltaic Inverter For Universal Application in Research and EducationshrikrisNo ratings yet

- Light Load THD and Efficiency Optimization of Digitally Controlled PFC Converter With Integrated Valley Switching ControlDocument15 pagesLight Load THD and Efficiency Optimization of Digitally Controlled PFC Converter With Integrated Valley Switching ControlshrikrisNo ratings yet

- Control For Grid-Connected and Stand-Alone Operations of Three-Phase Grid-Connected InverterDocument5 pagesControl For Grid-Connected and Stand-Alone Operations of Three-Phase Grid-Connected InvertershrikrisNo ratings yet

- Simplified High-Accuracy Calculation of Eddy-Current Losses in Round-Wire WindingsDocument8 pagesSimplified High-Accuracy Calculation of Eddy-Current Losses in Round-Wire WindingsshrikrisNo ratings yet

- Control Systems Block Diagram Reduction Www-TutorialspointDocument2 pagesControl Systems Block Diagram Reduction Www-TutorialspointshrikrisNo ratings yet

- Stray-Current Losses in Stranded Windings of Transformers Bu KaulDocument10 pagesStray-Current Losses in Stranded Windings of Transformers Bu KaulshrikrisNo ratings yet

- A Very Accurate Measurement System For Multielectrode Capacitive Sensors - Excellent - PaperDocument5 pagesA Very Accurate Measurement System For Multielectrode Capacitive Sensors - Excellent - PapershrikrisNo ratings yet

- Control Systems Block Diagram Reduction and Mason's Formula Www-TutorialspointDocument8 pagesControl Systems Block Diagram Reduction and Mason's Formula Www-TutorialspointshrikrisNo ratings yet

- Input Impedance Measurements For Stable Input Filter Design by OMICRONDocument22 pagesInput Impedance Measurements For Stable Input Filter Design by OMICRONshrikrisNo ratings yet

- The Skin Effect - Philips Technical Review Volume28Document16 pagesThe Skin Effect - Philips Technical Review Volume28shrikrisNo ratings yet

- Control Systems Control Systems Masons Gain Formula-Www-Tutorialspoint-ComDocument6 pagesControl Systems Control Systems Masons Gain Formula-Www-Tutorialspoint-ComshrikrisNo ratings yet

- Input Filter Interactions With Switching by BassoDocument166 pagesInput Filter Interactions With Switching by BassoshrikrisNo ratings yet

- Input Filter Design by EricksonDocument49 pagesInput Filter Design by EricksonshrikrisNo ratings yet

- Design of PID ControllerDocument13 pagesDesign of PID ControllershrikrisNo ratings yet

- A Low-Cost Highly Stable Reference Capacitor For Capacitive Sensor SystemsDocument5 pagesA Low-Cost Highly Stable Reference Capacitor For Capacitive Sensor SystemsshrikrisNo ratings yet

- Input Filter Design Example Biricha Digital Power LTDDocument5 pagesInput Filter Design Example Biricha Digital Power LTDshrikrisNo ratings yet

- EMI Filter Design For An Isolated DC-DC Boost ConverterDocument25 pagesEMI Filter Design For An Isolated DC-DC Boost ConvertershrikrisNo ratings yet

- EROR AMPLIFIER AND COMPENSATION NETWORK DESIGN Slup069Document4 pagesEROR AMPLIFIER AND COMPENSATION NETWORK DESIGN Slup069shrikris0% (1)

- Input Filter Compensation For Switching Regulators by S S KelkarDocument371 pagesInput Filter Compensation For Switching Regulators by S S KelkarshrikrisNo ratings yet

- Internal Compensation - Boon or Bane Slup174Document14 pagesInternal Compensation - Boon or Bane Slup174shrikrisNo ratings yet

- A Practical Method For Separating Common-Mode and Differential-Mode Emissions in Conducted Emissions Testing by Analog DrevicesDocument4 pagesA Practical Method For Separating Common-Mode and Differential-Mode Emissions in Conducted Emissions Testing by Analog DrevicesshrikrisNo ratings yet

- Frequency Response Measurements For Switching Power Supplies Slup121Document13 pagesFrequency Response Measurements For Switching Power Supplies Slup121shrikrisNo ratings yet

- 5 KW Two-Channel Interleaved CCM PFC EVAL Board InfineonDocument41 pages5 KW Two-Channel Interleaved CCM PFC EVAL Board InfineonshrikrisNo ratings yet

- Performance Comparison of Ferrite and Nanocrystalline Cores For Medium-Frequency Transformer of DC-DC ConverterDocument21 pagesPerformance Comparison of Ferrite and Nanocrystalline Cores For Medium-Frequency Transformer of DC-DC ConvertershrikrisNo ratings yet