Professional Documents

Culture Documents

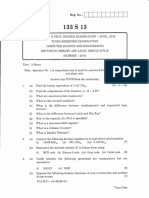

Sri Indu College of Engineering & Technology: Setno1 Code No.: R20Ece2102

Uploaded by

mohanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sri Indu College of Engineering & Technology: Setno1 Code No.: R20Ece2102

Uploaded by

mohanCopyright:

Available Formats

Set NO 1

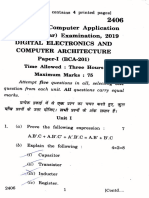

Code No.: R20ECE2102

SRI INDU COLLEGE OF ENGINEERING & TECHNOLOGY

(An Autonomous Institution under UGC, New Delhi)

Recognized under 2(f) and 12(B) of UGC Act 1956

DIGITAL LOGIC DESIGN

Time: 3 Hours Max Marks: 70

Part - A (5Q X 4M = 20 marks)

Marks Course BT

outcome . Level

1 Implement the function with only NAND gates: F(x,y,z) = Σ(0,6). (4) Postulates of 5

Boolean algebra

2 What are Hazards? List their types. (4) Known about 1

the Hazards

3 Differentiate combinational and sequential circuits? (4) Known about 3

the different

circuits.

4 What is a Ring Counter? What are applications of Ring counters? (4) Analyzing the 2

sequential

circuits

5 Write capabilities and limitations of Finite-State machine. (4) Known about 4

the FSM

Part – B (5Q X 10M = 50 Marks)

UNIT-I Understand the

numerical

6. a) i) Convert the given Octal number (2564. 603)8 to Hexadecimal Number. (10) information in 3

different forms.

ii) Given that (81)10 = (100)X , Find the value of X.

b) Encode data bits 1101 into 7 bit even parity Hamming Code.

(OR) 5

7. a) Expand min-term and maxterm AB′+ABD′+A+ABC′D.

b) Prove that AB'C + B + BD'+ ABD'+ A'C = B + C.

UNIT - II Realization of

K-map and

8. a) Simplify the following Boolean expression using K- map and implement (10) designing of 4

them with NOR logic gates F(A,B,C,D)= m ( 1,3,7,11,15 ) + d(0,2,5) combinational

circuits

b) Draw and explain the full adder circuit using two half adder circuits.

( OR)

9. a) Design a digital system to compare two binary numbers of 1 bit by using

logic gates. 6

b) Design and explain a 3 to 8 decoder with necessary truth table and logic

diagram.

UNIT - III (10) Analysing the

different

10. a) Derive the characteristic equation for JK flip-flop and T flip-flop. flipflops. 1

b) Discuss about binary cell in detail.

(OR) (10)

11. a) With the aid of external logic, convert D type flip-flop to a SR flip-flop. 3

b) Explain master slave JK flip-flop with neat timing diagram.

UNIT - IV (10) Designing of

sequential

12. Draw the circuit of mod-12 asynchronous up and down counter using JK circuits. 4

flip-flop.

(OR)

13. a) Construct a Johnson counter for 10 timing signals.

2

b) What are the fundamentals of Sequential machine operation?

UNIT-V (10) Analyse ASM

charts and

14. a) Draw the State diagram, State table and ASM chart for a D flip-flop. Moore model. 4

b) With a neat block diagram, explain the Moore model of a clocked

synchronous sequential circuit.

( OR)

6

15. Design a sequential logic circuit of a 4 bit counter to start counting from

0000 to 1000 and this process should go on. Draw the ASM chart and design

the Data processing unit and the control unit.

Note: Subdivisions if required can be added Eg: 6(a), 6(b)… and suitable marks need to be mentioned

Summary (to be filled by the question paper setter):

Indicate the percentage for each of the following criteria from the questions framed; Total no of questions

given:

Bloom Taxonomy level No.of

question % Name of Paper setter

s

1. Fundamental knowledge from Level I & II 4 27

2.Knowledge on application and analysis from Level III & IV 7 46

3.Critical thinking and ability to design from Level V & VI 4 27

You might also like

- Transistor Switching and Sequential CircuitsFrom EverandTransistor Switching and Sequential CircuitsRating: 5 out of 5 stars5/5 (1)

- Allison Prognostics BodygearsDocument4 pagesAllison Prognostics Bodygearsrbrto100% (1)

- The ISO 13381-1 Standard's Failure Prognostics Process Through An Example-2010-12pDocument12 pagesThe ISO 13381-1 Standard's Failure Prognostics Process Through An Example-2010-12pwylfredy100% (1)

- Topics in Engineering Logic: International Series of Monographs on Electronics and InstrumentationFrom EverandTopics in Engineering Logic: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- db2 Working in LabDocument44 pagesdb2 Working in Labahw0000007No ratings yet

- Ignition wiring diagram under 40 charactersDocument1 pageIgnition wiring diagram under 40 charactersNofriagara Davit HarnawanNo ratings yet

- The Supply Chain Planner'S Playbook: Plan To WinDocument37 pagesThe Supply Chain Planner'S Playbook: Plan To WinRasul11No ratings yet

- Q 6Document3 pagesQ 6Saranya MohanNo ratings yet

- Question Paper Code:: (10 2 20 Marks)Document2 pagesQuestion Paper Code:: (10 2 20 Marks)AbdulAzizNo ratings yet

- Ect203 Logic Circuit Design, December 2021Document2 pagesEct203 Logic Circuit Design, December 2021instapc0210No ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- TED (15) 3133 qp-1Document2 pagesTED (15) 3133 qp-1Anna JoseNo ratings yet

- Digital Systems and Applications TitleDocument2 pagesDigital Systems and Applications Titletk starNo ratings yet

- 08AB303 DIGITAL LOGIC CIRCUITS_1Document3 pages08AB303 DIGITAL LOGIC CIRCUITS_1Chandru RamaswamyNo ratings yet

- VI Sem Jun-July 2005Document10 pagesVI Sem Jun-July 2005Suraj KumarNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- CS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital ElectronicsDocument3 pagesCS3CO29-EC-EI3CO07-IT3CO09-OE00005 Digital Electronicschouhanraman822No ratings yet

- De MJ07Document2 pagesDe MJ07prayog8No ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- Part 'B' May Be Attempted in Rest of The Sheets of Answer SheetDocument6 pagesPart 'B' May Be Attempted in Rest of The Sheets of Answer SheetAhmar khan 04 / EveNo ratings yet

- Cs-64: Introtruct - On To Computeb Organisation: Bachelor in Computer Appucations Term-End Examination June. 2oo8Document4 pagesCs-64: Introtruct - On To Computeb Organisation: Bachelor in Computer Appucations Term-End Examination June. 2oo8sirajscribdNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- Ec6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesDocument12 pagesEc6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesSurendar PNo ratings yet

- STLD 1Document2 pagesSTLD 1ANUPAMA PonnuNo ratings yet

- De 3Document4 pagesDe 3Devansh SinghNo ratings yet

- STLDDocument2 pagesSTLDANUPAMA PonnuNo ratings yet

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- 22323-2019-Winter-Question-Paper (Msbte Study Resources)Document3 pages22323-2019-Winter-Question-Paper (Msbte Study Resources)Parth patkarNo ratings yet

- MCS 12Document5 pagesMCS 12Divya KumariNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)rajkumarsac100% (1)

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- Ec 1202 Digital System DesignDocument8 pagesEc 1202 Digital System DesignworkubNo ratings yet

- Computer Architecture Exam QuestionsDocument2 pagesComputer Architecture Exam QuestionsNâñè DévrûNo ratings yet

- de PDFDocument2 pagesde PDFUnknown userNo ratings yet

- Hours) :: DMMCA (.1tDocument2 pagesHours) :: DMMCA (.1tsagar batraNo ratings yet

- March 2008 Paper 2Document2 pagesMarch 2008 Paper 2many1tothe11No ratings yet

- 15A04502 Digital Communication Systems (2) - 1Document1 page15A04502 Digital Communication Systems (2) - 117BF1A04L7 kalyanNo ratings yet

- 2022 Dec. ECT203-CDocument2 pages2022 Dec. ECT203-CAthul RamNo ratings yet

- 07af303 - Digital Integrated Circuits and Logical DesignDocument3 pages07af303 - Digital Integrated Circuits and Logical DesignChandru RamaswamyNo ratings yet

- MP2 Coa BCS302 Paper 2022-23Document2 pagesMP2 Coa BCS302 Paper 2022-23mcuthor98No ratings yet

- LOC (1st) Dec2018Document2 pagesLOC (1st) Dec2018Anshul JangraNo ratings yet

- 9A04306 Digital Logic Design1Document4 pages9A04306 Digital Logic Design1Mahaboob SubahanNo ratings yet

- Ramaiah: Semester End Examinations FebruaryDocument3 pagesRamaiah: Semester End Examinations Februarysaikar.challaNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- SS 9A04306 Digital Logic DesignDocument1 pageSS 9A04306 Digital Logic DesignMahaboob SubahanNo ratings yet

- Ece361 - Ee 2010 S1Document5 pagesEce361 - Ee 2010 S1Mu'izz KaharNo ratings yet

- Hours /-: ThirdDocument3 pagesHours /-: ThirdAhmad UmarNo ratings yet

- Digital Electronics Exam QuestionsDocument3 pagesDigital Electronics Exam Questionsनीरज बंसलNo ratings yet

- nov - dec 2021Document3 pagesnov - dec 2021Pandyselvi BalasubramanianNo ratings yet

- 15A04502 Digital Communication Systems (1) - 1Document1 page15A04502 Digital Communication Systems (1) - 117BF1A04L7 kalyanNo ratings yet

- Digital Electronics: 17333 Seat Exam Question PaperDocument4 pagesDigital Electronics: 17333 Seat Exam Question PaperYogesh KuteNo ratings yet

- EC 1312 - Digital Logic Circuits Question BankDocument5 pagesEC 1312 - Digital Logic Circuits Question BankDeepak RavichandranNo ratings yet

- Ect203 Logic Circuit Design, December 2022Document2 pagesEct203 Logic Circuit Design, December 2022ShakiraNo ratings yet

- B.E./B.Tech. Degree Examinations Information Coding Techniques Question PaperDocument3 pagesB.E./B.Tech. Degree Examinations Information Coding Techniques Question PaperSaravanan SadhasivamNo ratings yet

- Smart Materials, Sensors and ActuatorsDocument2 pagesSmart Materials, Sensors and ActuatorsmanojNo ratings yet

- P15ec33 Z1Document2 pagesP15ec33 Z1Arun Kumar K MNo ratings yet

- 13A04306 Digital Logic Design1Document1 page13A04306 Digital Logic Design1Mahaboob SubahanNo ratings yet

- 15A04502 Digital Communication Systems (3) - 1Document1 page15A04502 Digital Communication Systems (3) - 117BF1A04L7 kalyanNo ratings yet

- R5 210504 Digital Logic DesignDocument1 pageR5 210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- Question Paper Code: X10348: Reg. NoDocument2 pagesQuestion Paper Code: X10348: Reg. NoJaikumar RajendranNo ratings yet

- Jntua University Previous Question Papers: Dept., of E.C.E, RCEWDocument4 pagesJntua University Previous Question Papers: Dept., of E.C.E, RCEWHarshini ANo ratings yet

- Nov Dec 2013Document6 pagesNov Dec 2013abdnazar2003No ratings yet

- Ignou MCS 14Document5 pagesIgnou MCS 14Abhishek MandalNo ratings yet

- Integration of One-forms on P-adic Analytic Spaces. (AM-162)From EverandIntegration of One-forms on P-adic Analytic Spaces. (AM-162)No ratings yet

- 02 - R20 I Yr M.Tech (Embedded Systems) I Sem - SyllabusDocument36 pages02 - R20 I Yr M.Tech (Embedded Systems) I Sem - SyllabusmohanNo ratings yet

- Front Unrev2Document9 pagesFront Unrev2mohanNo ratings yet

- Lossless Medical Image Compression Using Combinatorial TransformsDocument2 pagesLossless Medical Image Compression Using Combinatorial TransformsmohanNo ratings yet

- VLSI Design Mid 2Document3 pagesVLSI Design Mid 2mohanNo ratings yet

- JNTUH BTech Project GuidelinesDocument6 pagesJNTUH BTech Project GuidelinesmohanNo ratings yet

- Massive MIMO in Real Propagation Environments: Do All Antennas Contribute Equally?Document12 pagesMassive MIMO in Real Propagation Environments: Do All Antennas Contribute Equally?mohanNo ratings yet

- B. Tech II Year I Semester Examinations, 2022: Electronic Devices and Circuits Time: 3 Hours Max. Marks: 75Document3 pagesB. Tech II Year I Semester Examinations, 2022: Electronic Devices and Circuits Time: 3 Hours Max. Marks: 75mohanNo ratings yet

- Matter UnrevDocument77 pagesMatter UnrevmohanNo ratings yet

- Rain Detection and Automatic Retractable Roof System Using ArduinoDocument34 pagesRain Detection and Automatic Retractable Roof System Using ArduinomohanNo ratings yet

- Full Time Ph.D.-2021 (For JRF Fellowship Awarded Candidates) - List of Eligible Candidates For InterviewDocument1 pageFull Time Ph.D.-2021 (For JRF Fellowship Awarded Candidates) - List of Eligible Candidates For InterviewmohanNo ratings yet

- On Probability Theory &stochastic ProcessDocument101 pagesOn Probability Theory &stochastic ProcessmohanNo ratings yet

- On Probability Theory &stochastic ProcessDocument101 pagesOn Probability Theory &stochastic ProcessmohanNo ratings yet

- On Probability Theory &stochastic ProcessDocument101 pagesOn Probability Theory &stochastic ProcessmohanNo ratings yet

- Telangana govt extends contract worker pay till Sept 2021Document2 pagesTelangana govt extends contract worker pay till Sept 2021mohanNo ratings yet

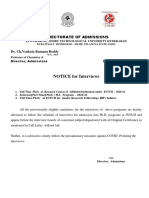

- Interview Call Letter For External (Part Time) and Full Time Ph.D. Programs - 2021Document1 pageInterview Call Letter For External (Part Time) and Full Time Ph.D. Programs - 2021mohanNo ratings yet

- Full Time Ph.D.-2021 List of Eligible Candidates For InterviewDocument9 pagesFull Time Ph.D.-2021 List of Eligible Candidates For InterviewmohanNo ratings yet

- JNTUH PhD admission scheduleDocument4 pagesJNTUH PhD admission schedulemohanNo ratings yet

- R16B TECHECEIVYearSyllabus PDFDocument242 pagesR16B TECHECEIVYearSyllabus PDFBasava RajuNo ratings yet

- Full Time Ph.D.-2021 List of Eligible Candidates For InterviewDocument9 pagesFull Time Ph.D.-2021 List of Eligible Candidates For InterviewmohanNo ratings yet

- Full Time Ph.D.-2021 (For JRF Fellowship Awarded Candidates) - List of Eligible Candidates For InterviewDocument1 pageFull Time Ph.D.-2021 (For JRF Fellowship Awarded Candidates) - List of Eligible Candidates For InterviewmohanNo ratings yet

- JNTU PhD Interview ScheduleDocument4 pagesJNTU PhD Interview SchedulemohanNo ratings yet

- Itr-1 A.y.2021-22Document2 pagesItr-1 A.y.2021-22Pretty AngelNo ratings yet

- Interview Call Letter For External (Part Time) and Full Time Ph.D. Programs - 2021Document1 pageInterview Call Letter For External (Part Time) and Full Time Ph.D. Programs - 2021mohanNo ratings yet

- Interview Schedule For External (Part Time) and Full Time Ph.D. Programs-2020-21Document4 pagesInterview Schedule For External (Part Time) and Full Time Ph.D. Programs-2020-21mohanNo ratings yet

- R16B TECHECEIVYearSyllabus PDFDocument242 pagesR16B TECHECEIVYearSyllabus PDFBasava RajuNo ratings yet

- Instrctions To The CandidatesDocument1 pageInstrctions To The CandidatesmohanNo ratings yet

- Pdfmergerfreecom Handbook of Biomedical Instrumentation Third EditioncompressDocument2 pagesPdfmergerfreecom Handbook of Biomedical Instrumentation Third EditioncompressmohanNo ratings yet

- Handbook of Biomedical Instrumentation by Rs KhandpurDocument1 pageHandbook of Biomedical Instrumentation by Rs KhandpurTagore Drnt0% (1)

- R16B TECHECEIVYearSyllabus PDFDocument242 pagesR16B TECHECEIVYearSyllabus PDFBasava RajuNo ratings yet

- For AWS Cloud Architects, Solutions Architects and EngineersDocument4 pagesFor AWS Cloud Architects, Solutions Architects and EngineersjondraxdNo ratings yet

- Lecture 4 - 5 - 6 - CSE - Microprocessor and Assembly LanguageDocument63 pagesLecture 4 - 5 - 6 - CSE - Microprocessor and Assembly LanguagefaridulNo ratings yet

- Java8 New Features - Study GuideDocument96 pagesJava8 New Features - Study GuideVikash KumarNo ratings yet

- What Is GRCDocument1 pageWhat Is GRCjacobR9BNo ratings yet

- Pal - Piwg1 PIWG2.LA 6751p.la 6753P.rev.0.3.SchematicsDocument60 pagesPal - Piwg1 PIWG2.LA 6751p.la 6753P.rev.0.3.SchematicsAngel AlarasNo ratings yet

- 830 00741 51 - NetHorizon - ZMS ClientDocument714 pages830 00741 51 - NetHorizon - ZMS Clientpolan78100% (1)

- Optimize Wireless Network Performance with iEon EMSDocument4 pagesOptimize Wireless Network Performance with iEon EMSBhuvnesh SachdevaNo ratings yet

- Mini Project ReportDocument48 pagesMini Project ReportDibakar Das GuptaNo ratings yet

- Integrated Flood Analysis System (IFAS)Document2 pagesIntegrated Flood Analysis System (IFAS)Umer MalikNo ratings yet

- Once Again Do Not Delete This Email As It 100% Sure From HSBC BANK UKDocument1 pageOnce Again Do Not Delete This Email As It 100% Sure From HSBC BANK UKPraveenKvNo ratings yet

- Características Técnicas y MetrológicasDocument2 pagesCaracterísticas Técnicas y MetrológicasChuy DiazNo ratings yet

- School Learning Continuity PlanDocument39 pagesSchool Learning Continuity Planreginald_adia_1No ratings yet

- Iut JournalDocument20 pagesIut JournalRong GuoNo ratings yet

- InkZone Perfect: Fast, Affordable Ink Key PresettingDocument2 pagesInkZone Perfect: Fast, Affordable Ink Key PresettingTheJuankyNo ratings yet

- Technologies empower hospital patientsDocument2 pagesTechnologies empower hospital patientsxyrahNo ratings yet

- Ricardo Aguirre: Professional Scrum MasterDocument1 pageRicardo Aguirre: Professional Scrum MasterDiego Velásquez AscuyNo ratings yet

- Region VII School Brigada ReportDocument2 pagesRegion VII School Brigada ReportJundell DiazNo ratings yet

- BX-B2 Semi-Automatic Bottle Blowing Machine Taizhou FactoryDocument4 pagesBX-B2 Semi-Automatic Bottle Blowing Machine Taizhou FactoryAriantoNo ratings yet

- DeviceNet BrochureDocument251 pagesDeviceNet BrochureabufaruqiNo ratings yet

- DVIN0009 M800 OEM WRX56 Installation Document 3Document15 pagesDVIN0009 M800 OEM WRX56 Installation Document 3Gilang AdityaNo ratings yet

- ZS11 EU6B6D Manual de Autoaprendizaje y Programación Del Módulo 20180329Document37 pagesZS11 EU6B6D Manual de Autoaprendizaje y Programación Del Módulo 20180329tallerr.360No ratings yet

- Management Information Systems: James A O'Brien George M Marakas Ramesh BehlDocument59 pagesManagement Information Systems: James A O'Brien George M Marakas Ramesh BehlTanya SinghNo ratings yet

- Regulated Infrastructure For Bitcoin Markets and CustodyDocument2 pagesRegulated Infrastructure For Bitcoin Markets and Custodymatiaslmart4571No ratings yet

- DB2 PureScale RedbookDocument306 pagesDB2 PureScale Redbookwangyt0821No ratings yet

- Understanding Number Systems From Binary to DecimalDocument52 pagesUnderstanding Number Systems From Binary to DecimalXentrix CritzNo ratings yet