Professional Documents

Culture Documents

Mitsubishi Semiconductor

Uploaded by

pavelOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Mitsubishi Semiconductor

Uploaded by

pavelCopyright:

Available Formats

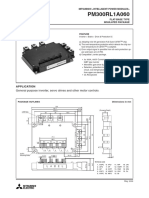

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21963-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

PS21963-4S

INTEGRATED POWER FUNCTIONS

600V/10A low-loss 5th generation IGBT inverter bridge for

three phase DC-to-AC power conversion.

Open emitter type.

INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

• For upper-leg IGBTS :Drive circuit, High voltage high-speed level shifting, Control supply under-voltage (UV) protection.

• For lower-leg IGBTS : Drive circuit, Control supply under-voltage protection (UV), Short circuit protection (SC).

• Fault signaling : Corresponding to an SC fault (Lower-leg IGBT) or a UV fault (Lower-side supply).

• Input interface : 3V, 5V line (High Active).

• UL Approved : Yellow Card No. E80276

APPLICATION

AC100V~200V inverter drive for small power motor control.

Fig. 1 PACKAGE OUTLINES www.DataSheet.net/

Dimensions in mm

38 ±0.5

A B 3.5 TERMINAL CODE

20×1.778(=35.56 )

0.28 35 ±0.3 1.5 ±0.05 1. (VNC)

0.4

1.778 ±0.2 16-0.5 2. VUFB

3. VVFB

(1)

17 1 4. VWFB

5. UP

6. VP

7. WP

14.4 ±0.5

8. VP1

9. VNC *

(3.5)

(3.3)

10. UN

11. VN

33.7 ±0.5

29.2 ±0.5

24 ±0.5

12. WN

13. VN1

.6

2-

R1

QR Type name 14. FO

15. CIN

18.9 ±0.5

14.4 ±0.5

16. VNC *

12

Lot No. 0.8

Code 17. NC

3 MIN HEAT SINK SIDE 18. NW

19. NV

20. NU

18 25 21. W

22. V

23. U

0.28 24. P

2.54 ±0.2 8-0.6 25. NC

0.4

4-C1.2

14×2.54(=35.56) 2.5 MIN

0.5 0.5

0.5 0.5 (2.656)

1.5m

in

(0°~5°)

9.5 ±0.5

(1.2)

(1.2)

(2.756)

5.5 ±0.5

HEAT SINK SIDE

DETAIL A DETAIL B

*) Two VNC terminals (9 & 16 pin) are connected inside DIP-IPM, please connect either one to the 15V power supply GND outside and

leave another one open.

Mar. 2007

Datasheet pdf - http://www.DataSheet4U.co.kr/

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21963-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

MAXIMUM RATINGS (Tj = 25°C, unless otherwise noted)

INVERTER PART

Symbol Parameter Condition Ratings Unit

VCC Supply voltage Applied between P-NU, NV, NW 450 V

VCC(surge) Supply voltage (surge) Applied between P-NU, NV, NW 500 V

VCES Collector-emitter voltage 600 V

±IC Each IGBT collector current TC = 25°C 10 A

±ICP Each IGBT collector current (peak) TC = 25°C, less than 1ms 20 A

PC Collector dissipation TC = 25°C, per 1 chip 27.0 W

Tj Junction temperature (Note 1) –20~+125 °C

Note 1 : The maximum junction temperature rating of the power chips integrated within the DIP-IPM is 150°C (@ TC ≤ 100°C). However, to

ensure safe operation of the DIP-IPM, the average junction temperature should be limited to Tj(ave) ≤ 125°C (@ TC ≤ 100°C).

CONTROL (PROTECTION) PART

Symbol Parameter Condition Ratings Unit

VD Control supply voltage Applied between VP1-VNC, VN1-VNC 20 V

VDB Control supply voltage Applied between VUFB-U, VVFB-V, VWFB-W 20 V

Applied between UP, VP, WP, UN, VN,

VIN Input voltage –0.5~VD+0.5 V

WN-VNC

VFO Fault output supply voltage Applied between FO-VNC –0.5~VD+0.5 V

IFO Fault output current Sink current at FO terminal 1 mA

VSC Current sensing input voltage Applied between CIN-VNC –0.5~VD+0.5 V

TOTAL SYSTEM

Symbol Parameter Condition Ratings Unit

VD = 13.5~16.5V, Inverter part

VCC(PROT) Self protection supply voltage limit

www.DataSheet.net/

Tj = 125°C, non-repetitive, less than 2µs 400 V

(short circuit protection capability)

TC Module case operation temperature (Note 2) –20~+100 °C

Tstg Storage temperature –40~+125 °C

60Hz, Sinusoidal, 1 minute,

Viso Isolation voltage 1500 Vrms

Between pins and heat-sink plate

Note 2: TC measurement point

Control terminals DIP-IPM

11.6mm

3mm

IGBT chip position

TC point

FWD chip position

Heat sink side

Power terminals

Mar. 2007

Datasheet pdf - http://www.DataSheet4U.co.kr/

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21963-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

THERMAL RESISTANCE

Limits

Symbol Parameter Condition Unit

Min. Typ. Max.

Rth(j-c)Q Junction to case thermal Inverter IGBT part (per 1/6 module) — — 3.7 °C/W

Rth(j-c)F resistance (Note 3) Inverter FWD part (per 1/6 module) — — 4.5 °C/W

Note 3 : Grease with good thermal conductivity should be applied evenly with about +100µm~+200µm on the contacting surface of DIP-IPM

and heat-sink.

The contacting thermal resistance between DIP-IPM case and heat sink (Rth(c-f)) is determined by the thickness and the thermal

conductivity of the applied grease. For reference, Rth(c-f) (per 1/6 module) is about 0.3°C/W when the grease thickness is 20µm and

the thermal conductivity is 1.0W/m·k.

ELECTRICAL CHARACTERISTICS (Tj = 25°C, unless otherwise noted)

INVERTER PART

Limits

Symbol Parameter Condition Unit

Min. Typ. Max.

Collector-emitter saturation VD = VDB = 15V IC = 10A, Tj = 25°C — 1.70 2.20

VCE(sat) V

voltage VIN = 5V IC = 10A, Tj = 125°C — 1.80 2.30

VEC FWD forward voltage Tj = 25°C, –IC = 10A, VIN = 0V — 1.70 2.20 V

ton 0.60 1.10 1.70 µs

trr VCC = 300V, VD = VDB = 15V — 0.30 — µs

tc(on) Switching times IC = 10A, Tj = 125°C, VIN = 0 ↔ 5V — 0.40 0.60 µs

toff Inductive load (upper-lower arm) — 1.50 2.10 µs

tc(off) — 0.50 0.80 µs

Collector-emitter cut-off Tj = 25°C — — 1

ICES VCE = VCES mA

current Tj = 125°C — — 10

CONTROL (PROTECTION) PART www.DataSheet.net/

Limits

Symbol Parameter Condition Unit

Min. Typ. Max.

VD = VDB = 15V Total of VP1-VNC, VN1-VNC — — 2.80

VIN = 5V VUFB-U, VVFB-V, VWFB-W — — 0.55

ID Circuit current mA

VD = VDB = 15V Total of VP1-VNC, VN1-VNC — — 2.80

VIN = 0V VUFB-U, VVFB-V, VWFB-W — — 0.55

VFOH VSC = 0V, FO terminal pull-up to 5V by 10kΩ 4.9 — — V

Fault output voltage

VFOL VSC = 1V, IFO = 1mA — — 0.95 V

VSC(ref) Short circuit trip level Tj = 25°C, VD = 15V (Note 4) 0.43 0.48 0.53 V

IIN Input current VIN = 5V 0.70 1.00 1.50 mA

UVDBt Trip level 10.0 — 12.0 V

UVDBr Control supply under-voltage Reset level 10.5 — 12.5 V

protection Tj ≤ 125°C

UVDt Trip level 10.3 — 12.5 V

UVDr Reset level 10.8 — 13.0 V

tFO Fault output pulse width (Note 5) 20 — — µs

Vth(on) ON threshold voltage — 2.1 2.6 V

Vth(off) OFF threshold voltage 0.8 1.3 — V

Applied between UP, VP, WP, UN, VN, WN-VNC

ON/OFF threshold hysteresis

Vth(hys) 0.35 0.65 — V

voltage

Note 4 : Short circuit protection is functioning only for the lower-arms. Please select the external shunt resistance such that the SC trip-level is

less than 1.7 times of the current rating.

5 : Fault signal is asserted corresponding to a short circuit or lower side control supply under-voltage failure.

Mar. 2007

Datasheet pdf - http://www.DataSheet4U.co.kr/

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21963-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

MECHANICAL CHARACTERISTICS AND RATINGS

Limits

Parameter Condition Unit

Min. Typ. Max.

Mounting screw : M3

Mounting torque Recommended : 0.69 N·m 0.59 — 0.78 N·m

(Note 6)

Weight — 10 — g

Heat-sink flatness (Note 7) –50 — 100 µm

Note 6 : Plain washers (ISO 7089~7094) are recommended.

Note 7: Flatness measurement position

Measurement position

+ – 4.6mm

DIP-IPM

Heat sink side

–

+

Heat sink side

RECOMMENDED OPERATION CONDITIONS www.DataSheet.net/

Limits

Symbol Parameter Condition Unit

Min. Typ. Max.

VCC Supply voltage Applied between P-NU, NV, NW 0 300 400 V

VD Control supply voltage Applied between VP1-VNC, VN1-VNC 13.5 15.0 16.5 V

VDB Control supply voltage Applied between VUFB-U, VVFB-V, VWFB-W 13.0 15.0 18.5 V

∆VD, ∆VDB Control supply variation –1 — 1 V/µs

tdead Arm shoot-through blocking time For each input signal, TC ≤ 100°C 1.5 — — µs

fPWM PWM input frequency TC ≤ 100°C, Tj ≤ 125°C — — 20 kHz

VCC = 300V, VD = VDB = 15V, fPWM = 5kHz — — 5.0

IO Allowable r.m.s. current P.F = 0.8, sinusoidal PWM, Arms

Tj ≤ 125°C, TC ≤ 100°C (Note 8) fPWM = 15kHz — — 3.0

PWIN(on) Allowable minimum input 0.5 — —

µs

PWIN(off) pulse width (Note 9) 0.5 — —

VNC VNC variation Between VNC-NU, NV, NW (including surge) –5.0 — 5.0 V

Note 8 : The allowable r.m.s. current value depends on the actual application conditions.

9 : IPM might not make response if the input signal pulse width is less than the recommended minimum value.

Mar. 2007

Datasheet pdf - http://www.DataSheet4U.co.kr/

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21963-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

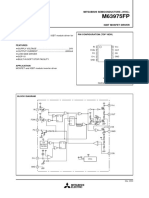

Fig. 2 THE DIP-IPM INTERNAL CIRCUIT

VUFB DIP-IPM

HVIC P

VP1 VCC VUB IGBT1 Di1

UP UP UOUT

VNC COM VUS U

VVFB VVB IGBT2 Di2

VP VP VOUT

VVS V

VWFB VWB IGBT3 Di3

WP WP WOUT

VWS W

IGBT4 Di4

LVIC

www.DataSheet.net/

UOUT

VN1 VCC NU

IGBT5 Di5

VOUT

UN UN

NV

VN VN IGBT6 Di6

WN WN

WOUT

Fo Fo CIN

NW

VNO

VNC GND

CIN

Mar. 2007

Datasheet pdf - http://www.DataSheet4U.co.kr/

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21963-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 3 TIMING CHART OF THE DIP-IPM PROTECTIVE FUNCTIONS

[A] Short-Circuit Protection (Lower-side only with the external shunt resistor and CR filter)

a1. Normal operation : IGBT ON and carrying current.

a2. Short circuit detection (SC trigger).

a3. IGBT gate hard interruption.

a4. IGBT turns OFF.

a5. FO outputs (tFO(min) = 20µs).

a6. Input “L” : IGBT OFF.

a7. Input “H” : IGBT ON.

a8. IGBT OFF in spite of input “H”.

Lower-side control a6 a7

input

Protection circuit state SET RESET

Internal IGBT gate

a3

a2

SC a4

a1

Output current Ic a8

SC reference voltage

Sense voltage of the

shunt resistor

CR circuit time

constant DELAY

Error output Fo a5

www.DataSheet.net/

[B] Under-Voltage Protection (Lower-side, UVD)

b1. Control supply voltage rising : After the voltage level reaches UVDr, the circuits start to operate when next input is applied.

b2. Normal operation : IGBT ON and carrying current.

b3. Under voltage trip (UVDt).

b4. IGBT OFF in spite of control input condition.

b5. FO outputs (tFO ≥ 20µs and FO outputs continuously during UV period).

b6. Under voltage reset (UVDr).

b7. Normal operation : IGBT ON and carrying current.

Control input

Protection circuit state RESET SET

RESET

UVDr

Control supply voltage VD b1 UVDt b6

b3

b4

b2 b7

Output current Ic

Error output Fo

b5

Mar. 2007

Datasheet pdf - http://www.DataSheet4U.co.kr/

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21963-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

[C] Under-Voltage Protection (Upper-side, UVDB)

c1. Control supply voltage rising : After the voltage level reaches UVDBr, the circuits start to operate when next input is applied.

c2. Normal operation : IGBT ON and carrying current.

c3. Under voltage trip (UVDBt).

c4. IGBT OFF in spite of control input signal level, but there is no FO signal outputs.

c5. Under voltage reset (UVDBr).

c6. Normal operation : IGBT ON and carrying current.

Control input

Protection circuit state RESET SET RESET

UVDBr

Control supply voltage VDB c1 UVDBt c5

c3

c2 c4 c6

Output current Ic

High-level (no fault output)

Error output Fo

Fig. 4 RECOMMENDED MCU I/O INTERFACE CIRCUIT

5V line

10kΩ www.DataSheet.net/ DIP-IPM

UP,VP,WP,UN,VN,WN

MCU

3.3kΩ (min)

Fo

VNC(Logic)

Note : The setting of RC coupling at each input (parts shown dotted) depends on the PWM control scheme and the

wiring impedance of the printed circuit board.

The DIP-IPM input section integrates a 3.3kΩ (min) pull-down resistor. Therefore, when using an external

filtering resistor, pay attention to the turn-on threshold voltage.

Fig. 5 WIRING CONNECTION OF SHUNT RESISTOR

DIP-IPM Each wiring inductance should be less than 10nH.

Equivalent to the inductance of a copper

pattern in dimension of width=3mm,

thickness=100µm, length=17mm

VNC

NU

NV

NW

Shunt resistors

Please make the GND wiring connection

of shunt resistor to the VNC terminal

as close as possible.

Mar. 2007

Datasheet pdf - http://www.DataSheet4U.co.kr/

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21963-4S

TRANSFER-MOLD TYPE

INSULATED TYPE

Fig. 6 AN EXAMPLE OF TYPICAL DIP-IPM APPLICATION CIRCUIT

C1: Electrolytic capacitor with good temperature characteristics C2,C3: 0.22~2µF R-category ceramic capacitor for noise filtering

C2 C1 C2 C1 C2 C1

Bootstrap negative electrodes

should be connected to U, V,

W terminals directly and

separated from the main output

wires.

VUFB VVFB VWFB DIP-IPM

P

HVIC

VP1 VUB

VCC

C3

UP

UP UOUT

U

VUS

VVB

VP

VP VOUT

V

VVS M

VWB

WP

WP WOUT

VNC W

COM VWS

MCU

LVIC

UOUT

VN1 NU

VCC

5V line C3

VOUT

UN

UN NV

VN VN www.DataSheet.net/

WN

WN

WOUT

Fo

Fo CIN NW

VNO

VNC

GND Long wiring here might C

cause short-circuit.

CIN

Long wiring here might cause

Long GND wiring here might SC level fluctuation and

15V line

generate noise to input and malfunction.

cause IGBT malfunction. Shunt resistors

A

B R1 N1

+

C4

- Vref

B R1

+

C4

- Vref

B R1

OR Logic +

C4

- Vref

Comparator

External protection circuit

Note 1 : Input drive is High-Active type. There is a 3.3kΩ(min.) pull-down resistor integrated in the IC input circuit. To prevent malfunction, the wiring of each in-

put should be as short as possible. When using RC coupling circuit, make sure the input signal level meet the turn-on and turn-off threshold voltage.

2 : Thanks to HVIC inside the module, direct coupling to MCU without any opto-coupler or transformer isolation is possible.

3 : FO output is open drain type. It should be pulled up to the positive side of a 5V power supply by a resistor of about 10kΩ.

4 : To prevent erroneous protection, the wiring of A, B, C should be as short as possible.

5 : The time constant R1C4 of the protection circuit should be selected in the range of 1.5-2µs. SC interrupting time might vary with the

wiring pattern. Tight tolerance, temp-compensated type is recommended for R1, C4.

6 : All capacitors should be mounted as close to the terminals of the DIP-IPM as possible. (C1: good temperature, frequency character-

istic electrolytic type, and C2, C3: good temperature, frequency and DC bias characteristic ceramic type are recommended.)

7 : To prevent surge destruction, the wiring between the smoothing capacitor and the P, N1 terminals should be as short as possible.

Generally a 0.1-0.22µF snubber between the P-N1 terminals is recommended.

8 : Two VNC terminals (9 & 16 pin) are connected inside DIP-IPM, please connect either one to the 15V power supply GND outside and

leave another one open.

9 : It is recommended to insert a Zener diode (24V/1W) between each pair of control supply terminals to prevent surge destruction.

10 : If control GND is connected to power GND by broad pattern, it may cause malfunction by power GND fluctuation. It is recommended

to connect control GND and power GND at only a point.

11 : The reference voltage Vref of comparator should be set up the same rating of short circuit trip level (Vsc(ref): min.0.43V to max.0.53V).

12 : OR logic output high level should exceed the maximum short circuit trip level (Vsc(ref): max.0.53V).

Mar. 2007

Datasheet pdf - http://www.DataSheet4U.co.kr/

You might also like

- MITSUBISHI SEMICONDUCTOR Dual-In-Line Package Intelligent Power ModuleDocument8 pagesMITSUBISHI SEMICONDUCTOR Dual-In-Line Package Intelligent Power ModuleManoel Bernárdez VaccariNo ratings yet

- ps21964-st eDocument8 pagesps21964-st eAnonymous rrD8UKYNXNo ratings yet

- Ps21964-T/-At/-Ct/-Tw: Mitsubishi SemiconductorDocument10 pagesPs21964-T/-At/-Ct/-Tw: Mitsubishi SemiconductorTEMAINCOL SASNo ratings yet

- Ps21964-T/-At/-Ct/-Tw: Mitsubishi SemiconductorDocument10 pagesPs21964-T/-At/-Ct/-Tw: Mitsubishi SemiconductorLucas EmanuelNo ratings yet

- MITSUBISHI SEMICONDUCTOR Dual-In-Line Package Intelligent Power ModuleDocument9 pagesMITSUBISHI SEMICONDUCTOR Dual-In-Line Package Intelligent Power ModuleAsrielBritoTandiNo ratings yet

- Mitsubishi SemiconductorDocument9 pagesMitsubishi Semiconductorgiovanni anseNo ratings yet

- Electronics IGBT Drivers Principles and Applications Rev03 EXPDocument79 pagesElectronics IGBT Drivers Principles and Applications Rev03 EXPmmkayaNo ratings yet

- PM50CS1D060Document9 pagesPM50CS1D060Abdul KurniadiNo ratings yet

- MITSUBISHI INTELLIGENT POWER MODULE PM50RL1B120Document9 pagesMITSUBISHI INTELLIGENT POWER MODULE PM50RL1B120MuMoMaNo ratings yet

- PM300RL1A060Document9 pagesPM300RL1A060manuelvinicius1803No ratings yet

- pm50cl1b120 eDocument9 pagespm50cl1b120 eAndy LNo ratings yet

- Wiring Diagram: DP Mdrive Dual PtoDocument1 pageWiring Diagram: DP Mdrive Dual PtoCésar Arturo Pajuelo EspinozaNo ratings yet

- M63975FPDocument5 pagesM63975FPnk7562527No ratings yet

- Pm100rl1a120 E2Document9 pagesPm100rl1a120 E2Quang Pham DuyNo ratings yet

- DNSD 339 FDocument2 pagesDNSD 339 FrajeshdaveNo ratings yet

- Unipolar 2-Phase Stepping Motor Driver ICsDocument18 pagesUnipolar 2-Phase Stepping Motor Driver ICsDriss Ben MohamedNo ratings yet

- Fm400tu-2a eDocument6 pagesFm400tu-2a eThein Htoon lwinNo ratings yet

- Catalog TC510Document6 pagesCatalog TC510vietnguyenNo ratings yet

- 5M02659R FairchildDocument14 pages5M02659R Fairchildايهاب فوزيNo ratings yet

- 1.5A Step Down Switching RegulatorDocument12 pages1.5A Step Down Switching Regulatorjavier ortizNo ratings yet

- FLUKE 27 Schematic DiagramDocument4 pagesFLUKE 27 Schematic Diagrambudi0251No ratings yet

- MAX1795/MAX1796/ MAX1797 Low-Supply Current, Step-Up DC-DC Converters With True ShutdownDocument13 pagesMAX1795/MAX1796/ MAX1797 Low-Supply Current, Step-Up DC-DC Converters With True ShutdownEletrohelp EletrodomésticosNo ratings yet

- AD775 AnalogDevicesDocument12 pagesAD775 AnalogDeviceshector mirandaNo ratings yet

- 2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyDocument10 pages2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyAnonymous aP1FSUPoNo ratings yet

- Diagrama de EPB Hyundai Azera 2012Document2 pagesDiagrama de EPB Hyundai Azera 2012Jairo GodoyNo ratings yet

- Data Sheet: Part No. Package Code No. SSOP016-P-0225EDocument32 pagesData Sheet: Part No. Package Code No. SSOP016-P-0225Ekarti0660No ratings yet

- 12V Power in MSD6308RTDocument13 pages12V Power in MSD6308RTelz SetupNo ratings yet

- DatasheetDocument1 pageDatasheetmixespirit73No ratings yet

- 029 00065 0 2sa1746Document1 page029 00065 0 2sa1746karimNo ratings yet

- IS31PM7212_DSDocument12 pagesIS31PM7212_DSdavid.gjeorgevskiNo ratings yet

- Pm300cla060 eDocument8 pagesPm300cla060 eGael VazquezNo ratings yet

- PDF Fairchild 430756Document14 pagesPDF Fairchild 430756Giovanni Carrillo VillegasNo ratings yet

- 15175fs Marking SMD CodeDocument8 pages15175fs Marking SMD Code2dmsNo ratings yet

- lm5110 PDFDocument28 pageslm5110 PDFRizkyNo ratings yet

- IP-7Plus NANDDocument1 pageIP-7Plus NANDwallison AndradeNo ratings yet

- LCM1601BDocument1 pageLCM1601BJosueFNo ratings yet

- Mitsubishi BCR12PM TriacDocument5 pagesMitsubishi BCR12PM TriacErasmo Franco SNo ratings yet

- Sharp Microelectronics Pq1cz41h2zxh eDocument5 pagesSharp Microelectronics Pq1cz41h2zxh esu30mkii83gmail.comNo ratings yet

- PC924Document6 pagesPC924tahir0732No ratings yet

- Sprinter PSMDocument14 pagesSprinter PSMEzequias Mattos FerreiraNo ratings yet

- Step-Up DC-DC MAX8752Document13 pagesStep-Up DC-DC MAX8752Peter PicalNo ratings yet

- SMD lx5050rgb TRDocument4 pagesSMD lx5050rgb TRNikhil khadeNo ratings yet

- (3rz-Fe) Engine ControlDocument11 pages(3rz-Fe) Engine ControlJhon Sanchez Lopez100% (1)

- Healthview Mono Interconnect Diagram: Section 6Document15 pagesHealthview Mono Interconnect Diagram: Section 6alexis marcanoNo ratings yet

- L6565 DatasheetDocument17 pagesL6565 DatasheetJose BenavidesNo ratings yet

- 1 A 05Document4 pages1 A 05ciremanNo ratings yet

- WF18FTLAADNN0Document5 pagesWF18FTLAADNN0jamer estradaNo ratings yet

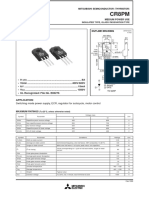

- Cr8Pm: Mitsubishi Semiconductor ThyristorDocument5 pagesCr8Pm: Mitsubishi Semiconductor ThyristorMahfud Adhi AnsoriNo ratings yet

- IDEA 1.4: Body Computer, Antena Code, Central de Injeção EletrônicaDocument1 pageIDEA 1.4: Body Computer, Antena Code, Central de Injeção EletrônicaPedro Almeida JuniorNo ratings yet

- AGM 1602B-818 Spec SheetDocument25 pagesAGM 1602B-818 Spec Sheet19thmnlfreemsNo ratings yet

- FSDH0165: Fairchild Power Switch (FPS)Document8 pagesFSDH0165: Fairchild Power Switch (FPS)vetchboyNo ratings yet

- Ct60am 18F PDFDocument5 pagesCt60am 18F PDFtecjadirNo ratings yet

- EPS ToyotaDocument1 pageEPS ToyotaAriel Prieto100% (1)

- Fracture ToughnessDocument286 pagesFracture ToughnessHusen TaufiqNo ratings yet

- Digital Power Electronics and ApplicationsFrom EverandDigital Power Electronics and ApplicationsRating: 3.5 out of 5 stars3.5/5 (3)

- Op Amps: Design, Application, and TroubleshootingFrom EverandOp Amps: Design, Application, and TroubleshootingRating: 5 out of 5 stars5/5 (2)

- Tracking Regulator TLE 4252: FeaturesDocument12 pagesTracking Regulator TLE 4252: FeaturespavelNo ratings yet

- 02wged PDFDocument284 pages02wged PDFAlex Box0% (1)

- 02wgeb PDFDocument782 pages02wgeb PDFAlex BoxNo ratings yet

- HYUNDAI R290LC Excavator Fault Codes DTCDocument11 pagesHYUNDAI R290LC Excavator Fault Codes DTCpavelNo ratings yet

- Yamaha Cygnus XC125 Service ManualDocument168 pagesYamaha Cygnus XC125 Service ManualpavelNo ratings yet

- Електро схема MLT 728 Tpowersh.547118EN - Group 80 (Electricity) 170215Document68 pagesЕлектро схема MLT 728 Tpowersh.547118EN - Group 80 (Electricity) 170215pavelNo ratings yet

- Orion - Prezentare ENGDocument2 pagesOrion - Prezentare ENGBenchia GabrielNo ratings yet

- NAS Remote Management Using IPMI On 5200 and 5300 MK-92HNAS092-00Document16 pagesNAS Remote Management Using IPMI On 5200 and 5300 MK-92HNAS092-00rerips.fakyuNo ratings yet

- Java Programming Lab 1Document15 pagesJava Programming Lab 1Minh Nguyễn QuangNo ratings yet

- V9-H Series Inverter User ManualDocument96 pagesV9-H Series Inverter User ManualkkcmNo ratings yet

- Work Experience: Birth Date: Birth Place: Age: Civil Status: Nationality: Height: Language SpokenDocument2 pagesWork Experience: Birth Date: Birth Place: Age: Civil Status: Nationality: Height: Language SpokenJohn De LeonNo ratings yet

- Hello From HeartDocument17 pagesHello From HeartArvind PavariyaNo ratings yet

- Migration Evaluator Collector Engagement Starter KitDocument4 pagesMigration Evaluator Collector Engagement Starter KitkkNo ratings yet

- Pfsense 1448Document15 pagesPfsense 1448Mahmoud AhmedNo ratings yet

- Dell Latitude 5410 14 Laptop White Papers En-UsDocument2 pagesDell Latitude 5410 14 Laptop White Papers En-UsFábio MaiaNo ratings yet

- 1Document5 pages1KarinaEvandraNo ratings yet

- 1150 DVOR Overheads Selex Rev - TRDocument125 pages1150 DVOR Overheads Selex Rev - TRdulli fitriantoNo ratings yet

- EMC VNX Series: Release 7.1Document154 pagesEMC VNX Series: Release 7.1Hernan RaviolNo ratings yet

- Dell Optiplex 270 SpecsDocument5 pagesDell Optiplex 270 Specsonly1str8No ratings yet

- Encapsulation WorksheetDocument2 pagesEncapsulation Worksheetks.ashwiniNo ratings yet

- HEWM Standalone Watermark Inserter Deployment GuideDocument54 pagesHEWM Standalone Watermark Inserter Deployment GuidePartha Sarathi RoyNo ratings yet

- Getting Started With Experion Software GuideDocument28 pagesGetting Started With Experion Software Guidebeerman81No ratings yet

- Series 90-30 System Manual For Windows UsersDocument116 pagesSeries 90-30 System Manual For Windows UsersErik GonzalezNo ratings yet

- Applikationen & Tools: FETCH/WRITE Service in An S7-300/400 CPU Via The Integrated Ethernet InterfaceDocument71 pagesApplikationen & Tools: FETCH/WRITE Service in An S7-300/400 CPU Via The Integrated Ethernet InterfaceRouma MansouriNo ratings yet

- A en GB - System 800xa Course GB850 PCDeviceLib SV5Document2 pagesA en GB - System 800xa Course GB850 PCDeviceLib SV5vantaipcNo ratings yet

- CMOS VLSI DESIGN NOTES Made by Barun Dhiman From Various Books Like Kamran Neil E WasteDocument226 pagesCMOS VLSI DESIGN NOTES Made by Barun Dhiman From Various Books Like Kamran Neil E WasteBarun DhimanNo ratings yet

- Vehicle Tracker Command ListDocument19 pagesVehicle Tracker Command ListAhmed YousryNo ratings yet

- Arl-500 Installation & Operation Manual v18Document79 pagesArl-500 Installation & Operation Manual v18paul5791100% (2)

- The Tenna Dipper A Poor Mans Antenna Analyzer CompressDocument39 pagesThe Tenna Dipper A Poor Mans Antenna Analyzer CompressRatinho LimaNo ratings yet

- Zener DiodeDocument14 pagesZener DiodeTanya SoodNo ratings yet

- CIS Module 1 - Journey To The CloudDocument12 pagesCIS Module 1 - Journey To The CloudSenthil RNo ratings yet

- Workflow ManagerDocument64 pagesWorkflow ManagerAbhy SinghNo ratings yet

- Silo - Tips - Clearcase Vob Database Troubleshooting Carem Bennett Ccna Mcse NT CipDocument7 pagesSilo - Tips - Clearcase Vob Database Troubleshooting Carem Bennett Ccna Mcse NT CippradeepyaNo ratings yet

- 110 MSPS/140 MSPS Analog Interface For Flat Panel Displays: R R Clamp 8 A/DDocument28 pages110 MSPS/140 MSPS Analog Interface For Flat Panel Displays: R R Clamp 8 A/DLuis Angel PNo ratings yet

- Project Management System in ITDocument4 pagesProject Management System in ITmuthuprakash123No ratings yet

- Multivector&SIMD Computers Ch8Document12 pagesMultivector&SIMD Computers Ch8Charu DhingraNo ratings yet