Professional Documents

Culture Documents

Electronics Design Mosfet Exercises

Uploaded by

bhanuCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electronics Design Mosfet Exercises

Uploaded by

bhanuCopyright:

Available Formats

Electronic design II

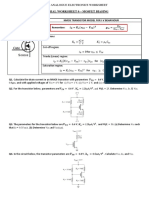

Exercise 1.

MOS – transistor and current mirror

Example:

E1. Draw a drain current of NMOS transistor as a function of drain source voltage

Vds when the gate source voltage (VGS) is 1.5 V and the size of the transistor is

W/L = 10um/1um. Explain also different region of the operation. Derive also

equation for small signal transconductance of the NMOS at above bias condition

in active region.

E2. Draw the small-signal model of the NMOS-transistor, when UD = 3 V,

UG = 2.5 V, US = 0.6 V, UB = 0 V ja W/L = 30 m / 2 m.

E3. Prove that the output current of the current mirror is equal to the input current

when sizes of the both transistors are same as shown in Fig. 1. Calculate also

the input impedance of the diode connected transistor M1 (input transistor in

Fig. 1).

Fig. 1. Current mirror.

E4. Calculate the output resistance of the MOS - cascode current mirror. The current

mirror have been biased on the active region. Iin = 0.1 mA and the width and

length of the transistors are W1 = W2 = W3 = W4 = 100 m ja L1 = L2 = L3 = L4

= 10 m. You do not need to take into account the body effect. In addition you

can assume that the gates of the M1 and M2 are low ohmic nodes.

Fig. 2 Cascode current mirror.

Electronic design II 9/3/20 1

E5. In Fig.3 the cascode current mirror with a wide dynamic range is presented. Size

the W/L of the transistors Q1-Q5 and a bias current Ibias so that

Vds3=Vds2=Veff+0.1V, when Veff is selected to be 0.2 V for all transistors

except Q5. The length of the transistors are L=2 µm and wanted Iout is 20 µA

and n=1. You can neglect the body effect. Here Vtn=0.8 V.

Fig.3 Cascode current mirror with a wide dynamic range.

Tasks to be calculated:

H1. Derive an equation for a small signal rds of the NMOS in an active region.

H2. Give the small signal model of the NMOS - transistor, when UD = 2.6 V,

UG = 2.5 V, US = 1 V, UB = 0 V ja W/L = 30m / 1.5m. (gm=480S, gs=95S,

rds=238k, Cgs=74fF, Cgd=17fF, Cgb=0fF)

H3. Prove that triode region equation is equal to active region equation when VDS

= VDS_SAT = Veff. Equations are below.

1 𝑊

𝐼𝑑 ≈ 2 ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ (𝑉𝐺𝑆 − 𝑉𝑡𝑛 )2 Activ region

𝐿

2

𝑊 𝑉𝐷𝑆

𝐼𝑑 ≈ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ [(𝑉𝐺𝑆 − 𝑉𝑡𝑛 ) ∙ 𝑉𝐷𝑆 − ] triode region, more accurate equa-

𝐿 2

tion

H4. Define the following quantities for the circuit shown in Fig. 4.

a) Magnitude of Iout (300 uA)

b) The DC-voltage Vin that is caused by Iin (Vin ~ 1,147V)

c) Input resistance ( Rin ~ 0.737k)

d) Output resestance ( Rout ~ 16.7k)

e) Minimum output voltage (Vout, min ~ 147mV)

f) The AC current signal of 1 uA is conducted at the input of the current mirror.

What kind of voltage signal you see at the input?

g) Small AC-voltage signal of 50 mV is connected at the output. What kind of

current signal you see at the output?

Iin = 100A, L(M1) =L(M2)= 0.5m, W(M1) = 50 m ja W(M2) = 150 m

Electronic design II 9/3/20 2

I in I out

Vi n Vo ut

Fig. 4. CMOS-current mirror.

H5. Give an estimate for the following quantities of the current mirror shown in Fig

5.

a) Output impedance (~ 6.6M)

b) Maximum value of the output voltage (~ 3.4V)

Vdd=4V, Ibias=10A, L1=L2=1m, W1=W2=100m, RDG=50k.

Fig. 7. CMOS-current with source degeneration.

Answers to the examples

E1. To calculate the drain current of the NMOS transistor at different regions below

equations can be used:

1 𝑊

𝐼𝑑 ≈ 2 ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ (𝑉𝐺𝑆 − 𝑉𝑡𝑛 )2 ∙ (1 + 𝜆 ∙ (𝑉𝐷𝑆 − 𝑉𝑒𝑓𝑓 )) Active region

𝐿

𝑊

𝐼𝑑 ≈ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ (𝑉𝐺𝑆 − 𝑉𝑡𝑛 ) ∙ 𝑉𝐷𝑆 triode region with small VDS

𝐿

Now by using above equations we can draw Id as a function of VDS. The border value

between the operation regions is VDS_sat or Veff which can be calculated to be VGS –

Vtn=1.5 V- 1 V=0.5 V in this case. So first equation have to be used when VDS≥0.5 V

and second one when VDS<<0.5 V. Actually there is third equation which approximate

current near the VDS_sat shown below. However two above equations are the most im-

portant ones.

2

𝑊 𝑉𝐷𝑆

𝐼𝑑 ≈ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ [(𝑉𝐺𝑆 − 𝑉𝑡𝑛 ) ∙ 𝑉𝐷𝑆 − ]

𝐿 2

Electronic design II 9/3/20 3

For example, Vds values: {0.05, 0.1, 0.2, 0.5, 1, 2} can be used. Now three first values

are in triode region and three last in active region. Inserting values to equations we get,

for example, at 0.05 V and 1 V

10𝜇

𝐼𝑑 ≈ 92𝜇 ∙ ∙ (1.5 − 1) ∙ 0.05 = 23𝜇𝐴

1𝜇

1 10𝜇

𝐼𝑑 ≈ ∙ 92𝜇 ∙ ∙ (1.5 − 1)2 ∙ (1 + 0.1 ∙ (1 − 0.5)) = 121𝜇𝐴

2 1𝜇

Finally at other VDS we get figure below:

From the small signal point of view and in active region NMOS is voltage controlled

current source (current is almost constant at different VDS) which means that output

current (drain current) is adjusted by the gate source voltage. Thus the small signal

transconductance of the transistor is defined as ΔId/ΔVGS. Now the small signal trans-

conductance can be solved by differentiating the Id as a function of VGS. Now we can

also neglect the term 1+λ(Vds-Veff) in the first order approximation (which is enough

in hand calculations in many cases).

1 𝑊

𝐼𝑑 ≈ ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ (𝑉𝐺𝑆 − 𝑉𝑡𝑛 )2 (1)

2 𝐿

𝑑𝐼𝑑 𝑊

≈ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ (𝑉𝐺𝑆 − 𝑉𝑡𝑛 ) = 𝑔𝑚 (2)

𝑑𝑉𝐺𝑆 𝐿

Solving the 𝑉𝐺𝑆 − 𝑉𝑡𝑛 from equation (1) and inserting it to (2) we can form more fa-

miliar equation for gm:

1 𝑊

𝐼𝑑 ≈ ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ (𝑉𝐺𝑆 − 𝑉𝑡𝑛 )2

2 𝐿

2 ∙ 𝐼𝑑

𝑉𝐺𝑆 − 𝑉𝑡𝑛 = √

𝑊

𝜇𝑛 𝐶𝑜𝑥 𝐿

Electronic design II 9/3/20 4

Inserting above to (2)

𝑊 2 ∙ 𝐼𝑑 𝑊 2 2 ∙ 𝐼𝑑 𝑊

𝑔𝑚 = 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ (√ ) = √(𝜇𝑛 𝐶𝑜𝑥 ∙ ) ∙ = √2𝐼𝑑 𝜇𝑛 𝐶𝑜𝑥 ∙

𝐿 𝑊 𝐿 𝑊 𝐿

𝜇𝑛 𝐶𝑜𝑥 𝐿 𝜇𝑛 𝐶𝑜𝑥 𝐿

𝑊

𝑔𝑚 = √2 ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙𝐼

𝐿 𝐷

E2. Small-signal model of the NMOS, UD = 3 V, UG = 2.5 V, US = 0.6 V, UB = 0 V

and W/L = 30 m / 2 m.

Values of the used parameter 2F (PHI in table), (GAMMA) Cox, CJ, MJ CJSW,

MJSW, PB and DL can be found in table (process_para_eng) in Moodle.

VT = VTo + ( 2 F + VSB – 2 F )

VT = 1 + 0,5( 0,6 + 0 6 – 0,6 ) 1,16V

Check that transistor is active region

UGS – V T = 1,9V – 1,16V = 0,74V UDS = 2 4V

So the NMOS is active region.

Current Id

1 𝑊

∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ (𝑉𝐺𝑆 − 𝑉𝑡𝑛 )2 ∙ (1 + 𝜆 ∙ (𝑉𝐷𝑆 − 𝑉𝑒𝑓𝑓 ))

𝐼𝑑 ≈

2 𝐿

The value of the parameter (LAMBDA) depends on the channel lenght L according

to the equation = Const / L . In this specific process NMOS = 0.1*10-6/L and

PMOS=0.2*10-6/L. Parameter has also more accurate equation which takes into ac-

count values of the Vds and Veff . Now we use equation =Const/L.

Electronic design II 9/3/20 5

1 30

𝐼𝑑 ≈ ∙ 92𝜇 ∙ ∙ (1.9 − 1,16)2 ∙ (1 + 0,05 ∙ (2,4 − 0,74)) = 409 𝜇𝐴

2 2

Transconductance

𝑊

𝑔𝑚 = √2 ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ ∙ 𝐼 = 1,06 𝑚𝑆

𝐿 𝐷

𝛾 0,5

𝑔𝑠 = 𝑔𝑚 ∙ = 1,06𝑚 ∙ = 244𝜇𝑆

2 ∙ √2 ∙ |𝜙𝐹 | + 𝑉𝑆𝐵 2 ∙ √0,6 + 0,6

Output resistance

1

𝑟𝑑𝑠 = = 48,9 𝑘𝛺

𝜆 ∙ 𝐼𝑑

Capacitances

gate cap. G gateoverlap

S D

sidewall

bottom

L

W

S G D

4m

L

2

Cgs = --- WLC ox + W LC ox

3

L is the LD in parameter table, which is for both N/PMOS 300nm.

C gs = --- ( 30 10 ) 2 10 + 30 10 0,310 1,9 10

2 –6 –6 –6 –6 –3

3

Cgs 93 1 fF

Cgd = W LCox 17 1fF

Cgb 0

Electronic design II 9/3/20 6

CJ CJSW

Csb = ( AS + WL ) ----------------------------

MJ

- + PS -----------------------------------

MJSW

-

V

1 + -------- sb V

1 + -------- sb

PB PB

To evaluate the value of the capacitance we have to first calculate the area and the pe-

rimeter of the drain and source. Now we assume that drain and source area reach 4 m

beyound the gate area, see above picture. In that case AS and AD

2 –12 2

AS = AD = 30m 4m = 120 ( m ) = 120x10 m

Perimeters are

PS = PD = 30m + 4m + 4m = 38m

Note that sidewalls against gate are not included.

–3 –9

–12 –12 0,4 10 –6 0,4 10

Csb = ( 120 10 + 60 10 ) -----------------------------

- + 38 10 -----------------------------

-

1 + 0 6 0,5 0 6 0,1

--------- 1 + -------- -

0,8 0,8

= 54fF + 14fF = 68fF

CJ CJSW

Cdb = A D -----------------------------

MJ

- + PD -----------------------------------

-

1 + V db Vdb MJSW

-------- 1 + --------

PB PB

–3 –9

–12 0,4 10 –6 0,4 10

120 10 ---------------------------

0,5

- + 38 10 ---------------------------

-

1 + ------ 3 3 0,1

- 1 + ------ -

0,8 0,8

= 22fF + 13fF 35fF

small-signal model

Electronic design II 9/3/20 7

The small-signal model is used in small-signal AC-analysis. For every component the

DC-operating point and the values of the small-signal model in that specific DC-oper-

ating point is first calculated. The small-signal model of the whole design can be formed

by connecting the small-signal model of all components together. The designed circuit

small-signal model can be used to evaluate for example small-signal gain, output re-

sistance, input resistance and bandwidth etc.

Advantages:

• simple, can be used hand calculation

• easy to see how every components affects to the result

• fast in simulation

Disadvantages

• works only with small signals

• do not take account nonlinearitys

• do not take account slew rate

• do not take account supply voltages

What is the small-signal? When the voltage or current change caused by the signal is

much smaller than DC- voltage or current the signal can be intend to be small-signal.

For example see figure below where the small-signal model can be intend to behave

linearly in specific DC-operating point.

ID

id

ube

UBE

E3. Now we can write the equation of the current of the both transistor as:

1 𝑊1

𝐼𝑖𝑛 = ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ (𝑉 − 𝑉𝑡𝑛 )2

2 𝐿1 𝐺𝑆1

1 𝑊2

𝐼𝑜𝑢𝑡 = ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ (𝑉 − 𝑉𝑡𝑛 )2

2 𝐿2 𝐺𝑆2

Because both transistors have same VGS so VGS1= VGS2=Vin and the sizes are

same W1/L1 = W2/L2 we can write equation again:

1 𝑊1

𝐼𝑜𝑢𝑡 = ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ (𝑉 − 𝑉𝑡𝑛 )2

2 𝐿1 𝑖𝑛

Electronic design II 9/3/20 8

1 𝑊1

𝐼𝑖𝑛 = ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ (𝑉 − 𝑉𝑡𝑛 )2

2 𝐿1 𝑖𝑛

Now Iout is equal to Iin and also see that ratio of the currents is:

1 𝑊1

(𝑉 )2 𝑊1⁄

𝐼𝑖𝑛 2 ∙ 𝜇𝑛 𝐶𝑜𝑥 ∙ 𝐿1 𝑖𝑛 − 𝑉𝑡𝑛 𝐿1

= = , 𝑛𝑜𝑤 1

𝐼𝑜𝑢𝑡 1 𝑊1 (𝑉 2 𝑊2⁄

∙ 𝜇 𝐶 ∙ − 𝑉 ) 𝐿2

2 𝑛 𝑜𝑥 𝐿1 𝑖𝑛 𝑡𝑛

To solve any small-signal parameter, like an input impedance, the small-signal model

have to be drawn. After that the node equations can be solved. Now the small-signal

model for diode connected transistor can be drawn as shown below in a). To solve the

input impedance the test voltage vin have to be connected to input (Gate in this case)

which causes the test current iin to be driven towards input. Now the input impedance is

vin/ iin in fig b).

Now we can write the equation for currents in input node (note that now vgs = vin):

𝑖𝑖𝑛 = 𝑖𝑟𝑑𝑠 + 𝑔𝑚 ∙ 𝑣𝑖𝑛 , (1)

𝑣𝑖𝑛

𝑖𝑟𝑑𝑠 = , (2)

𝑟𝑑𝑠

Now inserting (2) to (1) we get:

𝑣𝑖𝑛

𝑖𝑖𝑛 = + 𝑔𝑚 ∙ 𝑣𝑖𝑛

𝑟𝑑𝑠

𝑣𝑖𝑛 1 1 1

= ≈ , 𝑔𝑚 ≫

𝑖𝑖𝑛 𝑔𝑚 + 1⁄𝑟 𝑔𝑚 𝑟𝑑𝑠

𝑑𝑠

E4. To make calculation easier we can assume that the gates of the M1 and M2 (diode

connected transistors) are low impedance points because input dc current source

is open circuit which means that the gates of the M3 and M4 are floating points.

Thus no current can flow through the resistance of the diode connected transistor

in small-signal point of view. The output resistance can be solved by applying a

Electronic design II 9/3/20 9

test voltage at the output and solving the vo/io = rout. First draw the small-signal

model of the current mirror.

Then write the nodal equations of the small-signal model

𝑣𝑠2 = 𝑖𝑜𝑢𝑡 ∙ 𝑟𝑑𝑠1 , (1)

𝑖𝑜𝑢𝑡 = 𝑖𝑑𝑠2 − 𝑔𝑚2 ∙ 𝑣𝑠2 , (2)

𝑣𝑜𝑢𝑡 − 𝑣𝑠2

𝑖𝑑𝑠2 = , (3)

𝑟𝑑𝑠2

Using above equations to solve vo/io = ro

Now inserting (1) and (3) to equation (2) we get:

𝑣𝑜𝑢𝑡 − 𝑣𝑠2

𝑖𝑜𝑢𝑡 = − 𝑔𝑚2 ∙ 𝑖𝑜𝑢𝑡 ∙ 𝑟𝑑𝑠1 , (4)

𝑟𝑑𝑠2

and then again inserting (1) to (4) we get:

Electronic design II 9/3/20 10

𝑣𝑜𝑢𝑡 − 𝑖𝑜𝑢𝑡 ∙ 𝑟𝑑𝑠1 𝑣𝑜𝑢𝑡 𝑖𝑜𝑢𝑡 ∙ 𝑟𝑑𝑠1

𝑖𝑜𝑢𝑡 = − 𝑔𝑚2 ∙ 𝑖𝑜𝑢𝑡 ∙ 𝑟𝑑𝑠1 = − − 𝑔𝑚2 ∙ 𝑖𝑜𝑢𝑡 ∙ 𝑟𝑑𝑠1

𝑟𝑑𝑠2 𝑟𝑑𝑠2 𝑟𝑑𝑠2

Then rearranging we get:

𝑖𝑜𝑢𝑡 ∙ 𝑟𝑑𝑠1 𝑣𝑜𝑢𝑡 𝑟𝑑𝑠1

𝑖𝑜𝑢𝑡 + + 𝑔𝑚2 ∙ 𝑖𝑜𝑢𝑡 ∙ 𝑟𝑑𝑠1 = = 𝑖𝑜𝑢𝑡 (1 + + 𝑔𝑚2 ∙ 𝑟𝑑𝑠1 )

𝑟𝑑𝑠2 𝑟𝑑𝑠2 𝑟𝑑𝑠2

𝑣𝑜𝑢𝑡 𝑟𝑑𝑠1

= 𝑟𝑑𝑠2 (1 + + 𝑔𝑚2 ∙ 𝑟𝑑𝑠1 ) = 𝑟𝑑𝑠2 + 𝑟𝑑𝑠1 + 𝑔𝑚2 ∙ 𝑟𝑑𝑠1 ∙ 𝑟𝑑𝑠2

𝑖𝑜𝑢𝑡 𝑟𝑑𝑠2

= 𝑟𝑑𝑠2 + 𝑟𝑑𝑠1 (1 + 𝑔𝑚2 ∙ 𝑟𝑑𝑠2 )

Approximately this is

𝑟𝑜𝑢𝑡 ≈ 𝑔𝑚2 ∙ 𝑟𝑑𝑠1 ∙ 𝑟𝑑𝑠2

because gm2*rds1*rds2>> rds1,rds2

Calculate rds1, rds2 and gm2.

1 1 W

r ds1 = -------------- = -------------- = rds2 g m2 = 2K pn ------2- ID2

1 I D1 2 ID2 L2

1 A

rds1 = ---------------------------------- = 1M g m2 = 2 92 -----2- 10 0,1mA = 0,43mS

0,1

----------- 0,1mA V

10

So the output resistance is

𝑟𝑜𝑢𝑡 ≈ 𝑔𝑚2 ∙ 𝑟𝑑𝑠1 ∙ 𝑟𝑑𝑠2 = 0.43 𝑚𝑆 ∙ 1𝑀𝛺 ∙ 1𝑀𝛺 = 430 𝑀𝛺

E5. Because n=1 the ratio of the (W/L1,2,3,4)/(W/L5) = 4. The output current is 20

µA in which case also the Iin is 20 µA and the effective voltage Veff=0.2 V for Q1,2,3,4.

Thus, the size of the transistor Q3 can be calculated by using the equation of the drain

current

W3 2 Id 2 20A

------- = -------------------------------2- = ------------------------------------ = 10

L3 K pn ( V eff3 ) A 2

100 ------2- ( 0,2V )

V

Now W/L of Q1,2,4 are also 10 in which case W/L5=2.5, because n=1.Now we can cal-

culate the Ibias=Id5 using drain current equation Ibias = Id5=0.5Kpn(W/L5)(Vgs5-Vtn)2.

Vgs5=is unknown so we have to the first calculate that by using

Vgs5 = Vds3 + Vgs4

Electronic design II 9/3/20 11

Veff3 was given and so thta Vds3=Veff3+0.1V=0.3V and Vgs4=Veff4+Vtn=0.2V+0.8V=1V.

Thus, Vgs5=0.3V+1V=1.3V and

1 𝜇𝐴

𝐼𝑏𝑖𝑎𝑠 = ∙ 100 ∙ 2 ∙ 2.5 ∙ (1.3𝑉 − 0.8𝑉)2 = 31.25𝜇𝐴

2 𝑉

Electronic design II 9/3/20 12

You might also like

- Electronics design II amplifier calculationsDocument14 pagesElectronics design II amplifier calculationsbhanuNo ratings yet

- Experiment No. 1: ObjectiveDocument9 pagesExperiment No. 1: ObjectiveNitin RajputNo ratings yet

- Matching Analysis and Design of Low Offset AmplifiersDocument21 pagesMatching Analysis and Design of Low Offset Amplifiersprabhat_premNo ratings yet

- EECE2412 Final Exam: With SolutionsDocument15 pagesEECE2412 Final Exam: With Solutionsአንድነት togetherNo ratings yet

- Chapter 2: Diode Applications: 2.1 Half Wave RectifiersDocument27 pagesChapter 2: Diode Applications: 2.1 Half Wave Rectifiersahmed adnanNo ratings yet

- Analog Circuit Design Notes-3Document22 pagesAnalog Circuit Design Notes-3itsnirosNo ratings yet

- Lec 8 5 8 6BJT-Differential AmplifierDocument105 pagesLec 8 5 8 6BJT-Differential AmplifierRakhmeen gulNo ratings yet

- ECE-438 MOS Transistor Circuit AnalysisDocument10 pagesECE-438 MOS Transistor Circuit Analysisneeno2013No ratings yet

- Questions On Small Signal Model of AmpDocument2 pagesQuestions On Small Signal Model of AmpdevsrivastavaNo ratings yet

- Solns 2cmosDocument18 pagesSolns 2cmosramprakash_rampelliNo ratings yet

- Chap.3 and Chap.4平時考解答Document10 pagesChap.3 and Chap.4平時考解答邱宇琳No ratings yet

- MOS Differential Pair Homework ProblemsDocument7 pagesMOS Differential Pair Homework ProblemsApricot BlueberryNo ratings yet

- Assignment 02Document3 pagesAssignment 02Anchal Debnath ee21b017No ratings yet

- Experiment 1Document6 pagesExperiment 1Enes AyduranNo ratings yet

- 6 Es2c0 Tutorial Worksheet 6 Mosfet BiasingDocument2 pages6 Es2c0 Tutorial Worksheet 6 Mosfet BiasingNamita GeraNo ratings yet

- Lab 8 ReportDocument6 pagesLab 8 Reportapi-491291595No ratings yet

- ECE 453 Homework 1: RLC circuits and transistor circuitsDocument5 pagesECE 453 Homework 1: RLC circuits and transistor circuitsBrimwoodboyNo ratings yet

- ENEE 3543 - Homework 4 - SolutionsDocument4 pagesENEE 3543 - Homework 4 - SolutionsTSwayNo ratings yet

- (ELECS2) Exp2 - Compound ConfigurationsDocument15 pages(ELECS2) Exp2 - Compound ConfigurationsFrodolfre Reginald LazoNo ratings yet

- TUGAS ELEKTRONIKA - Kelompok 2Document10 pagesTUGAS ELEKTRONIKA - Kelompok 2Christine SibaraniNo ratings yet

- Short Test 1 Solutions - S1 2023Document5 pagesShort Test 1 Solutions - S1 2023nayasisereiNo ratings yet

- Lesson Inverters 04 PDFDocument49 pagesLesson Inverters 04 PDFlunesNo ratings yet

- CMOS Inverter Characteristics Lab ReportDocument8 pagesCMOS Inverter Characteristics Lab ReportabhiNo ratings yet

- Inductor and Transformer Design: Problem 1Document14 pagesInductor and Transformer Design: Problem 1hans_alayoNo ratings yet

- Chapter 2 MOS Transistor TheoryDocument25 pagesChapter 2 MOS Transistor TheoryrasheeenNo ratings yet

- Analysis and Design of Digital Integrated CircuitsDocument14 pagesAnalysis and Design of Digital Integrated CircuitsfjwoemcuNo ratings yet

- Autriz. Merin. Punongbayan. Fet and Op AmpDocument20 pagesAutriz. Merin. Punongbayan. Fet and Op AmpRenjelle Mae AutrizNo ratings yet

- CMOS Analog Design Gain and Noise AnalysisDocument6 pagesCMOS Analog Design Gain and Noise AnalysisAnish BennyNo ratings yet

- Differential Pair Using MOS TransistorsDocument5 pagesDifferential Pair Using MOS TransistorsSatish BojjawarNo ratings yet

- 2 in One LabDocument5 pages2 in One LabEnock KachokolaNo ratings yet

- EC410 Fall 2012 FinalDocument8 pagesEC410 Fall 2012 FinalRabee Adil JamshedNo ratings yet

- Mohit Jetani 1270404 0Document32 pagesMohit Jetani 1270404 0ronajoj120No ratings yet

- Design of CMOS OpAmp For A D/A Converter Buffer by Manraj Singh GujralDocument22 pagesDesign of CMOS OpAmp For A D/A Converter Buffer by Manraj Singh GujralManraj GujralNo ratings yet

- Current Sources and Sinks: V V V V V V VDocument7 pagesCurrent Sources and Sinks: V V V V V V VSyed HyderNo ratings yet

- Diodes, Home Work Solutions: 3.1 Problem 3.11Document13 pagesDiodes, Home Work Solutions: 3.1 Problem 3.11Sherweet A. AlsaadanyNo ratings yet

- Bias Circuits: Kanazawa University Microelectronics Research Lab. Akio KitagawaDocument22 pagesBias Circuits: Kanazawa University Microelectronics Research Lab. Akio Kitagawapani256No ratings yet

- Circuit Theory - Solved Assignments - Semester Fall 2007Document30 pagesCircuit Theory - Solved Assignments - Semester Fall 2007Muhammad UmairNo ratings yet

- Sol 1Document25 pagesSol 1Kyoung Su Lee0% (1)

- Electronics Past Test Questions and MemoDocument22 pagesElectronics Past Test Questions and MemoPrevin BogopaNo ratings yet

- Full-Wave Controlled Rectifier With Resistive LoadDocument4 pagesFull-Wave Controlled Rectifier With Resistive Loadhamza abdo mohamoudNo ratings yet

- BJT Amplifiers Problems & SolutionsDocument14 pagesBJT Amplifiers Problems & SolutionsThiện Nguyễn100% (5)

- Unit Ii: Problem 2.1: in The Circuit of Natural Commutation, The Turn-Off Time (TDocument27 pagesUnit Ii: Problem 2.1: in The Circuit of Natural Commutation, The Turn-Off Time (TAnisa FathimaNo ratings yet

- Modeling the Semiconductor Diode Forward CharacteristicDocument22 pagesModeling the Semiconductor Diode Forward CharacteristicSujata DahalNo ratings yet

- Zero and Span CircuitsDocument2 pagesZero and Span CircuitsMourougapragash Subramanian100% (1)

- Homework #4: I I V VDocument7 pagesHomework #4: I I V Vtay ChantsNo ratings yet

- 08ece Ee331 Group 6 Le Van Hai Lab3Document19 pages08ece Ee331 Group 6 Le Van Hai Lab3Quốc HiếuNo ratings yet

- Sheet 3 - SolutionDocument10 pagesSheet 3 - SolutionMajid HelmyNo ratings yet

- Chapter 2 Part 2 EEE411 DR Yusnita PDFDocument60 pagesChapter 2 Part 2 EEE411 DR Yusnita PDFCaha yANo ratings yet

- Chapter03 ExDocument10 pagesChapter03 ExKarthikeya VemparalaNo ratings yet

- UNSW Sydney Australia: Question DA1Document18 pagesUNSW Sydney Australia: Question DA1Marquee BrandNo ratings yet

- Homework 3 - SolutionsDocument14 pagesHomework 3 - SolutionsYahya Salam SalehNo ratings yet

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Electronics 3 Checkbook: The Checkbooks SeriesFrom EverandElectronics 3 Checkbook: The Checkbooks SeriesRating: 5 out of 5 stars5/5 (1)

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- NMOS transistor rds derivation using active region equationDocument10 pagesNMOS transistor rds derivation using active region equationbhanuNo ratings yet

- Electronics design II frequency responseDocument8 pagesElectronics design II frequency responsebhanuNo ratings yet

- Answers 4 2020Document7 pagesAnswers 4 2020bhanuNo ratings yet

- JVVD UniversitiesDocument6 pagesJVVD UniversitiesbhanuNo ratings yet

- 2.1 Function BasicsDocument50 pages2.1 Function BasicsbhanuNo ratings yet

- SpecificationsDocument4 pagesSpecificationsBawantha Prasad MihirangaNo ratings yet

- Cinchoo ETL - Parquet Writer - CodeProjectDocument35 pagesCinchoo ETL - Parquet Writer - CodeProjectgfgomesNo ratings yet

- SRX SFP 10ge Dac 1MDocument7 pagesSRX SFP 10ge Dac 1MAssem SamirNo ratings yet

- Manual Horno 3DDocument11 pagesManual Horno 3DJose ZuñigaNo ratings yet

- Employee Payroll System ProjectDocument21 pagesEmployee Payroll System ProjectZeeshan Hyder BhattiNo ratings yet

- Schwartz Space and Fourier AnalysisDocument10 pagesSchwartz Space and Fourier AnalysiseducatedyaserNo ratings yet

- Research Proposal: Factors Effecting Online Education Among University Students of Bangladesh During Covid-19Document14 pagesResearch Proposal: Factors Effecting Online Education Among University Students of Bangladesh During Covid-19Mohaiminul IslamNo ratings yet

- JT-11-DMCF: Line Output TransformerDocument2 pagesJT-11-DMCF: Line Output TransformerLuis Otavio TrindadeNo ratings yet

- Level 11 Pin Relays Catalog PageDocument12 pagesLevel 11 Pin Relays Catalog PageRicardo RosárioNo ratings yet

- SQLPlus Concurrent Program in Oracle AppsDocument5 pagesSQLPlus Concurrent Program in Oracle AppsTikendra Kumar PalNo ratings yet

- Resume - Game DevelopmentDocument1 pageResume - Game Developmentapi-498982826No ratings yet

- Linear-Strain Triangle Equations ChapterDocument26 pagesLinear-Strain Triangle Equations ChapterFábio1 GamaNo ratings yet

- Mrs J's Resource Creations ©Document7 pagesMrs J's Resource Creations ©syddysNo ratings yet

- Perspective, Secne Design, and Basic AnimationDocument17 pagesPerspective, Secne Design, and Basic AnimationShehnaz ObeidatNo ratings yet

- Computer (Dempo Group)Document9 pagesComputer (Dempo Group)Kenichi Okta HerwantoNo ratings yet

- Cyber Hunter Installation Log Documents File Installation ProcessDocument18 pagesCyber Hunter Installation Log Documents File Installation ProcessGregory JNo ratings yet

- Cgo San Jose Nueva Ecija-Administrative Aide III Utility Worker IIDocument1 pageCgo San Jose Nueva Ecija-Administrative Aide III Utility Worker IIWarren Del RosarioNo ratings yet

- Advanced Isometric Configuration in AutoCADPlant3DDocument49 pagesAdvanced Isometric Configuration in AutoCADPlant3DRoobens SC Lara100% (1)

- The in Uence of The Building Shape On The Costs of Its ConstructionDocument14 pagesThe in Uence of The Building Shape On The Costs of Its ConstructionCornelius TapiwaNo ratings yet

- Cryptography - Lucee DocumentationDocument2 pagesCryptography - Lucee Documentationrangel.sardinhaNo ratings yet

- AIRPORTS AUTHORITY OF INDIA I CardDocument2 pagesAIRPORTS AUTHORITY OF INDIA I Cardkallul5551350100% (1)

- Flange Leakag PEQ Allowable StressDocument1 pageFlange Leakag PEQ Allowable Stressazhagu duraiNo ratings yet

- Organizational Theory Quiz 1Document1 pageOrganizational Theory Quiz 1Shabana NaveedNo ratings yet

- Bess-Sm-3q90041-Qams-003 Method of Statement - Cable Termination PDFDocument5 pagesBess-Sm-3q90041-Qams-003 Method of Statement - Cable Termination PDFChristian BulaongNo ratings yet

- Eduwork: Free Class Web ProgrammingDocument53 pagesEduwork: Free Class Web ProgrammingAgnesNo ratings yet

- EFI FLash Tool - HowToDocument15 pagesEFI FLash Tool - HowToJasonNo ratings yet

- 18CSC207J APP Lab ManualDocument89 pages18CSC207J APP Lab Manualshivani sankarNo ratings yet

- A Project Report On Knowledge ManagementDocument6 pagesA Project Report On Knowledge ManagementBharati KudambalNo ratings yet

- Foss Lab Manual FinalDocument75 pagesFoss Lab Manual FinalBalraj ENo ratings yet

- BTECDocument11 pagesBTECRini SandeepNo ratings yet