Professional Documents

Culture Documents

In Out

In Out

Uploaded by

Manuel CasanovaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

In Out

In Out

Uploaded by

Manuel CasanovaCopyright:

Available Formats

Basic course I/O bus 1-1

Contents

Figures

Contents list

Introduction 3

Physical lay-out of the microscope 5

General block diagram 7

I/O Bus principles 24

General info on I/O bus 25

Put routine 26

Get routine 28

Load Dac routine 30

Examples of comon used electrical diagrams 31

I/O Boards 37

Switching on 44

Contents

Figures

H

H

Fig. 1 Basic course I/O bus 1-1

Basic course I/O bus 1-2

Contents

Figures

List of Illustrations

Fig. Title Page

1 Motherboard connections ............................................... 4

2 Physical lay-out of microscope ...................................... 6

3 Multi bus and support boards .......................................... 8

4 SBC Block diagram ........................................................... 9

5 SDB Block diagram ......................................................... 10

6 PFD block diagram .......................................................... 11

7 MMB Jumper settings ..................................................... 18

8 Vacuum sytem block diagram ........................................ 20

9 HT block diagram ............................................................ 21

10 Camera sytem block diagram ........................................ 22

11 Lenses block diagram .................................................... 23

12 Put routine timing diagram ............................................. 27

13 Get routine timing diagram ............................................ 29

14 Address selection example ............................................ 32

15 Interrupt procedure example ......................................... 33

16 Overview diagram puts and gets .................................. 34

17 Load DAC example .......................................................... 35

18 DAC AD7542 block diagram ........................................... 36

19 Input output block diagram ............................................ 38

20 Input output block diagram (detailed) ........................... 39

21 Multiple output board block diagram ............................ 40

22 Multiple input board block diagram ............................... 41

23 Push button interface block diagram ............................ 42

24 Panel coder interface block diagram ............................. 43

25 Switching on circuit old ................................................. 45

Contents

Figures

H

H 26 Switching on circuit new ............................................... 46

Basic course I/O bus 1-2

Basic course I/O bus 1-3

Contents

Figures

1.1 Introduction

• HOW TO USE THE MANUALS

• VOLUME 1

– BLOCKDIAGRAM

– FUNCTIONAL SETUP

• VOLUME 2 + 3

– CIRCUIT DIAGRAMS

– ALPHABETIC SETUP

• Mechanical

– top to bottom

– at the end the vacuum system (parts not in column)

Contents

Figures

H

H

Basic course I/O bus 1-3

Fig. 1 Motherboard connections Basic course I/O bus 1-4

Contents

Figures

FLAT CABLE

+

CONNECTOR

MOTHER BOARD MBCL MBCL - X5 - 101

MBCL - X5 - 301

(X)1 - 301 MBCL - X5A

(X)1 - 101

BOARD

X1

Rear connectors

X2

X6 D connector MBCL - X25 - 332

Front connectors MBCL - X25 - 132

(X)2 - 332

BNC

(X)2 - 132 EM4639A

X5

Contents

Figures

H

H

Basic course I/O bus 1-4

Basic course I/O bus 1-5

Contents

Figures

1.2 Physical lay-out of the microscope

Contents

Figures

H

H

Basic course I/O bus 1-5

Fig. 2 Physical lay-out of microscope Basic course I/O bus 1-6

Contents

Figures

PANEL HT TANK

24VRS

LIGHT POWER UNIT Sect. 3.18 CM100/120

H / UNIT

Sect. 3.24

POWER SUPPLIES

+24V ± 15V +5V ONLY ELECTRONICS

HT RACK

IGP SUPPLY

LENS SUPPLY 56V or 75V

-M

- M U UN HT ELECTRONICS

- M A RA IT S

- PUMPING SYSTEM - M B RA CK Sect. 3

WATER CONNECTIONS - WATER CONNECTIONS Fig. MS MS UNIT Fig. 440 - M BB R CK S ect. .17

- PNEUM. CONNECTION 441 Sect. 3.14, 3.16 - M BCL ACK ect. 3.7

- N2 CONNECTION - P DEL + R S Sect 3.8

- S .S.P. + R S ect. . 3.9

ER ect 3.10

IAL . 3.

L.H. CONSOLE Sect. 3.5 VDB C.B CO 12 + 3.1

MD . NN +3 1

COLUMN Sect. 3.22 EC .13

SOLID STATE T TIO +F

SUPPORT +15 XA NK ig.

PRE-AMP CSP V CP IT a 440

S Fig. 441 Sect. 3.2 -15 Fig cc.

BRIGHT FIELD +24 V ST . 44

SCA C EM 0

SCREEN CURRENT A +5V V CO

AMPLIFIER Sect. 3.5.2 SOLID STATE NN

EDAX CR .

PRE-AMP Se T P.S

BSD Sect. 3.5.1 Fig ct. 3.1 .P.

DA . 45

TA 0 HR

MO DISP M

L.H. PANEL Sect. 3.6 NIT LA

OR Y HIG

RE H

PH SOL

SED PLATE VS MO OTO UTIO

NUMBER 3.3 Se S Sec NITO N

ct.

3.2 t. 3 R

. R.H 3 .4

L.H MO .

R

TO TO

MO BSD R R.H AC SR

X Y

. PA CE S

. acc NE SS

acc . LS OR

Y

AU ect

LE OT . 3.

V E 21

Se

ct. LLING

3.3

(CM

300

onl

y) -M

E

- BRIGHT FIELD DETECTOR (STEM) - P AS U R

OW I

- DARK FIELD DETECTOR (STEM) + 4 ER N G U

- PEELS (ACC.) -K x P BO N IT

- TV (ACC.) E YB O W OS Se

OA E R B TE R ct .

- NEAR AXIS DETECTOR CM200/300 (ACC.) 3

RD O O H E A .1 5

Hierna toevoegen fig 440 CO

NN

ST

EC

ER T S IN

D K

TO P B S

RB e

O A ct. 3 .

Contents

EM6451A RD 19 F ig

Figures

ac c . 44

. 3

H

H

Basic course I/O bus 1-6

Basic course I/O bus 1-7

Contents

Figures

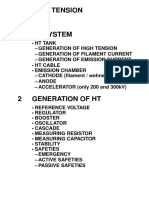

1.3 GENERAL BLOCK DIAGRAM

• MULTIBUS

• SBC - RCB - MMB

• SUPPORT BOARDS: SDB, PFD

• SOFTWARE ASPECTS

– START-UP PROCEDURE

– RAM INIT

– SOFTWARE MESSAGE NUMBERS

– JUMPER SETTINGS

• VACUUM

• HT

• CAMERA

• LENSES

•

• Hier toevoegen de funties van de sdb en RCB

Contents

Figures

H

H

Basic course I/O bus 1-7

Fig. 3Multi bus and support boards Basic course I/O bus 1-8

Contents

Figures

H

INTEL MULTI BUS

+5V -5V +12V -12V

MBB REMOTE

POWER CONTROL

BUFFER

(OPTION)

or

one

serial MEMORY

option

MOTHER BOARD

BUS MMB X2

TRANSLATER +5V +15V -15V

RAM COMBI QUAD SERIAL PORT

SINGLE J2 (OPTIONAL)

STEM BUS STEM BUS X4 BOARD COMPUTER RAM

OPTO MBB X6 32K/64 k

COUPLER BOARD

SERIAL 1

MMB X1 J1

MDER - X1 PRINTER ROM

START-UP

N.V. RAM MBB X1 SERIAL 2 128/256/512/ k

PROMS

16 k RESTART KEYBOARD J2

ROM

SBC337 SERIAL 3 128/256512 k

8087 J3

SRS

VIDEO RAM ROM

2k SERIAL 4 128/256/512 k

J4

Not used

BUS INTER.

MATRIX PAR 1 ADDRESS

TRANSLATER J5 PROM

(not used)

POWER FAIL

TEM BUS OPTO TEM BUS X3 ACL0

LOGIC

COUPLER

MBCR - X4

TELETEXT CIRCUIT

X5 The address prom has 4 positions for

4 address maps:

W7= 32K RAM with 128 K ROM

W8= 64K RAM with 256 K ROM

IO RESET W8= 64K RAM with TESTSW

TO ALL W9= 64K RAM with 512 K ROM

I/0 BOARDS POWER UNIT

None = 64K RAM with 256 K RAM

A13 ACSNS ACL0

POWER FAIL

DETECTION

SYSTEM * MAINS PANEL

DEFINITION

BOARD

KEY

MBCL - X15

* 4 JUMPER BYTES

RESTART MBCR - X1

EM4356-1F

Contents

Figures

Basic course I/O bus 1-8

Fig. 4SBC Block diagram Basic course I/O bus 1-9

Contents

Figures

24 PARALLEL CONTROL SERIAL SBX

I/O LINES INTERFACE DEVICES MULTIMODULES

BOARDS

SBC85/10/50

SINGLE COMPUTER BOARD

DRIVER MMB X1 RS 232 SBX SBX

TERMINATOR INTERFACE MULTIMODULES MULTIMODULES

INTERFACE CONNECTOR CONNECTOR

POWER FAIL

INTERRUPT

MATRIX

(JUMPERS)

PROGRAMMABLE TWO PROGRAMMABLE SERIAL PROGRAMMABLE

PERIPHERAL PROGRAMMABLE INTERRUPT INTERFACE BAUDRATE

INTERFACE TIMERS CONTROLLER (USART) GENERATOR

(8255A) (2/3 8254A) (8259A) (8251A) (1/3 8254A)

ON BOARD LOCAL BUS

8K BYTES RAM 64K BYTES IAPX86/10 MULTIBUS

(4 x 2160) EPROM/ROM (8086-2) MULTIMASTER

SOCKETS CPU INTERFACE

(4 x 28 PINS)

8K BYTES RAM 64K BYTES SBC337

SBC382 EPROM/ROM NUMMERIC

(4 x 2165) SOCKETS DATA

SBC341 PROCESSOR

(4 x 28 PINS) (8087)

Contents

MULTIBUS SYSTEM BUS

Figures

H

H

Basic course I/O bus 1-9

Fig. 5SDB Block diagram Basic course I/O bus 1-10

Contents

Figures

SDB MDCL X15

ADDRESS &

LATCH

CRDSL

RDDAT

LATCH

Key BUFFER

BUFFER Customer

Service

Factoy

FAS

BCD

DECI-

MAL

A B C D Tri-STATE

BUFFER

SDB board list of jumpers

Contents

Figures

H

H

Basic course I/O bus 1-10

Fig. 6PFD block diagram Basic course I/O bus 1-11

Contents

Figures

PFD MBCR-X1

ONE SHOT

Level

detector

12msec

ACLO

Via RCB to SBC

Missing PULS

detector

RESET

From P/A13 ACSNS

Transformer

ODP status 15sec delay

To MIB

from ODP

Transformer

Contents

Figures

H

H

Basic course I/O bus 1-11

Basic course I/O bus 1-12

Contents

Figures

H Flowchart start-up procedure for CM control software version up to 10

1 ON BOARD ROM CHECK CPU BOARD CHECK SUM

2 VIDEO RAM TEST TEST FOR BLANKS

* Note: JUMPER ON RCB

3 NON-VOLATILE RAM TEST SAVE, WRITE/READ/COMP.,

RESTORE

4 DATA RAM TEST MMB RAM (32K)

5 MMB ROM CHECK CHECK SUM PER ROM PAIR

6 BUS INITIALIZATION SETS BUS PORTS FOR USE

7 DETERMINE HARDWARE CONFIG. CHECK SDB BOARD

8 BATTERY CHECK CHECK BATTERY FOR NV RAM

9 CHECK FOR DEFAULT RAM INIT. VIA SOFTKEY OR VIA JUMPER SDB-D2

10 READ/CHECK SOLID STATE KEY IN CASE OF RAM INIT SOLID

STATE KEY IS WRITTEN INTO RAM

11 INIT DATA RAM DURING NORMAL START UP

FILAMENT IS UPDATED.

WHEN RAM INIT NEW ROM SET

WRITTEN INTO RAM

12 START UP PAGE

13 AUTO TEST CHECK IF ALL BOARDS ARE

PRESENT. DEPENDS ON SDB

INFO

14 START VACUUM SYSTEM AUTOMATIC/NON-AUTOMATIC

DEPENDS ON SDB JUMPER

15 CALIBRATING THE STEM

Contents

Figures

Basic course I/O bus 1-12

Basic course I/O bus 1-13

Contents

Figures

H FLOWCHART START-UP PROCEDURE VERSION 10 ONWARDS, PART 1

On Board ROM Check

DATA RAM Test 1

NV RAM Battery Test 2

Yes Data

RAM Test 3

Failed

No

NV RAM Test

Program

RAM ROM

Board

type

6

Program

Valid Non Valid Failed PROM pair

Data 5

Loaded Checksum

Program RAM Block

6A Block Read/Write 6B

Passed

Checksum Test

Data

Waiting RAM test &

No

7 for PC NV RAM battery

to Attach test

passed

Yes

Load new

programme Scanning serial port

via Down for PC 8

Loadable

Lens series

Diagnose 9 Diagnose

Programme 10

via TAD

Aktive

No

Contents

Figures

A

H

Basic course I/O bus 1-13

Basic course I/O bus 1-14

Contents

Figures

FLOWCHART START-UP PROCEDURE, VERSION 10 ONWARDS PART 2

BUS INITIALIZATION SETS BUS PORTS FOR USE

DETERMINE HARDWARE CONFIG. CHECK SBD BOARD

CHECK FOR DEFAULT RAM INIT. VIA SOFTKEY OR VIA JUMPER SDB-D2

READ/CHECK SOLID STATE KEY IN CASE OF RAM INIT SOLID

STATE KEY IS WRITTEN INTO RAM

INIT DATA RAM DURING NORMAL START- UP

FILAMENT IS UPDATED.

WHEN RAM INIT NEW ROM SET

WRITTEN INTO RAM

START- UP PAGE

AUTO TEST CHECK IF ALL BOARDS ARE

PRESENT. DEPENDS ON SDB

INFO

START VACUUM SYSTEM AUTOMATIC/NON-AUTOMATIC

DEPENDS ON SDB JUMPER

CALIBRATING THE STEM

Contents

Figures

H

H

Basic course I/O bus 1-14

Basic course I/O bus 1-15

Contents

Figures

RAM-INIT

RAM-INIT can be done the start with a known set of alignments

RAM-INIT This can be done in various ways but the principle is to remove a

known pattern that indicates valid alignment data (ABBA)

1 Service calibrate, RAMINIT microscope off and on.

2 SDB jumper D2 present, microscope off and on

3 Remove the batteries from RCB and leak out data (30min)

4 Use test software to write a new pattern.

SDB KEY NUMBER

During the RAMINIT a DEFAULT alignment set is copied from pro-

gram to NV RAM where it is modified during alignments.

During a RAM-INIT the key number is copied into the non volatile

ram.(this must be done after a different customer key is inserted

e.g. when a new software option is installed)

NV RAM KEY NUMBER

From now on every 10 minutes the number in the key and the

number in NV RAM are compared. If not the same the error mes-

sage “KEY MISMATCH” is shown.

At switching on the version number in the key and the version

number in the software are compared. If not the same the error

message “VERSION NUMBER MISMATCH” is shown

The contents of the non volatile RAM can be stored in two ways:

Using the REMOTE CONTROL program.

This program does not store all data as it assumes that in between storing and reloading, settings have

been changed. The following settings are not stored:

Gun alignments

Camera settings

User data in STEM

Aperture memo

Last used mode before switching off

Using the TAD software.

Contents

This program makes a exact copy of the NV RAM and contains thus all alignments.

Figures

H

H

Basic course I/O bus 1-15

Basic course I/O bus 1-16

Contents

Figures

SOFTWARE MESSAGE NUMBERS

Err.no. Description Err.no. Description

00 Vacuum interlock 32 Mismatch instrument number

01 Pneumatics 33 Mismatch key number

02 Critical backing pressure 34 Mismatch version number

03 ODP circuit 35 Service key installed or softkey diagnostic program

04 ODP water 36 Calibrating the line times

05 ODP oil 37 Printer not selected

06 Valve 38 Mismatch Baud rate printer

07 IGP interlock 39 Mismatch Baud rate printer

08 ODP interlock 40 Printer

09 Main screen handle 41 Keybord not responding

10 Camera moved 42 Automatic determination of goniometer centre

11 Film stock 43 Out of limit please recalibrate

12 Plate stock 44 Servo not receiving RFR not high

13 Camera drive 45 Servo not transmitting RFR not low

14 Plate unload 46 Servo output not accepted

15 Exposure time out of range 47 Servo overflow

16 DAC output failed 48 Servo positioning error

17 Battery-backup failed 49 EDX protection active

18 Default RAM initialisation 50 Left spec drive positive limit

19 DAS error bit set 51 Left spec drive negative limit

20 Error-power-fail-sense 52 Right spec drive positive limit

21 Battery-backup unreliable 53 Right spec drive negative limit

22 Solid-state-key 54 No end detected

23 SDB or BTR error 55 2 peripheral devices without SDB-jumper A7

24 Memory test inverse checksum error 57 HREM series incompatible with nanoprobe

25 Memory test mmb checksum error 58 Error in calibrating the line times

26 Memory test r/w NVRAM error 59 Spec airlock time is not standard

27 Memory test r/w DATARAM error 60 Not allowed because vacuum not ready

28 Start-up of a new LAB6 cathode 61 MIB 2 not installed

29 Start-up of a new W cathode

Contents

30 Start-up of a LAB6 cathode

Figures

H

H 31 Start-up of a W cathode

Basic course I/O bus 1-16

Basic course I/O bus 1-17

Contents

Figures

Software error number continued

Err.no. PC Board Remarks Err.no. PC Board Remarks

100 QDCR-1 121 HVG

101 QDCR-2 122 REF

102 QDCR-3 123 SDD/GCB

103 QDCR-4 124 CMD

104 QDCR-5 125 SOB-1

105 QDCR-6 125 SOB-2

106 QDCR-7 126 SYNC STEM only

107 MDAC-1 127 TVFX STEM only

108 MDAC-2 STEM only 128 SMDR STEM only

109 MDAC-3 STEM only 129 MDRV STEM only

110 MDAC-4 130 SDCG STEM only

111 MDAC-5 STEM only 131 FRGN STEM only

112 HRDS 132 LNGN STEM only

113 PCI-1 STEM only 133 NLIM STEM only

114 PCI-2 134 FBDR STEM only

115 PCI-3 135 MOB-3 CM20(0) or CM30(0)

only

116 PBI 136 CTB FEG only

117 MOB-1 137 QDCR-8 FEG only

118 MOB-2

119 MIB-1/MIB-2

120 PVG

Contents

Figures

H

H

Basic course I/O bus 1-17

Fig. 7MMB Jumper settings Basic course I/O bus 1-18

Contents

Figures

Multi bus Back Panel Jumper settings

W W W W W W

6 5 4 3 2 1

X1 X2 X3 X4 X5 X5

MBB - 4022 192 5160

Multi bus back panel lay-out

Address

P.C.B. Address Jumper settings and remarks

jumpering

MBB Lens circuit CM10(0)/CM12(0) CM20(0) CM20(0) FEG CM30(0) CM30(0) FEG

Back panel W6 W6 W6 W6 W6

SBC 86/05 W2-3, W6-7, W10-11, W2-3, W6-7, W10-11, W2-3, W6-7, W10-11, W2-3, W6-7, W10-11, W2-3, W6-7, W10-11,

W14-15, W19-20, W25-27, W14-15, W19-20, W25-27, W14-15, W19-20, W25-27, W14-15, W19-20, W25-27, W14-15, W19-20, W25-27,

W28-29, W32-33, W38-42, W28-29, W32-33, W38-42, W28-29, W32-33, W38-42, W28-29, W32-33, W38-42, W28-29, W32-33, W38-42,

W39-43, W40-44, W41-45, W39-43, W40-44, W41-45, W39-43, W40-44, W41-45, W39-43, W40-44, W41-45, W39-43, W40-44, W41-45,

W46-50, W47-51, W48-52, W46-50, W47-51, W48-52, W46-50, W47-51, W48-52, W46-50, W47-51, W48-52, W46-50, W47-51, W48-52,

W49-53, W56-57, W58-59, W49-53, W56-57, W58-59, W49-53, W56-57, W58-59, W49-53, W56-57, W58-59, W49-53, W56-57, W58-59,

W60-61, W79-80, W83-84, W60-61, W79-80, W83-84, W60-61, W79-80, W83-84, W60-61, W79-80, W83-84, W60-61, W79-80, W83-84,

W87-88, W89-90, W91-92, W87-88, W89-90, W91-92, W87-88, W89-90, W91-92, W87-88, W89-90, W91-92, W87-88, W89-90, W91-92,

W107-108, W115-116 , W107-108, W115-116 , W107-108, W115-116 , W107-108, W115-116 , W107-108, W115-116 ,

W157-W159, W170-171, W157-W159, W170-171, W157-W159, W170-171, W157-W159, W170-171, W157-W159, W170-171,

W174-175, W177-178, W174-175, W177-178, W174-175, W177-178, W174-175, W177-178, W174-175, W177-178,

W179-180, W183-184, W179-180, W183-184, W179-180, W183-184, W179-180, W183-184, W179-180, W183-184,

W186-187, W188-189, W186-187, W188-189, W186-187, W188-189, W186-187, W188-189, W186-187, W188-189,

W191-192, W204-205, W191-192, W204-205, W191-192, W204-205, W191-192, W204-205, W191-192, W204-205,

W212-213 , W217-218, W212-213 , W217-218, W212-213 , W217-218, W212-213 , W217-218, W212-213 , W217-218,

W221-222 W221-222 W221-222 W221-222 W221-222

MMB W3, W7,or W8,or W9 W3, W7,or W8,or W9 W3, W7,or W8,or W9 W3, W7,or W8,or W9 W3, W7,or W8,or W9

depending on SW version depending on SW version depending on SW version depending on SW version depending on SW version

Quad Serial 121-126, 62-63, 105-106, 121-126, 62-63, 105-106, 121-126, 62-63, 105-106, 121-126, 62-63, 105-106, 121-126, 62-63, 105-106,

131-135, 80-81, 80-79, 87- 131-135, 80-81, 80-79, 87- 131-135, 80-81, 80-79, 87- 131-135, 80-81, 80-79, 87- 131-135, 80-81, 80-79, 87-

Port 88, 87-86, 94-95, 94-93, 88, 87-86, 94-95, 94-93, 88, 87-86, 94-95, 94-93, 88, 87-86, 94-95, 94-93, 88, 87-86, 94-95, 94-93,

101-102, 101-100, 1-2, 4-5, 101-102, 101-100, 1-2, 4-5, 101-102, 101-100, 1-2, 4-5, 101-102, 101-100, 1-2, 4-5, 101-102, 101-100, 1-2, 4-5,

7-8, 9-10, 11-12, 14-15, 17- 7-8, 9-10, 11-12, 14-15, 17- 7-8, 9-10, 11-12, 14-15, 17- 7-8, 9-10, 11-12, 14-15, 17- 7-8, 9-10, 11-12, 14-15, 17-

18, 19-20, 21-22, 24-25 27- 18, 19-20, 21-22, 24-25 27- 18, 19-20, 21-22, 24-25 27- 18, 19-20, 21-22, 24-25 27- 18, 19-20, 21-22, 24-25 27-

28, 29-30, 31-32, 34-35, 37- 28, 29-30, 31-32, 34-35, 37- 28, 29-30, 31-32, 34-35, 37- 28, 29-30, 31-32, 34-35, 37- 28, 29-30, 31-32, 34-35, 37-

38, 39-40, 64-65, 67-68, 70- 38, 39-40, 64-65, 67-68, 70- 38, 39-40, 64-65, 67-68, 70- 38, 39-40, 64-65, 67-68, 70- 38, 39-40, 64-65, 67-68, 70-

Contents

71, 74-75, 48-49, 51-52, 44- 71, 74-75, 48-49, 51-52, 44- 71, 74-75, 48-49, 51-52, 44- 71, 74-75, 48-49, 51-52, 44- 71, 74-75, 48-49, 51-52, 44-

45, 41-42 45, 41-42 45, 41-42 45, 41-42 45, 41-42

Figures

H

H

Basic course I/O bus 1-18

continuedi Basic course I/O bus 1-19

Contents

Figures

Address

P.C.B. Address Jumper settings and remarks

jumpering

MBB Lens circuit CM10(0)/CM12(0) CM20(0) CM20(0) FEG CM30(0) CM30(0) FEG

RCB W4,W5,W8,W9,W11,W12, W4,W5,W8,W9,W11,W12, W4,W5,W8,W9,W11,W12, W4,W5,W8,W9,W11,W12, W4,W5,W8,W9,W11,W12,

W19, W22,W24,W40,W43, W19, W22,W24,W40,W43, W19, W22,W24,W40,W43, W19, W22,W24,W40,W43, W19, W22,W24,W40,W43,

W49,W50,W52,W54,W63, W49,W50,W52,W54,W63, W49,W50,W52,W54,W63, W49,W50,W52,W54,W63, W49,W50,W52,W54,W63,

W66,W72,W74,W75,W76, W66,W72,W74,W75,W76, W66,W72,W74,W75,W76, W66,W72,W74,W75,W76, W66,W72,W74,W75,W76,

W79 W79 W79 W79 W79

Contents

Figures

H

H

Basic course I/O bus 1-19

Fig. 8Vacuum sytem block diagram Basic course I/O bus 1-20

Contents

Figures

H

PRE VACUUM

GAUGE P1 PRESSURE

X5 / X6 P2 PRESSURE VACUUM

SYSTEM

PIRANI’s P1, P2

MBCR-X8

HIGH VACUUM LOW HIGH

GAUGE TENSION -2kV

P3 PRESSURE X1

PENNING (P3)

MBCR-X20 MBCR-X9

X1 X17 MEASURING

V1, V2, V3, V4,V5

VACUUM V6,V7,V8,V9,V10

DISTRIBUTION V11,V12

BOARD V18,V19 (CM200/300)

MULTIPLE INPUT

BOARD CNTRL SIGNALS

X5 X4 X10

PDTMR (ODP OFF)

MBCR-X17 X2 PFD

POTMR

LOCKING

MATRIX IGP MBCR-X1

IGPDR 220V X1 SUPPLY X3

MAINS PANEL IGP

P / A13 ODPST

ODPDR 220V

ODP

HEATER

SPECIAL OUTPUT

BOARD 1

X5 X2 PVPDR 220 + 10V

P.V.P.

MBCR-X19

DRIVE SIGNALS

TO VALVES

SPECIAL OUTPUT VACUUM

X202

BOARD 2 CNTRL INDICATORS

X5 X3 X11 X402

LED’S (LED’S)

RHP, A2 / A4

MBCR-X18

AIRLOCK EPD

LHP R.H. EAR

X21 X1 X14 X12 VAC.

INDICATION

TILT HOLDER

FOOTSWITCH

DMD/SMD SPECIMEN HOLDER

X22 DUAL MOTOR DRIVE

X6 X5 X5 TILT

SPECIMEN

MOTOR

MOTOR

X23 ONLY CMXX

X24 X17-3 AND X17-36

X25

BAKE OUT

VALVE Y23 IGP INTERLOCK

(NOT FOR CM300)

GONIOMETER

X101 X102 DISTRIBUTION

X21 MBG BOARD

GONIOMETER X2 X11 X5 X9 MOTORS X,Y,Β

CONTROLLER FEED BACK & EPD

BOARD

X1 X12

X20 MBG X1-X2 X2 STAGE CURRENT

BOOSTER X11 X5 X9 MOTORS Α,Z

X1 X1

MBG X3 FEED BACK & EPD

X12

JOYPAD

MIB-2

Contents

MBCR X3 HOLDER CONNECT, HOLDER INDENTIFY, HOLDER SAFE

Figures

EM4356-3D

Basic course I/O bus 1-20

Fig. 9HT block diagram Basic course I/O bus 1-21

Contents

Figures

H

HT INT 1

HT INT 2

OS CON

COND E

COND 3

CONDITIONS

HIGH TENSION SWITCH-ON SIGNALS + START +15V DOUBLING +30V

SWITCH-ON

HT ON-OFF

EMERGENCY STOP -15V -30V

P / A9-X7 P / A9-X1

HT FAST COND 2

(2/3)

REFERENCE

WEHNELT SWITCH LEFT RIGHT TRIPPLE MOTOR

X4

SWITCH

WEHNELT

MOTOR

MBCL X14 P / A9-X4

WEHNELT POSITION WEHNELT SWITCH POSITION

P / A16

HT CHANGE BUFFER

I SUM = Ie + Im

P / A9-X5 HT TANK

Im

HT CHANGE

EMISSION METER P / A15

HIGH TENSION

REGULATOR

HT REF PE 1264 / 40

P / A9-X6

OSCILLATOR HT

P / A9

STH

HP ON

P / A9-X2

FIL DRIVE

PE 1269

OSCILLATOR FIL.

FP ON

P / A8

START

P / A9-X3

STF

TESTLINE

FILAMENT

DRIVE

EM4356 - 4C

Contents

Figures

Basic course I/O bus 1-21

Fig. 10Camera sytem block diagram Basic course I/O bus 1-22

Contents

Figures

H (FIL DRIVE)

HT MEASURE (Ie and Im) HIGH RESOLUTION

DATA AQUISITION

VACUUM PRESSURES (P1, P2, P3, IGP) SYSTEM

(8 OR 16 BITS)

TEM POSITION

MBCL X13 - X33

WHEN HAVING A

VREF STEM UNIT

REFERENCE POSITION IS

MDEL X9 - X29

LREF = f = (HT) SCREEN CURRENT

MBCL -X14 TEST LINE

VIDEO IN VIDEO OUT

SCRUP SMSCRN

SCREEN CURRENT SHUTTER COIL

SCRUP AMPLIFIER

S 20 PLCNP

CAMERA DRIVER PLATE CAMERA

PLCWP

MBCR -X7

FEGON (FEG only)

CMRDY*

TMS 35 mm CAMERA

OR NOT FOR CM20(0) /

FSB (for FEG)

CM20(0) FEG AND S10

CMBSY*

CM30(0)

* CMRDY and CMBSY are used for FEG as FEGON and FEG ACK

CONDITIONS

CMXX SEGMENT

PLATE NUMBERING

DISPLAY DRIVER

IN PROJECTION

CMXXX GENERAL CHAMBER

CONTROLER

BOARD

MBCR-X5

SERIAL PORT

PC UNDER WINDOWS

WITH TEXT EDITOR

(CMXXX only)

Contents

EM4356-5C

Figures

Basic course I/O bus 1-22

Fig. 11Lenses block diagram Basic course I/O bus 1-23

Contents

Figures

H

TEST

1 / 2 MULTIPLE

DAC

1 / 8 LINE COARSE

1 / 8 LINE FINE

1 / 8 FRAME COARSE

1 / 8 FRAME FINE

MBCL X12-X32

LPR

TEST

1 / 8 MULTIPLE

DAC

LREF MBCL X3-X23

CM12(0) ONLY

TEST

1 / 4 QUAD CURRENT 1 / 2 DUAL CURRENT 1 / 2 FLY BACK

REGULATOR BOOSTER DRIVER

X5 X5 X5

PERSONALITY SLOW,FAST*

MBCL X21A

LREF MBCL X10-X30 MBA X3-A MBCL X1-X21

BEAM

DEFLECTION

LOWER X

FOOT

RESISTOR

TEST

1 / 4 QUAD CURRENT

REGULATOR

PERSONALITY

LREF MBCL X2-X22

*SLOW = CM100

FAST = CM120 STEM

TEST

1 / 2 MULTIPLE

DAC

1 / 8 LINE COARSE

1 / 8 LINE FINE

1 / 8 FRAME COARSE

1 / 8 FRAME FINE

MBCL X12-X32

TEST

1 / 8 MULTIPLE

DAC

LREF MBCL X3-X23

CM12(0) ONLY

TEST

1 / 4 QUAD CURRENT 1 / 2 DUAL CURRENT 1 / 2 FLY BACK

REGULATOR BOOSTER DRIVER

X5 X5 X5

PERSONALITY SLOW,FAST*

LREF MBCL X10-X30 MBA X3-B MBCL X1-X21 BEAM

DEFLECTION

LOWER Y

FOOT

RESISTOR

TEST

1 / 4 QUAD CURRENT

REGULATOR

PERSONALITY

Contents

LREF MBCL X2-X22 EM4356-9C

Figures

Basic course I/O bus 1-23

Basic course I/O bus 1-24

Contents

Figures

1.4 I/O Bus principles

• PUT

• GET

• LOAD DAC

Contents

Figures

H

H

Basic course I/O bus 1-24

Basic course I/O bus 1-25

Contents

Figures

1.4.1 General info on I/O bus

The I/O bus begins at the PPI (Pheripheral Programmable Interface) chip

located on the Ram Combi Board.

This contains 3 ports

– Input bus, 8 bits DATA in = Port B

– Output bus 8 bits ADDRESS and DATA (in turn) = Port A

– Control bus 8 bits = Port C

The control port C contains the following bits:

Input signals Strobe in

Acknowledge

Output signals Read data

Write data

Write address

Input buffer full

Service request enable

Interrupt A or B (4 respectively 5)

The control signals take care of the timing and handshake of the signals over

the input and output bus

Input and output is done via three type of procedures:

“put” This is an output to load DATA in an I/O board

“get” This is an input to read DATA from an I/O board

Contents

“Load dac” This a an output of three DATA bytes to load a 12 bits DAC

Figures

H

H

Basic course I/O bus 1-25

Basic course I/O bus 1-26

Contents

Figures

1.4.2 Put routine

• Service request is disabled

• Address is set on the output bus

• Write address is set on the control bus

• Data is set on the output bus

• Write data is set on the control bus

• Acknowledge is made on the selected board by means of the signals card

select AND write data (handshake)

• Software now tests for the signal acknowledge. If present the signal write

data is removed from the control bus

• Acknowledge is then removed in turn from the selected board

• The selected board is deselected by putting an unused address (00F) on the

bus together with its cotrol signal write address.

Contents

Figures

H

H

Basic course I/O bus 1-26

Fig. 12Put routine timing diagram Basic course I/O bus 1-27

Contents

Figures

BASIC OUTPUT ROUTINE BUS CLEAR ROUTINE

25 µs

ADDRESS

OUTPUT BUS DATA

8 µs 7 µs

WRITE ADDRESS

8 µs

WRITE DATA

15 µs 25 µs

ACKNOWLEDGE

20 µs 1 ACKNW DELAY IN THIS EXAMPLE

APPR. 20 µs.

1 x WAIT 2

2 0 ≤ WAIT < 1 ms.

EM4562

Contents

Figures

H

H

Basic course I/O bus 1-27

Basic course I/O bus 1-28

Contents

Figures

1.4.3 Get routine

• Service request is enabled via the control bus

• Data difference (indicating that new data is present) latches an identifier code

(made be a jumper selection) on the input bus. Data difference AND service

request produce the control signal strobe in.

• Strobe in latches the identifier code into port B (located on the Ram Combi

Board). This in turn generates the control signal input buffer full acting as the

handshake signal to the board. It removes the strobe in signal on the board.

• Input buffer full also creates an interrrup signal to the computer board.

• The software generates an interrupt routine to learn the boards identifier

code.

• The control signal input buffer full is set false.

• The control signal service request enable is set false so that the software can

controle the output bus.

• Address is set on the output bus

• Write address is set on the control bus

• Read data is set on the control bus, this signal AND card select generate a

second strobe in. Strobe in also sets the new data on the input bus

• Strobe in atches the new data into port B (located on the Ram Combi Board).

This in turn generates the control signal input buffer full acting as the

handshake signal to the board. It removes the strobe in signal on the board.

• Input buffer full also creates an interrrup signal to the computer board.

Contents

Figures

H

H

• The software generates an interrupt routine to read the new data.

Basic course I/O bus 1-28

Fig. 13Get routine timing diagram Basic course I/O bus 1-29

Contents

Figures

• The control signal input buffer full is set false.

• The selected board is deselected by putting an unused address (00F) on the

bus together with its cotrol signal write address.

BASIC INPUT ROUTINE = 110 µs BUS CLEAR ROUTINE

(INCL. 1 WAIT STATE)

OUTPUT BUS BUSY

8 µs 7 µs

WRITE ADDRESS

8 µs

READ DATA

INPUT BUS

I/O READ

1

STROBE IN

16 µs

15 µs

32 µs

INPUT

BUFFER FULL 3

CPU READ TEST 0 TEST 1

20 µs CPU READ

1x WAIT

INPUT BUS BUSY 1 STBIN PULSE WIDTH DEPENDS ON

OPTO COUPLER DELAY, TYPICAL 5 µs.

2 STBIN DELAY, IN THIS EXAMPLE APPR. 20 µs.

EM4561

3 STROBE GENERATES AN INTERRUPT. ONCE INTERRUPT

IS ACCEPTED THE INPUT BUFFER IS READ BY

COMPUTER.

Contents

Figures

H

H

Basic course I/O bus 1-29

Basic course I/O bus 1-30

Contents

Figures

1.4.4 Load Dac routine

• Service request is disabled

• Address is set on the output bus

• Write address is set on the control bus

• Data is set on the output bus

• Write data is set on the control bus

• Acknowledge is made on the selected board by means of the signals card

select AND write data (handshake)

• Data is set on the output bus

• Write data is set on the control bus

• Acknowledge is made on the selected board by means of the signals card

select AND write data (handshake)

• Data is set on the output bus

• Write data is set on the control bus

• Acknowledge is made on the selected board by means of the signals card

select AND write data (handshake)

• Software now tests for the signal acknowledge. If present the signal write

data is removed from the control bus

• Acknowledge is then removed in turn from the selected board

• The selected board is deselected by putting an unused address (00F) on the

Contents

bus together with its control signal write address.

Figures

H

H

Basic course I/O bus 1-30

Basic course I/O bus 1-31

Contents

Figures

1.5 Examples of comon used electrical diagrams

• Address and base selection

• Acknowledge

• Realization of strobe in signal

• Strobe in

• Interrupt routine

• Load dac procedure

Contents

Figures

H

H

Basic course I/O bus 1-31

Fig. 14Address selection example Basic course I/O bus 1-32

Contents

Figures

+

8 x 1k

1k

8 x 1k

LSB

D OUT 0 1k

D OUT 1

D OUT 2

INTERNAL BUS

D OUT 3

D OUT 4

D OUT 5

D OUT 6

D OUT 7

+

CARD

ADDRESS

SELECTION

MSB

1

&

2 5

BUFFER

3

4 6

1

5 1k

&

&

2

3

0.1µF

4 6

4M7

CP

MR CRDSL

+

A3

00

LSB

EM4582

1

BASE +0

DECODER

2 5

BUFFER A2 BASE +1

BASE +2

A1 BASE +3

BASE +4

+

A0 BASE +5

BASE +6

BASE +7

CP

6 x 100k

100k

09

6 x 1k

MR

WRADR 1k

RESET RESET

WRDAT

WRDAT Acknowledge part

RDDAT

RD DAT

INPBF

INPBF

Contents

SRQEN SRQEN

Figures

H

H

Basic course I/O bus 1-32

Fig. 15Interrupt procedure example Basic course I/O bus 1-33

Contents

Figures

D-FF

LSB

8 x 150E

40175

CP

MR

40098

COMP

0

EO

P

DTIN0

BYTE

3 0

P<Q

DTIN1

P=Q

Q

P>Q DTIN2

3 < = >

DTIN3

4585

++

DTIN4

DTIN5

D-FF

DTIN6

DTIN7

MSB

41075

CP

MR

COMP

0

EM4566

40098

3 0

P<Q

EO

A=B=1

P=Q

Q

P>Q

3 < = >

4585

+

RESET

+

40097

&

BASE + A

STBIN

10k 150

&

1k5

1M

SRQEN

&

10k

RDDAT

&

&

10k

CRDSL

1k5

INPBF

Contents

Figures

H

H

Basic course I/O bus 1-33

Fig. 16Overview diagram puts and gets Basic course I/O bus 1-34

Contents

Figures

SBC86/05 RAM COMBI BOARD BUS TRANSLATOR INPUT OUTPUT BOARD

Bin Base 0

Base 1

to

Opto coupler Base 2

Address selection Dec Base 3

Base 4

output output

Base 5

Base 6

port A Base 7

8255 crdsl

Programmable

Pheripheral

Interface

stbin

8259A

Interrupt input input &

acknw

controller datdiff

&

int 0 & old compa new

CONTROL rator

int 1 Buffer BUS wraddr

int 2 output

output wrdat

Int int 3

int 4 inpbf

port C

int 5 srqen

int 6 rddat

int 7 Tristate

Buffer

input input

Base 0

port B Input

Tristate device

Buffer

ID code

Reset

datdiff

Contents

Figures

aclo

H

H EM7656

Basic course I/O bus 1-34

Fig. 17Load DAC example Basic course I/O bus 1-35

Contents

Figures

+5V

ACKNW

154

LSB

AD OUT 0

AD OUT 1

BUFFERED DAC BUS

NON INV BUFFER

INTERNAL BUS

AD OUT 2

AD OUT 3

AD OUT 4

AD OUT 5

AD OUT 6

MSB

AD OUT 7

E

EO

CRD BL

10k

+5V

2k2

A0

A1

D0

D1

D2

D3

RFB

OUT 1

WR

12 BIT DAC

CRDSL + WRDAT

AD 7542

CLR

RESET

INV BUFFER

CS

OUT 2

BASE 0 + TRANS

BASE 1 + TRANS

VREF

AGND

100k

A0

A1

D0

D1

D2

D3

RFB

OUT 1

EM4584

WR

12 BIT DAC

AD 7542

CLR

CS

OUT 2

VREF

AGND

Contents

Figures

H

H

Basic course I/O bus 1-35

Fig. 18DAC AD7542 block diagram Basic course I/O bus 1-36

Contents

Figures

AD7542 FUNCTIONAL BLOCK DIAGRAM

Vref

15

18

Rfb

AD7542 1

Out 1

12 BITS MULTIPLYING DAC 2

Out 2

3

Agno

13

CLR 12 BITS DAC REGISTOR

9

WR L-BYTE

H-BYTE M-BYTE 14

8 DATA DATA DATA V00

ADDRESS

CS REGISTER REGISTER REGISTER 12

Dgnd

DECODE

10

A0 LOGIC

11

A1 7

D0 (lsb)

6

D1

5

D2

4

D3 (msb)

Contents

Figures

H

H

Basic course I/O bus 1-36

Basic course I/O bus 1-37

Contents

Figures

1.6 I/O Boards

• Block diagram (high level)

• Block diagram (low level)

• MOB

• MIB

• PBI

• PCI

Contents

Figures

H

H

Basic course I/O bus 1-37

Fig. 19Input output block diagram Basic course I/O bus 1-38

Contents

Figures

H

PBI RHP

X205 S433 S440 S450 S460 LHP A3

X5 X405 S434 S442 S451 S461 X404 X301 S374

S435 S443 S452 S462 S375

S436 S444 S453 S463 S376

S437 S445 S454 S464 S377

MBCR X13 S446 S455 S465

S447 S456 S466 RHP A1

S103 S110 S115 S120 S125

S233 S457 S467 X401 X101

S104 S111 S116 S121 S126

S234 S236

S106 S112 S117 S122 S127

S235 S237

S107 S113 S123

S114 S124

A2 / A4

PCI 1

X207 X201

X5 B491 X401 X101 RHP A1

X407 B194

B492

B493

MBCR X12

RHP A1 RHP

PCI 2 A2 / A4 LHP A3

X201 X204

B181

X5 X103 B182

X101 X401 X404 X301 B384

B183

INTENSITY

MBCR X11

DATA CRT

PCI 3 B171

B172

X5 X102 B173

B174

B175

B176

MBCR X10

INPUTS

OUTPUTS

RHP A2 / A4

MOB 1

X206 X204 LHP A3

B233 / 433

X5 X406 B234 / 434 X404 X301 B374

B376

B235 / 435

B377

B440 B444

B441 B445

MBCR X14 B442 B446

B443 B447

X201 B103 RHP A1

X401 X101 B104

B105

B106

B107

SEE FIG. 403

M4

MOB 2 B451 B460

B452 B461

X5 X10 X11 B453 B462

B454 B463

X408 B456 B464

B457 B465

MBCR X15 B466

PANEL LIGHT

X202

MAINS ON - OFF X402

VDB X11

V.A.C. ON - OFF

MOB 3

* X5

LEVELLING

X1 SYSTEM

EM4356-2D

Contents

MBCR X6

Figures

* = CM300 ONLY

REMOVED FROM 1990 ONWARDS

= ONLY FOR STEM

H

Basic course I/O bus 1-38

Fig. 20Input output block diagram (detailed) Basic course I/O bus 1-39

Contents

Figures

X204

X5 - X206 (X404) X301

MOB 1 21

(X406)

21 RHP 23 23 LHP B374

MBCR X14 (192 7007)

20 20 4 4

B376

1 1 5 5

B377

X201 22 22

X101

4 4 37

B103 A3

13 13 38

B106

36 TEM STEM MAGNIFICATION ZOOM

22 22

B104 B103 B103 D

32 32 39

B107 FOCUS

49 X101-40 B104 B104 AUTO

2 2 ROOM

50 DIM X201 B106 B106 RESET

CONTROL (X401) B107 B107 READY

BEEP A1 40

7 7 B374 B374 EXPOSURE

10k + 5V LIGHT 1

RHP A2 14 14 MNS OFF B376 B376 FINE

SEE SWITCHINGON CIRCUIT

TEM STEM 33 33 STB OFF B377 B377 WBL

27 27 B433 MULTIFUNCTION

S120 S121 S122 S123 S124 S125 S126 S127 (B233)

MAGNIFICATIONS

8 8 B434 B233 B433 STIG

S103 S103 D (B234)

S110 S111 S112 S113 S114 S115 S116 S117 B234 B434 DF

26 26 B435

(B235) B235 B435 ALGN

FOCUS S103 S104 S106 S107 31 31 B440 SCAN MODE

S104 S104 AUTO B440

12 12 B441

S106 S106 RESET B441

X101 30 30 B442 LIGHT 1

S107 S107 READY B442

11 11 B443 B443

SOFT KEYS 48 53 46 57 47 54 58 55 60 56 59

B444 SCAN STOP

29 29 B444

S110 UP S110 UP VARIOUS X201 MULTIFUNCTION

TO S120 TO S120 FUNCTIONS (X401) X205 PBI 10 10 B445

(X405) MBCR X13 B233 B433 STIG

X5

S374 S374 EXPOSURE 28 28 B446 B234 B434 DF

6 / 18 6 / 18 PRIORITY (192 7002)

S375 S375 RST I7

DECODER 9 9 B447 B235 B435 ALGN

S376 S376 FINE 7 / 19 7 / 19

S377 S377 WBL I6 23 23 SPARE MOB 14

NOT ALL QDCR LPR ALL DCB

8 / 20 8 / 20 25 25 FBD - Y ON 2 USED BOARDS MBCL X34 BOARDS

MULTIFUNCTION I5

6 6 FBD - X ON 15

S233 S433 STIG 9 / 21 9 / 21 311 114 125 MBCL X34B-20 316

I4 3 - STATE 24 24 FAST / SLOW 1 1

S234 S434 DF

HEX 5 5

S235 S435 ALGN 10 / 22 10 / 22 5 5 LPROT MBA X36-20

I3 INVERTING

S236 S436 VAC OFF BUFFER 15 15 X203 MBCL - X46

S237 S437 VAC ON 11 / 23 11 / 23 16 16 (X403)

I2

17 17

SCAN MODE 12 / 24 12 / 24

18 18

I1

S440 19 19

13 / 25 13 / 25

S441 I0 34 34

AD - OUT

DAT - IN

S442 35 35

S443 36 36

S444 SCAN STOP 37 37

5 5 A4 (A2)

I7 PRIORITY

VIEWING SCAN RATE S460 S461 S462 S463 S464 S465 S466 S467 DECODER

4 4 X208

S445 FLOW I6 X5 - X10 - X11 - (408)

S446 FAST S451 S452 S453 S454 S455 S456 S457

3 3 MOB 2 23

23 MU - A2 1 1 B460 LIGHT 1 DUAL MODE

S447 T.V. I5

S440 S441 S442 S443 S444 S445 S446 S447 MBCR X15 (192 7007) 4 4 9 9 B461 B451 SGNL

DUAL MODE 2 2

I4 22 2 2 B452 MAG

S451 SGNL S433 S434 S435 S436 S437 22 B462

x x 16 16 B453

S452 MAG I3 3 3 10 10 B463 RHP

S453 (A4) A2 B454

15 15 21 3 3

I2 21 B464

S454 PHOTO SCAN RATE

14 14 2 11 11 B465

PHOTO SCAN RATE 2 B455 EXP1

RHP I1

S455 EXP 1 20 20 4 4 B466 B456 EXP2

A2 (A4) 1 1

S456 EXP 2 I0 12 12 B457 EXP3

8 8 B451

S457 EXP 3 VIDEOMODE

26 26 5 5 B452

DUAL MODE B460

7 7 13 13 B453

S460 3 21 2 20 1 X204 B461

S461 (X404) 25 6 6

25 B454

B462

S462 14 14

3 21 2 20 1 X301 6 6 B455 B463 PHOTO EXPOSURE

S463 PHOTO EX-

POSURE 24 24 7 7 B456 SIGNAL CONTROL

SIGNAL CONTROL 5 15 15 B457 B464 SET

5

S464 SET

LHP LIGHT 1 8 8 B465 AUTO

S374 S375 S376 S377 27 FREQ

S465 AUTO A2 (A4) 27 B466

9 9

S466 STATVR X14 LX1 B467

12 12

V. LINE - L 3 3 MU - A1

S467

13 13 LED 1 2 2 B1

= = 32 32 LED 2 1 1 B2

x

X15 RX1

14 14 LED 3 2 2 B3

33 33 LED 4 1 1 B4

3 3

X13 X1 - X3 - PSP-X2 X3 - HRM(A1) X50-

28 14 8 8 8 4

28 MAPP MAPP 14 MAPP MU - A3 (A5) MAPPING 3

1 1 REC REC 2 2 REC 7 7 7 5

- 5V

REC 1 1 REC 6 6 6 X84-15 RECORD

TO FIG. 424-1B TV - L 11 11 TV - L X105-6 MON. LEFT X84-16 16

5 A3 + 15V

10 10 TV DOT - L 10 10 DOT - L 3

MON. RIGHT

4 A3

LINE - L 9 9 LINE - L 1

29 2

29 DOT SLOW- L 12 12 SLOW- L 7

4 4 8

TV - R TV - R X104-5

6

11 11 LINE - L DOT - R 5 5 DOT - R 3 EM4508-1E

30 30 6 6

Contents

LINE - R LINE - R LINE - R 1

31 31 SLOW SLOW- R 3 3 SLOW- R 8

Figures

H

H

Basic course I/O bus 1-39

Fig. 21Multiple output board block diagram Basic course I/O bus 1-40

Contents

Figures

MOB

ADDRESS &

LATCH

Red led

ADDRESS

DATA

Byte 0

BCD Byte 1

DECI-

MAL Byte 2

Byte 3

BUFFERS

8x

20 output lines

(31/2 bytes)

OUTPUT

WRADR CONTROL

WRDAT SIGNALS

RESET

Contents

Figures

H

H

Basic course I/O bus 1-40

Fig. 22Multiple input board block diagram Basic course I/O bus 1-41

Contents

Figures

ADDRESS & MIB Block

LATCH

Red led

CRDSL

ADDRESS

DATA

E.G. MICRO

SWICHES

16 lines (2Bytes) DATA IN

LATCH TRI

BUFFER STATE

IDENTIFIER CODE

COMPA

RATOR

STBIN

WRADR

INPUT

RDDAT CONTROL

SIGNALS

SRQEN

INPBF

RESET

Contents

Figures

H

H

Basic course I/O bus 1-41

Fig. 23Push button interface block diagram Basic course I/O bus 1-42

Contents

Figures

ADDRESS & PBI Block

LATCH

Red led

CRDSL

ADDRESS

DATA

PRIO DATA IN

ENC LATCH TRI

BUFFER STATE

PRIO

ENC

SET (PUSH

BUTTON

WRADR ACTIVE)

INPUT

RDDAT CONTROL IDENTIFIER

SIGNALS FLIP

SRQEN FLOP STBIN

PUSH BUTTONS ARRAY

INPBF

RESET (PUSH BUTTON INACTIVE)

RESET

Contents

Figures

H

H

Basic course I/O bus 1-42

Fig. 24Panel coder interface block diagram Basic course I/O bus 1-43

Contents

Figures

RHP-A4

+ R500 X407-10 X5-10 PCI - 1

A1 D4/10/11

154E (B0 - HEX)

B491 R501 X407-2 X5-2

B1

154E

D17

RATIO -

(B0-HEX)

+ R502 X407-11 X5-11

A2 D1/3/4

154E

B492 R503 X407-3 X5-3

B2

154E

CONTRAST -

+ R504 X407-12 X5-12

A3 D4/12

154E D13/15

B493 R505 X407-4 X5-4

B3

154E

BRIGHTNESS -

1 RHP-A1

+ X101-52

X401-52

X407-13 X5-13

A4 D2/5/6

3

B194 X101-51 X407-5 X5-5

B4 X401-51 D18/25

5

ZOOM - (B1-HEX)

IO - BUS

7 X407-14 X5-14

D2/13

D14/15

X407-6 X5-6

(B0-HEX

CIRCUIT

PC SELECT

COUNT +

X407-7 X5-7

D2/7/8

X407-8 X5-8

X101-45 X407-15

X401-45 X5-15 +5V

+5V TO D19/20

SHAFT D21/26

X101-41 X407-1

X401-41 X5-1 GND ENCODERS COUNT +

PC SELECT

X407-9 X5-9 CIRCUIT

GND (B0-HEX)

Contents

D30

Figures

EM4509-1

H

H

Basic course I/O bus 1-43

Basic course I/O bus 1-44

Contents

Figures

1.7 Switching on

• OLD CIRCUIT

• NEW CIRCUIT

Contents

Figures

H

H

Basic course I/O bus 1-44

Fig. 25Switching on circuit old Basic course I/O bus 1-45

Contents

Figures

P/A10

IGP SUPPLY XSX5- X10-

24 24

X79

X17- X1 X2 P/X1 MS-X4 X17 X1 IGP OVERLOAD

X2-10 X2-11 P/X1-52 MSX4-60 X17-36 VDB V127 37 23 23

X5-11

K5 X11-13 1 4 4 4 19 11

B24

1k

+24V 40 17 17 3 6 5 5 2 3 X5-3

1 2 X11-15

1k

X5-33 X2-33 B20 4 F13-6A X5-10

3 4 X11-14 MS-X5 2 12 6 6 35 10

SOB1 1k HVG

MSX4-59 IGPDR ODP

MBCR X19 X5-31 X2-31 V125 B22 7 13 14 X10-25 25 P/A10 MBCR -

IGP

VDBX17-3 X5-2 X2-2 23 X3 X20

ODP IN X10-20 20 SUPPLY

nc

VDB-X20 PVLK IGP VDB

PVP IN X10-16 16

nc VDB-X17 unlocks

V10 21 7 X5-7

MSX8-1 PVP LOCK X10-34 34 6 X17-40 V8

PVPDR 18 18 V18

X10-33 33 39 V2

RHP VDB VDB

MSX8-2 19 V1 X11-14 X4-22 X5-22

ODPDR 19 X203-6

K3 MS-X5 HEATER ODP

1 2 X9-9 9 1 MS-X8

MBCL RHP

MIB

X5-1 MBCR X17

SAFETY TRAFO X11-6 F12-4A 20 X46-6 X202-14

3 4 1 1 5 7 3

3

P/A12 220V X11-7 ODP 13 14 X9-20 Optional

P/A13-T1 220 V

8

T1 9

K4 13 9 186 9741 VDB

X17 P/A12 X6 X5 MSX3

MS-X5 VDB RHP MBCL MBCR PFD MBCR MBCL

T2 6 -7

X10-22 22 24 X11-32 ODPST X203-12 X34a-9 X1b-9 329 129 X1b-10 X34a-10 1 8

+ MBCR X1

1 2 3 4 5 6 X1-1

RHP MBCL 15 SEC DELAY POTMR 2 P/A11 7 -1

X2-3* To PBH

X10 VDB X4-1 X202-32 X46-12 +56V

K3 3 X1

X11-5

- -21 21 41 4 9 X2-4* Lens Supply (56 volt)

5 6 -15

-2 X10-33 VDB X2-32 X5-32 V3C 7 X1-2 4

X11-1 SOB1

31 32 0V 5

MS-X7 MBCR-X19 SEE LOCKING -10

F11-6A X9-23 23 6 X1-3 5

3 4 2 MATRIX 220 V P/A12

PVP

PVP 1 2 PVP 230V X9-21 21 1 X8 X7 T3

1 8

P/A12

F7 X11-9 P/A12-X2-1 X2-3 2

X11-8 P/A12-X2-2 P/A12-X2-4 3 30

F3 F4 F8 P/A8

4 9

PE1269/00 To P/A9

Z2 20AFILTER 7 26

* F10 3 5 3 4 X8-1 5 (filament supply) HT control

X8-2 6

220 V

* 1 4 1 2 X8-3

F9 5 30

2 -u 3 K6 P/A7

MAINS PANEL A2 SWITCH

ON DELAY

X11-18

X11-21 28

PE1264/40 To P/A9

(HT - supply) HT control

WALL SWITCH OR

MAINS PLUG

S1 P/A13 197 9733 192 5268 2

F1 1 2 Z1 20AFILTER (≈ = 0.3 sec) X11-16

F6 3 5 4

MS X2

~ 200-240V F2 3 4 F5 1 4

1

(X11-33)

X11-29

+ 8 / 12 / 16 + 7

2 X3-b8 1 5 4 54 MDT 0V

EARTH P/A5-X4 +S

3 4

X11-17 3 X921

P/A5 X3-z8 2 X2

+

X11-22 1 X922

1

44

2

43 -15V SUPPLY

X3-b18 3

X11-25 X11-19 2 X923

PE1130 - FILTER

13 14 192 5302

220 V X3-z18 4 6 5

21 22 X9-10 MSX6-10 MSX9-3 -S

X11-24 - 10/10 55A MDT -15V

20 / 24 / 28 -

43 44 X9-1 MSX6-1 MSX9-1 35 mm

K2 1

13 CAM. +8 / 12 / 16 +

K1 Motor 2 52A MDT +15V

T2 6 X11-10 P/A9-X55-1 X3-b8 1 5

+24VRS +S

4

14 HOLD X921

3 X11-11 132 P/A4 +

X3-z8 2 X2

R3 TMS

X11- X10-12 X203- X34a

X10 8 10 9 X11 11 29

2

X922

+15V SUPPLY

31 P/A9 X6 X3-b18 3

+24VRS 18 X46- -14 -32

C2

P/A9-X55-3 106 X923

PE1130 - FILTER

MSX5-12 0VRS 192 5302

1 8 X3-z18 4 6 3

18 -12 -S

R237

MBCL 5 X11-12 - 15/15 53 MDT 0V

108

111 20 / 24 / 28 -

Θ+ X1b -12 -14 P/A9-X55-2

X10

X17-30 X11- x11

1/7

K1 312 3 118 130 8 / 12 / 16 +

-28 28 X17-1 4 X202-4

20 51A MDT +5V

LPR-X34 130 131 T3 X1-6 1 5 2

+S

X203-19

4 X5-3

X10 5 AC SNS X3.24

-7 7 X46- PFD X5-1 X1-10 2 X2

X58 4V X3.28 +

X11-18 X202-18 19 321 322 1 8 SUPPLY

STND BY 23 wehnelt

X5-2 X1-26 3 MS X1

B1 X8-16 S37 (blow-off) REF MBCR-X1 motor X3.32

+5V

- FILTER

X11- X10 X14 192 5302

X11-33 X10-15 X1-30 4 6 3

0VRS 34 -6 6 RESTART P/A2 -S

VDB 8 10 9 11 29 PE1123 10/15 57 MDT 0V

X8-1

0VRS

MS-X5 MSX5-15 20 / 24 / 28 -

MDT 0V

X10 X29 MDT X58 RHP RHP

14 X17-33 ZEPHYR 50 17 13 14 X17-48

2 3 X9-3 MNSILK -14 X28 X201-2 X201-1

watercooler VDB

VDB-X17 RHP RHP P/A17

X209-1

X11-19 X203-20 X203-8 b14

MSX3 MSX6 S3 S1 R1 +

X10 X57 MBCL MBCL

3 -13 13 X17-20 X11-37 X202-37 X209-2 VDB-X11 X46-20 X46-8 PE1268

7 X9-7 27 8 7 26 RHP X202-19 X5 b20

MBCL MBCL

LIGHT 2

OFF ON X202-27 X202-8 X344-4 X34a-1 SPOTLIGHT X3

X11-26 X11-27 RHP X203-7 z8

MSX5 X202-7 X202-26 X4 SUPPLY 1

MOB1 14

X206 X209-3 MBCL MBCL-X49 MBCL MBCR MBCR 0V

-14 MNSONL

MBCR-X14 V205 X46-7 X34a-3 X1b-4 X1b-1 -

X6-106 X6-306 b26

2 SPOTLIGHT

X2-1

33 MBCR X1b 326 126 325 0.5 - 7V

X2-2 b30

X206-33

X209 X209

5 7 6 X209 MIB PFD

106 S201 S203 S2 MBCR - X17 125

-4 -10 ON OFF ST MBCR - X1 X2-3 b32

P/A9 HTS S202 BY

X5-14

HT control rack STAND-BY

X7 MBCR X1b-2

X4-14

107 RHP NOTE : FOR STEM

9 X209 8 X1- X5- MS X1

13 13 + 12

- A2 = A4 X202

106 306

0V RS V201 -6 X11-6 V120 HVG MBCL X34a-2 X3-b8 1 5

X2xx = X4xx VDB X1-8 8 X3.32 +S 56A MDT +24V

+24V SB (stand-by supply) MBCL X47-2 P/A3

PE1125 X3-z8 2

23 24 112 312 107 307 107 307 X15-5 V119 R41 X21 + P/A3-X2

0VRS X3.28 +24V SUPPLY

Wehnelt MS BUF HTR ACLO RCB (Stand By) - X3-b18

3

FILTER

MBB 6

Motor Unit X4 X5 X6 18 220 V X3-z18 4

-S

Contents

X3.24

- 8

58 MDT 0V

24

Figures

+24V (stand by supply)

H

H EM5605B

Basic course I/O bus 1-45

Fig. 26Switching on circuit new Basic course I/O bus 1-46

Contents

Figures

P/A10

IGP SUPPLY XSX5- X10-

24 24

X79

X17- P/X1 MS-X4 X17 X1 IGP OVERLOAD

X2-10 X2-11 MSX4-60 X17-36 VDB X1 X2

P/X1-52 V127 37 23 23 X5-11

K5 X11-13 1 4 4 4 19 11

1k

B24

+24V 40 17 17 3 6 5 5 2 3 X5-3

1 2 X11-15

1k

X5-33 X2-33 B20 4 F13-6A X5-10

3 4 X11-14 MS-X5 2 12 6 6 35 10

SOB1 1k HVG

MSX4-59 IGPDR ODP

MBCR X19 X5-31 X2-31 V125 B22 7 13 14 X10-25 25 P/A10 MBCR -

IGP X3

VDBX17-3 X5-2 X2-2 23 ODP IN X10-20 20 SUPPLY X20

nc

VDB-X20

PVLK IGP VDB

PVP IN X10-16 16

nc unlocks

VDB-X17 21

V10 7 X5-7

MSX8-1 PVP LOCK X10-34 34 6 X17-40 V8

PVPDR 18 18 V18

X10-33 33 39 V2

RHP VDB VDB

MSX8-2 19 V1 X11-14 X4-22 X5-22

ODPDR 19 X203-6

K3 MS-X5 HEATER ODP

1 2 X9-9 9 1 MS-X8

MBCL RHP

MIB

X5-1 MBCR X17

SAFETY TRAFO X11-6 F12-4A 20 X46-6 X202-14

3 4 1 1 5 7 3

3

P/A12 220V X11-7 ODP 13 14 X9-20 Optional

P/A13-T1 220 V

8

T1 9 K4 13 9 186 9741 VDB

X17 P/A12 X6 X5 MSX3

MS-X5 VDB RHP MBCL MBCR PFD MBCR MBCL

T2 6 -7

X10-22 22 24 X11-32 ODPST X203-12 X34a-9 X1b-9 329 129 X1b-10 X34a-10 1 8

+ MBCR X1

1 2 3 4 5 6 X1-1

RHP MBCL 15 SEC DELAY POTMR 2 P/A11 7 -1 To PBH

VDB X4-1 X202-32 X46-12 X2-3*

K3 X10 3 +56V X1

X11-5

- -21 21 41 4 9 X2-4* Lens Supply (56 volt)

5 6 -15

-2 X10-33 VDB X2-32 X5-32 V3C 7 X1-2 4

X11-1 SOB1 5

31 32 0V SEE LOCKING

F11-6A MS-X7 MBCR-X19 -10

X9-23 23 MATRIX 220 V 6 X1-3 5

3 4 2 P/A12

PVP

PVP 1 2 PVP 230V X9-21 21 1 X8 X7 T3

1 8

P/A12

F7 X11-9 P/A12-X2-1 X2-3 2

X11-8 P/A12-X2-2 P/A12-X2-4 3 30

F3 F4 F8 P/A8

4 9

PE1269/00 To P/A9

Z2 20AFILTER 7 26

* F10 3 5 3 4 X8-1 5 (filament supply) HT control

X8-2 6

220 V

* 1 4 1 2 X8-3

F9 5 30

2 -u 3 K6 P/A7

MAINS PANEL A2 SWITCH

ON DELAY

X11-18

28

PE1264/40 To P/A9

X11-21 (HT - supply) HT control

WALL SWITCH OR

MAINS PLUG

S1 P/A13 197 9733 192 5268 2

F1 1 2 Z1 20AFILTER (≈ = 0.3 sec) X11-16

F6 3 5 4

MS X2

~ 200-240V F2 3 4 F5 1 4

1

(X11-33)

X11-29

+8 / 12 / 16 + 7

2 X3-b8 1 5 4 54 MDT 0V

EARTH P/A5-X4 +S

3 4

X11-17 3 X921

P/A5 X3-z8 2 X2

+

1 2 X11-22 1 X922 SUPPLY

44 43 -15V X3-b18 3

X11-25 X11-19 2 X923

PE1130 - FILTER

13 14 192 5302

220 V X3-z18 4 6 5

21 22 X9-10 MSX6-10 MSX9-3 -S

X11-24 - 10/10 55A MDT -15V

20 / 24 / 28 -

43 44 X9-1 MSX6-1 MSX9-1 35 mm

K2 1

13 CAM. +8 / 12 / 16 +

K1 Motor 2 52A MDT +15V

T2 6 X11-10 P/A9-X55-1 X3-b8 1 5

+24VRS +S

4

14 HOLD X921

3 X11-11 132 P/A4 +

X3-z8 2 X2

R3 TMS

X11- X10-12 X34a

X10 8 10 9 X11 11 29

2

X922

+15V SUPPLY

31 X203- P/A9 X6

- X3-b18

+24VRS -32 P/A9-X55-3 106 X923 3 FILTER

18 X46- -14 C2 PE1130

MSX5-12 0VRS 192 5302

1 8 X3-z18 4 6 3

18 -12 -S

R237

MBCL 5 X11-12 - 15/15 53 MDT 0V

108

111 20 / 24 / 28 -

Θ+ X1b -12 -14 P/A9-X55-2

X17-30 X11- x11

X10 K1 312 3 118 130 8 / 12 / 16 + 1/7

-28 28 X17-1 4 X202-4

20 51A MDT +5V

LPR-X34 130 131 T3 X1-6 1 5 2

+S

X203-19

4 X5-3

X10 5 AC SNS X3.24

-7 7 X46- PFD X5-1 X1-10 2 X2

X58 4V X3.28 +

X11-18 X202-18 19 321 322 1 8 SUPPLY

STND BY 23 wehnelt

- X1-26 MS X1

X5-2 3

REF MBCR-X1 motor X3.32 FILTER

B1 X8-16 S37 (blow-off) +5V 192 5302

X11- X10 X14 X11-33 X10-15 X1-30 4 6 3

0VRS 34 -6 6 RESTART P/A2 -S

VDB 8 10 9 11 29 PE1123 10/15 57 MDT 0V

X8-1

0VRS

MS-X5 MSX5-15 20 / 24 / 28 -

MDT 0V

X10 X29 MDT X58 RHP RHP

14 X17-33 ZEPHYR 50 17 13 14 X17-48

2 3 X9-3 MNSILK -14 X28 X201-2 X201-1

watercooler VDB

VDB-X17 RHP RHP P/A17

X209-1

X11-19 X203-20 X203-8 b14

MSX3 MSX6 S3 S1 R1 +

X10 X57 MBCL MBCL

3 -13 13 X17-20 X11-37 X202-37 X209-2 VDB-X11 X46-20 X46-8 PE1268

7 X9-7 27 8 7 26 RHP X202-19 X5 b20

MBCL MBCL

LIGHT 2

OFF ON X202-27 X202-8 X344-4 X34a-1 SPOTLIGHT X3

X11-26 RHP X203-7 z8

X11-27 MSX5 X202-7 X202-26 X4 SUPPLY 1

MOB1 X206 X209-3 MBCL MBCL-X49 MBCL MBCR MBCR 0V

14 -14 MNSONL

MBCR-X14 V205 X46-7 X34a-3 X1b-4 X1b-1 -

X6-106 X6-306 b26

2 SPOTLIGHT

MNSONhold X2-1

33 MBCR X1b 326 126 325 0.5 - 7V

X2-2 b30

X206-33 Standby-hold X209 X209

5 7 6 X209 MIB PFD

106 S201 S203 S2 MBCR - X17

-4 -10 ON OFF ST 125 X2-3 b32

MBCR - X1

P/A9 HTS S202 BY

X5-14

HT control rack STAND-BY

X7 MBCR X1b-2

107 RHP NOTE : FOR STEM

9 X209 8 X4-14 X1- X5- MS X1

X202

13 13 + 12

- A2 = A4

106 306

0V RS V201 -6 X11-6 V120 HVG MBCL X34a-2 X3-b8 1 5

X2xx = X4xx VDB X1-8 8 X3.32 +S 56A MDT +24V

+24V SB (stand-by supply) MBCL X47-2 P/A3

PE1125 X3-z8 2

23 24 112 312 107 307 107 307 X15-5 V119 R41 + P/A3-X2

X21

0VRS X3.28 +24V SUPPLY

Wehnelt MS BUF HTR ACLO RCB (Stand By) -

X3-b18 3

FILTER

MBB 6

Motor Unit X4 X5 X6 18 220 V X3-z18 4

-S

Contents

X3.24

- 8

58 MDT 0V

24

Figures

+24V (stand by supply)

H

H

EM5605Bmod

Basic course I/O bus 1-46

You might also like

- Hammond Service Manual A A-100 BA BC BCV BV B2 B3 C CV C2 C2 TextDocument220 pagesHammond Service Manual A A-100 BA BC BCV BV B2 B3 C CV C2 C2 Textbubbapebi100% (3)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Week3Document11 pagesWeek3T GUNA guna0% (1)

- Wavestar Dacs 4/4/1 Introduction and O&M: Patrick Wu Qacc &tsoDocument38 pagesWavestar Dacs 4/4/1 Introduction and O&M: Patrick Wu Qacc &tsoDaiAnShengNo ratings yet

- Volvo Truck FM Euro5 Service ManualDocument20 pagesVolvo Truck FM Euro5 Service Manualrobby100% (54)

- Technical Information LTM 1055/1Document46 pagesTechnical Information LTM 1055/1josselin quatrain100% (2)

- Connector Industry: A Profile of the European Connector Industry - Market Prospects to 1999From EverandConnector Industry: A Profile of the European Connector Industry - Market Prospects to 1999No ratings yet

- BMK 1055 1 enDocument82 pagesBMK 1055 1 enDavidVazquez100% (9)

- Handleiding Ic4c Incosa Feb2014 v4 enDocument20 pagesHandleiding Ic4c Incosa Feb2014 v4 enLeninNo ratings yet

- 02 Transmission Media PROFIBUSDocument22 pages02 Transmission Media PROFIBUSIsai AnguianoNo ratings yet

- Electrical 999 CumminsDocument39 pagesElectrical 999 CumminsMohamed FathyNo ratings yet

- Philips Chassis L03.1U AA 312278513933Document56 pagesPhilips Chassis L03.1U AA 312278513933Mendez FreddyNo ratings yet

- SSB Manual - Areva - Test BoxDocument52 pagesSSB Manual - Areva - Test Boxירדן רובינשטייןNo ratings yet

- Philips Lc4.1l-Aa Chassis 20pf8946-78 23pf5321-78 23pf8946-78 23pf8946m-78 SM PDFDocument55 pagesPhilips Lc4.1l-Aa Chassis 20pf8946-78 23pf5321-78 23pf8946-78 23pf8946m-78 SM PDFfanchheizNo ratings yet

- Philips Chassis L01.2e Ab PDFDocument60 pagesPhilips Chassis L01.2e Ab PDFIoannis PitsoulisNo ratings yet

- Philips Chassis TC2.1A AA 312278513690 - enDocument49 pagesPhilips Chassis TC2.1A AA 312278513690 - enCaptain444No ratings yet

- 9537 Chassis L03.6LCA Manual de Servicio PDFDocument38 pages9537 Chassis L03.6LCA Manual de Servicio PDFOmar BustoNo ratings yet

- Philips 14pt3005 55 Chassis L03.2laa SMDocument42 pagesPhilips 14pt3005 55 Chassis L03.2laa SMLupita Motta TobíasNo ratings yet

- 09051111036535Document81 pages09051111036535PedroNo ratings yet

- 14pt3822 69 PhilipsDocument35 pages14pt3822 69 PhilipsHanif Rathore PrinceNo ratings yet

- Lab Manual-1st TermDocument12 pagesLab Manual-1st Termcmp2012No ratings yet

- Basic Design PDFDocument26 pagesBasic Design PDFLeTung95No ratings yet

- Philips L03 SSDocument60 pagesPhilips L03 SSMarco Antonio100% (12)

- Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesLesson Plan Microprocessor and Micro COntrollerRaja Pirian0% (2)

- And8009 DDocument37 pagesAnd8009 DMartin WhiteNo ratings yet

- Magnavox 32MF338BDocument93 pagesMagnavox 32MF338BJames SouthNo ratings yet

- Philips 32pw8422/77 Chassis L05laaDocument86 pagesPhilips 32pw8422/77 Chassis L05laaRicardo E. Roldán100% (1)

- Tpm4.1ela 689Document64 pagesTpm4.1ela 689Anonymous 3SCkL0No ratings yet

- FT-2200 Serv F6DBL 1993Document125 pagesFT-2200 Serv F6DBL 1993Marcos DanilaviciusNo ratings yet

- ABB CS31 FPR3312101R1022 DatasheetDocument6 pagesABB CS31 FPR3312101R1022 DatasheetChristian BacconnaisNo ratings yet

- DIGITAL Course Plan FinalDocument10 pagesDIGITAL Course Plan FinalponniNo ratings yet

- EC8691 Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesEC8691 Lesson Plan Microprocessor and Micro COntrollerlauro eugin brittoNo ratings yet

- PHILIPS TV 20MS2331-17 Chassis L03.2UAADocument53 pagesPHILIPS TV 20MS2331-17 Chassis L03.2UAAManuel MartinezNo ratings yet

- 11AK19P5 SCHDocument44 pages11AK19P5 SCHtodorloncarskiNo ratings yet

- 42PFL4007G-78 Service+fonte PDFDocument74 pages42PFL4007G-78 Service+fonte PDFPedro AfonsoNo ratings yet

- 42PFL4007G-78 Service+fonte PDFDocument74 pages42PFL4007G-78 Service+fonte PDFAntonio MacedoNo ratings yet

- 1.9 Block Diagram: Philips SemiconductorsDocument1 page1.9 Block Diagram: Philips SemiconductorsutsabNo ratings yet

- PSA Unit-1.v3Document26 pagesPSA Unit-1.v3yvkrishnareddyNo ratings yet

- Delny Galindo: PPMV-Service Septiembre 2015Document13 pagesDelny Galindo: PPMV-Service Septiembre 2015cachiletNo ratings yet

- Different Control Mode For Buck or Boost TopologyDocument15 pagesDifferent Control Mode For Buck or Boost TopologyJesus Honorio Alvarez PaezNo ratings yet

- SN54F245, SN74F245 Octal Bus Transceivers With 3-State OutputsDocument22 pagesSN54F245, SN74F245 Octal Bus Transceivers With 3-State OutputsrectibeiraNo ratings yet

- 42pfl5609 32pfl5409Document90 pages42pfl5609 32pfl5409dibbenduNo ratings yet

- 32PFL3605 Tpm4.1e - LaDocument64 pages32PFL3605 Tpm4.1e - Laismosch100% (1)

- DE - UNIT 2 - Dec 2018 UpdatedDocument41 pagesDE - UNIT 2 - Dec 2018 UpdatedsampritiNo ratings yet

- TCM3.2L La 22PFL1234 D10 32PFL5604 78 32PFL5604 77 42PFL5604 77Document67 pagesTCM3.2L La 22PFL1234 D10 32PFL5604 78 32PFL5604 77 42PFL5604 77castronelsonNo ratings yet

- GS33J05H20 01enDocument2 pagesGS33J05H20 01enkjh346gmail.comNo ratings yet

- Colour Television Chassis AA: C and Supply Voltage OverviewDocument72 pagesColour Television Chassis AA: C and Supply Voltage OverviewCompilexNo ratings yet

- 20PT1547.01, Te1.1e Aa (PT92P)Document50 pages20PT1547.01, Te1.1e Aa (PT92P)khafjiNo ratings yet

- 14 PT 150112Document78 pages14 PT 150112Javier Alejandro Sevilla LinaresNo ratings yet

- LensesDocument49 pagesLensesManuel CasanovaNo ratings yet

- PreinstDocument23 pagesPreinstManuel CasanovaNo ratings yet

- High TensionDocument11 pagesHigh TensionManuel CasanovaNo ratings yet

- Overview of Alignment Procedures CM12/120 Microscopes: LegendDocument49 pagesOverview of Alignment Procedures CM12/120 Microscopes: LegendManuel CasanovaNo ratings yet

- Digital Logic Design Exp. No. 10Document20 pagesDigital Logic Design Exp. No. 10Abbas RaxaNo ratings yet

- IC 045 Embedded Sys Design PPT 5Document51 pagesIC 045 Embedded Sys Design PPT 5RajendraPrasadSahuNo ratings yet

- Digital Circuit Projects by Dr. Charles W. Kann.Document122 pagesDigital Circuit Projects by Dr. Charles W. Kann.Svh van HeerdenNo ratings yet

- Seminar Report On VLSIDocument21 pagesSeminar Report On VLSIGaurav Jaiswal75% (4)

- Master Slave Flip FlopDocument3 pagesMaster Slave Flip FloplakshmiraniNo ratings yet

- FPGA Signal Processing For Sonar ApplicationsDocument4 pagesFPGA Signal Processing For Sonar ApplicationsthmmyNo ratings yet

- Stm32f303re PDFDocument173 pagesStm32f303re PDFmeeramytuNo ratings yet

- Design of High Speed Pipeline ADC: Estec February 4-5, 2004Document29 pagesDesign of High Speed Pipeline ADC: Estec February 4-5, 2004Niamat KhanNo ratings yet

- Computer and Interfacing Chapter Six Pin and Clock GeneratorDocument78 pagesComputer and Interfacing Chapter Six Pin and Clock GeneratormigadNo ratings yet

- CD4553Document9 pagesCD4553oscarNo ratings yet

- Data Sheet: HEF40192B MSIDocument9 pagesData Sheet: HEF40192B MSIvanmarteNo ratings yet

- Flip-Flops: Lecturer Uzma Hasan, CSE Department, MISTDocument21 pagesFlip-Flops: Lecturer Uzma Hasan, CSE Department, MISTRafinNo ratings yet

- User's Manual ET-8LSDDocument5 pagesUser's Manual ET-8LSDRoberto PasicNo ratings yet

- MPMC Assignment-1Document7 pagesMPMC Assignment-113Panya CSE2No ratings yet

- Xilinx Training CoursesDocument16 pagesXilinx Training CoursesM Madan GopalNo ratings yet

- Design and Analysis of FPGA Based 32 Bit ALU UsingDocument5 pagesDesign and Analysis of FPGA Based 32 Bit ALU UsingEng:ehab AlmkhlafiNo ratings yet

- UTS Sistem Pengaturan KendaliDocument19 pagesUTS Sistem Pengaturan KendaliImam IbrahimNo ratings yet

- Dte Micro Project OriginalDocument14 pagesDte Micro Project Originaljhjh25% (4)

- Module 5 PDFDocument133 pagesModule 5 PDFDeepak KumarNo ratings yet

- Unit09.programmable Logic Devices EnglishDocument20 pagesUnit09.programmable Logic Devices EnglishRufo LemurNo ratings yet

- Embedded Systems Programming: Prof. Dr. Hassan AlansaryDocument10 pagesEmbedded Systems Programming: Prof. Dr. Hassan AlansaryAbdallah AdelNo ratings yet

- Memory and Programmable LogicDocument47 pagesMemory and Programmable Logicdewantosatrio50% (2)

- TransistorsDocument7 pagesTransistorsDan Jeric Arcega RustiaNo ratings yet

- Programming Microcontroller AT89C51Document6 pagesProgramming Microcontroller AT89C51Vyan DexterNo ratings yet

- Digital Signal Processing Unit V: DSP ProcessorDocument20 pagesDigital Signal Processing Unit V: DSP ProcessorKumar ManiNo ratings yet

- I/O Ports in AVR: The AVR Microcontroller and Embedded SystemsDocument23 pagesI/O Ports in AVR: The AVR Microcontroller and Embedded SystemsLuqmanMaraabaNo ratings yet

- GrlibDocument85 pagesGrlibshrikul.joshi100% (1)

- KE1xFP100M168SF0 PDFDocument99 pagesKE1xFP100M168SF0 PDFyunus emre KılınçNo ratings yet

- Interfacing Digital-To-Analog Converter To 8086 Using 8255Document4 pagesInterfacing Digital-To-Analog Converter To 8086 Using 8255C S75% (4)