Professional Documents

Culture Documents

Digital Electronics Question Bank

Uploaded by

ponniOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Electronics Question Bank

Uploaded by

ponniCopyright:

Available Formats

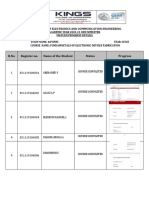

FORMAT : QP09 KCE/DEPT.

OF ECE

DEPARTMENT OF ELECTRONICS AND COMMUNICATION

ENGINEERING

SUBJECT : DIGITAL ELECTRONICS

SEMESTER : III

QUESTION BANK (EC8392)

(Version- 2)

PREPARED BY

Mr.A.HERALD, AP/ ECE

DE -5-1 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

EC 8392 DIGITAL ELECTRONICS L TPC

3 0 0 3

UNIT I DIGITAL FUNDAMENTALS 9

Number Systems – Decimal, Binary, Octal, Hexadecimal, 1’s and 2’s complements, Codes –

Binary, BCD, Excess 3, Gray, Alphanumeric codes, Boolean theorems, Logic gates, Universal

gates, Sum of products and product of sums, Minterms and Maxterms, Karnaugh map

Minimization and Quine-McCluskey method of minimization.

UNIT II COMBINATIONAL CIRCUIT DESIGN 9

Design of Half and Full Adders, Half and Full Subtractors, Binary Parallel Adder – Carry look

ahead Adder, BCD Adder, Multiplexer, Demultiplexer, Magnitude Comparator, Decoder,

Encoder, Priority Encoder.

UNIT III SYNCHRONOUS SEQUENTIAL CIRCUITS 9

Flip flops – SR, JK, T, D, Master/Slave FF – operation and excitation tables, Triggering of FF,

Analysis and design of clocked sequential circuits – Design - Moore/Mealy models, state

minimization, state assignment, circuit implementation – Design of Counters- Ripple Counters,

Ring Counters, Shift registers, Universal Shift Register.

UNIT IV ASYNCHRONOUS SEQUENTIAL CIRCUITS 9

Stable and Unstable states, output specifications, cycles and races, state reduction, race free

assignments, Hazards, Essential Hazards, Pulse mode sequential circuits, Design of Hazard free

circuits.

UNIT V MEMORY DEVICES AND DIGITAL INTEGRATED CIRCUITS 9

Basic memory structure – ROM -PROM – EPROM – EEPROM –EAPROM, RAM – Static and

dynamic RAM - Programmable Logic Devices – Programmable Logic Array (PLA) -

Programmable Array Logic (PAL) – Field Programmable Gate Arrays (FPGA) - Implementation

of combinational logic circuits using PLA, PAL.

Digital integrated circuits: Logic levels, propagation delay, power dissipation, fan-out and fan-

in, noise margin, logic families and their characteristics-RTL, TTL, ECL, CMOS

TOTAL: 45 PERIODS

SIGNATURE OF STAFF INCHARGE HOD/ECE

Mr. A.Herald

DE -5-2 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

COURSE PLAN

COURSE PLAN

Sub. Code : EC 8392 Branch / Year / Sem : B.E ECE / II / III

Sub.Name : Digital Electronics Batch : 2018-2022

Staff Name : Mr. A.Herald Academic Year : 2019-20 (ODD)

COURSE OBJECTIVE

1. To present the Digital fundamentals, Boolean algebra and its applications in digital

systems.

2. To familiarize with the design of various combinational digital circuits using logic gates.

3. To introduce the analysis and design procedures for synchronous and asynchronous

sequential circuits.

4. To explain the various semiconductor memories and related technology.

5. To introduce the electronic circuits involved in the making of logic gates.

TEXT BOOK

T1: M. Morris Mano and Michael D.Ciletti, “Digital Design”, 5th Edition, Pearson 2014.

REFERENCE BOOKS

R1: Charles H.Roth. “Fundamentals of Logic Design”, 6th Edition, Thomson Learning, 2013.

R2: Anil K.Maini “Digital Electronics”, Wiley, 2014.

R3: S.Salivahanan and S.Arivazhagan“Digital Electronics”, Ist Edition, Vikas Publishing House

pvt Ltd, 2012.

R4: J.S Katre and G.C.Patil, “Digital electronics”, Macmillan Publishers India Ltd, 2011.

WEB RESOURCES

W1. www.cse.yorku.ca/~mack/1011/01.NumberSystems.ppt (Topic. No:01)

W2. http://www.ee.surrey.ac.uk/Projects/Labview/minimisation/tabular.html

(Topic. No:10)

W3. http://www.slideshare.net/jayanshugundaniya9/digital-electronics-multiplexers-

demultiplexers (Topic.No:16)

W4. nptel.ac.in/video.php?subjectId=117106086 (Topic.No:20)

W5. http://freevideolectures.com/Course/2310/Digital-Circuits-and-Systems/24

(Topic.No:22)

W6. www.dauniv.ac.in/downloads/Digitalsystems_PPTs/DigdesignCH19L5.pdf

(Topic.No:30& 31)

W7.www.iitk.ac.in/eclub/summercamp/Courses/Special

%20Topics/.../SemiMem_lec1.ppt

(Topic.No:33)

DE -5-3 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

Topic Topic Books for Page No. Teaching No. of Cumulative

No Reference Methodology Hours No. of

Required periods

UNIT I DIGITAL FUNDAMENTALS (9+1)

1. Number Systems – T1 1-6 BB 1 1

Decimal, Binary R2 4-5

W1 PPT

2. Octal, Hexadecimal T1 7-9 BB 1 2

R2 4-5

3. 1’s and 2’s complements T1 9-11 BB 1 3

R2 5-6

4. Codes – Binary, T1 18-22 BB 1 4

Binary coded Decimal

5. Excess 3, Gray and T1 23-26 BB 1 5

Alphanumeric codes R2 21-37

6. Boolean theorems, Logic R1 39-43 BB 1 6

gates, Universal gates

7. Sum of products and R1 98 BB 1 7

product of sums

8. Minterms and Maxterms R1 97-99 BB 1 8

9. Karnaugh map R1 123- BB 1 9

Minimization 153

10. Quine-McCluskey R1 167- BB 1 10

method of minimization. W2 176 PPT

LEARNING OUTCOME

At the end of unit, students should be able to

Use various number conversions and arithmetic operations.

Realize Quine - Mc Cluskey method of minimization

Identify the Minimimum Boolean expressions using Karnaugh map

UNIT II COMBINATIONAL CIRCUIT DESIGN (9+1)

11. Design of Half adder and T1 132-138 BB 1 11

Full Adder

12. Half subtractor, Full T1 139-143 BB 1 12

subtractor

13. Binary Parallel adder R2 245 BB 1 13

14. Carry Look Ahead adder R2 254-259 BB 1 14

15. BCD adder R2 246-253 BB 1 15

16. Multiplexer & T1 158-162 BB 2 17

Demultiplexer R2 269-280

W3 PPT

17. Magnitude Comparator T1 148-149 BB 1 18

18. Decoder , Encoder T1 150-156 BB 1 19

19. Priority Encoder R2 280-284 BB 1 20

LEARNING OUTCOME

At the end of unit, students should be able to

Outline knowledge on Multiplexer& Demultiplexer

Design adder and subtractor.

State the working of BCD adder, fast adder & priority encoder.

DE -5-4 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

Topic Topic Books for Page No. Teaching No. of Cumulative

No Reference Methodology Hours No. of

Required periods

UNIT III SYNCHRONOUS SEQUENTIAL CIRCUITS (9+1)

20. Flip-flops - SR, JK, D, T, T1 196-201 BB 2 22

and Master-Slave, W4 NPTEL

operation and excitation

tables.

21. Triggering of Flip flop T1 201-203 BB 1 23

22. Analysis and design of BB 2 25

T1 PPT

clocked sequential 204-216

W5

circuits.

23. Design of Moore/Mealy T1 234-250 BB 2 27

models, state R3 297-321

minimization, state

assignment, circuit

implementation.

24. Design of Counters T1 271-280 BB 1 28

25. Ripple Counters, T1 266-270 BB 1 29

Ring Counters

26. Shift registers, Universal T1 255-264 BB 1 30

Shift Register.

LEARNING OUTCOME

At the end of unit, students should be able to

Design sequential circuits using various flip flops.

Describe and Compare the shift registers.

Analyze & Compare the functioning of moore and mealy models.

UNIT IV ASYNCHRONOUS SEQUENTIAL CIRCUITS (9+1)

27. Stable and Unstable T1 435-450 BB 2 32

states, output R3 388-397

specifications

28. cycles and races T1 463-466 BB 1 33

29. state reduction, race free T1 466-468 BB 2 35

assignments,

30. Hazards, Essential T1 469-474 PPT 1 36

Hazards, W6

31. Pulse mode sequential R4 12.1- PPT 2 38

circuits, W6 12.44 BB

32. Design of Hazard free T1 343-379 BB 2 40

circuits.

LEARNING OUTCOME

At the end of unit, students should be able to

Design the pulse mode sequential circuits

Describe the technology behind Hazard Free Switching circuits

Demonstrate the cycles , races and race free assignments.

Topic Topic Books for Page No. Teaching No. of Cumulative

DE -5-5 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

No Reference Methodology Hours No. of

Required periods

UNIT V MEMORY DEVICES AND DIGITAL INTEGRATED CIRCUITS (9+1)

33. Basic memory structure T1 315-320 PPT 2 42

– ROM -PROM – EPROM W7

– EEPROM –EAPROM,

34. RAM – Static and T1 299-312 BB 1 43

dynamic RAM

35. Programmable Logic T1 321-324 BB 1 44

Devices – Programmable

Logic Array (PLA) -

36. Programmable Array T1 325-328 BB 1 45

Logic (PAL) – Field R2 317-333

Programmable Gate

Arrays (FPGA)

37. Implementation of T1 329-341 BB 1 46

combinational logic

circuits using PLA, PAL.

38. Digital integrated T1 60-67 BB 1 47

circuits: Logic levels,

propagation delay,

power dissipation, fan-

out and fan-in, noise

margin.

39. logic families and their T1 67-69 BB 1 48

characteristics-RTL,

40. TTL, ECL T1 69-71 BB 1 49

R2 124-150

41. CMOS T1 71-72 BB 1 50

R2 151-164

LEARNING OUTCOME

At the end of unit, students should be able to

Analyze & Compare the functioning of memories

Outline knowledge on Programmable Logic devices.

Describe the logic families and their characteristics.

COURSE OUTCOME

At the end of the course, the students will be able to

Use digital electronics in the contemporary world.

Design various Combinational digital circuits using logic gates.

Do the analysis and design procedures for synchronous and asynchronous sequential

circuits.

Use the semiconductor memories and related technology.

Use electronic circuits involved in the design of logic gates.

CONTENT BEYOND THE SYLLABUS

1. Study of Advanced Field Programmable Gate Array system.

INTERNAL ASSESSMENT DETAILS

DE -5-6 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

ASST. NO. I II MODEL

Topic Nos. 1-15 16-26 1-41

Date

ASSIGNMENT DETAILS

ASSIGNMENT I II

Topic Nos. for

1-15 PCE

reference

Deadline

ASSIGNMENT DETAILS:

ASSIGNMENT I (20 Marks) ASSIGNMENT II (20 Marks)

(Before AT – I) (Before AT – II)

Topic for Reference: (1-15) PCE Activity

Part-A Activity 1: Case study presentation

1. State and prove Demorgans theorem. Synchronous sequential circuits

2. State principle of duality. Programmable logic devices.

3. Prove that ABC + ABC' + AB'C + A'BC

Activity 2: Quiz

= AB + AC + BC.

Google classroom

4. Draw the logic diagram and truth table

Testmoz

for Half adder and half subtractor.

5. What do you mean by weighted code? Activity 3: Think break (problem solving)

Part-B Counter problems

1. Using Quine- McClusky method simplify Moore & Mealey problems

the given function :

F(A,B,C,D)=∑m(0,2,3,5,7,11,13,14). Activity 4: APH

2. Explain the operation of Full adder, CPLD & FPGA

Full subtractor and carry look ahead MUX, DEMUX, Encoders & Decoders

adder. Activity 5: Poster Presentation

3.Using K map find the MSP form of Flip-flops –SR,JK,D,T

F=(0-3,12-15) +d(7,11). Pulse mode Sequential circuits

Activity 6: Virtual lab exercise

Multiplexers and Demultiplexers

Code converters

Prepared by Verified By

Mr.A.Herald HOD/ECE

Approved by

PRINCIPAL

REVIEW SHEET

After Completion of syllabus

DE -5-7 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

Faculty experience in handling / covering syllabus

Unit I :

Unit II :

Unit III :

Unit IV :

Unit V :

Difficulties (if any)

Feedback on University Question Paper

SIGNATURE OF STAFF HOD/ECE

DE -5-8 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

GENERAL GUIDELINES

Course Objectives are brief, clear statements that describe the desired learning of

instruction; i.e., the specific skills, values, and attitudes students are intended to

acquire. Three learning objectives are

What do you want your graduates to know?

What do you want your graduates to think or care about?,

What do you want your graduates to be able to do?

Learning Outcome are set of statements setting out what the participants should be

able to do / understand by the end of the Unit. Learning Outcomes are statements that

describe significant and essential learning that learners have achieved, and can reliably

demonstrate at the end of a course or program

Learning outcome muse be clear and precise, learner-oriented, realistic and achievable.

(Words such as State, Describe, Explain, Use, Identify, Analyze, Compare, Demonstrate,

Plan, Develop can be used)

Course Outcome are set of statements setting out what the participants should be able

to do / understand at the end of the course.

Teaching Methodology includes

DE -5-9 KCE/ECE/QB/II YR/DE

FORMAT : QP09 KCE/DEPT. OF ECE

o BB - Black board o Sem - Seminar

o CBT - Computer Based o GL - Guest Lecture

Tutorial o IV - Industrial visit

o PPT - Power Point based learning

o V - Video o CS - Case study

o Demo - Demonstration o Tut - Tutorial

o OHP - Over Head o NPTEL- National

Projector usage Programme on

(OHP slides) Technology

Enabled Learning

Minimum of 1 NPTEL class per course should be included and executed.

Assignment dates shall be fixed in consent with all 6 subject faculties so as to give

equal time slot balance for the students. Assignment dates should be prior to

Assessment & Model Exams.

Course plan Pages 1 to 6 shall be included in Question bank

Review sheet is experience summary sheet to be included in the course file for

future reference (staff has to fill in the sheet after completing the course) & need not

be included in Question Bank.

Updated Question Bank shall be given appropriate version numbers

GUIDELINES FOR ASSIGNMENT

1. Student Groups shall be formed (Eg. Class strength :50, each group comprising 10

members, totaling 5 groups). As per the number of groups, Assignment question I, II

has to be identified by faculty. (5 groups means, 5 questions for Assignment I, II).

Group 1 shall be allotted Qn 1 from Assignment I & Qn. 1 from Assignment II and

likewise the other groups.

2. For Assignment I, each group has to attend 1 question in detail (Min. of 8 pages).

Marks will be credited for Assessment I.

3. For Assignment II, as per the specification mentioned student groups has to develop

model/simulate the assigned task. Work has to documented individually (Title,

Objective, Description, Requirement, Implementation details, Inference).

4. Award of marks :Document-05, Presentation-05, Demo-10

5. Marks secured in Document, Presentation will be credited for Assessment-II.

6. Work has to be Demonstrated to the faculty in-charge for award of marks & credited

for Model exam.

7. Progress of Assignment II will be monitored through faculty-batch interaction.

DE -5-3 KCE/ECE/QB/II

YR/DE

You might also like

- B.tech Cse VTR Uge2021 de SyllabusDocument4 pagesB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiNo ratings yet

- 19EC303-DPSD - ECE-Updated 03.01.2020 PDFDocument4 pages19EC303-DPSD - ECE-Updated 03.01.2020 PDFMulla SarfarazNo ratings yet

- Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesLesson Plan Microprocessor and Micro COntrollerRaja Pirian0% (2)

- MPMC CP FinalDocument9 pagesMPMC CP Finalsimman8371029No ratings yet

- Digital Electronics Course OverviewDocument41 pagesDigital Electronics Course Overviewbad boiiNo ratings yet

- Microprocessors and Microcontrollers Question BankDocument11 pagesMicroprocessors and Microcontrollers Question BankheraldNo ratings yet

- Subject: Ec8501 Digital Communication: Department of Electronics and Communication EngineeringDocument6 pagesSubject: Ec8501 Digital Communication: Department of Electronics and Communication EngineeringheraldNo ratings yet

- Department of Electronics and Communication Engineering: Prepared byDocument6 pagesDepartment of Electronics and Communication Engineering: Prepared byheraldNo ratings yet

- EC8691 Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesEC8691 Lesson Plan Microprocessor and Micro COntrollerlauro eugin brittoNo ratings yet

- Digital ElectronicsDocument125 pagesDigital ElectronicsAditya SharmaNo ratings yet

- R23 YCA2002Document4 pagesR23 YCA2002munnisujliNo ratings yet

- Digital Electronics Course OutlineDocument15 pagesDigital Electronics Course OutlineYash KuncolienkerNo ratings yet

- CS3351 - Digital Principles and Computer Organization Course Objectives and OutcomesDocument7 pagesCS3351 - Digital Principles and Computer Organization Course Objectives and Outcomesmagy1989No ratings yet

- EE206 DigitalSystemDesignDocument2 pagesEE206 DigitalSystemDesignRajalearn2 Ramlearn2No ratings yet

- De&mp Unit - 2Document35 pagesDe&mp Unit - 2Mahesh BabuNo ratings yet

- Efficient VLSI Signal Processing ArchitecturesDocument8 pagesEfficient VLSI Signal Processing ArchitecturesRaja PirianNo ratings yet

- Digital Design: Cs/Eee/Ece /instr F215Document34 pagesDigital Design: Cs/Eee/Ece /instr F215SIDDHANT RAVINDRA KULKARNINo ratings yet

- Subject: Electronic Devices: Department of Electronics and Communication EngineeringDocument9 pagesSubject: Electronic Devices: Department of Electronics and Communication EngineeringAnonymous 9WJ7YeGNo ratings yet

- WC Lesson PlanDocument7 pagesWC Lesson PlanParanthaman GNo ratings yet

- DPSD CS8351 U1 PDFDocument182 pagesDPSD CS8351 U1 PDFPragna SidhireddyNo ratings yet

- Design of Radix-4 Signed Digit Encoding for Pre-Encoded MultipliersDocument6 pagesDesign of Radix-4 Signed Digit Encoding for Pre-Encoded MultipliersKanak KujurNo ratings yet

- Mahendra Engineering College) : Continuous Assessment Test - II - Aug - 2019Document2 pagesMahendra Engineering College) : Continuous Assessment Test - II - Aug - 2019Gowri ShankarNo ratings yet

- ME8791 Mechatronics - UNIT IIDocument52 pagesME8791 Mechatronics - UNIT IIUdamanNo ratings yet

- 1151CS104 Digitalelectronics SyllabusDocument2 pages1151CS104 Digitalelectronics Syllabusdogece8707No ratings yet

- Subject: Communication Theory: Department of Electronics and Communication EngineeringDocument12 pagesSubject: Communication Theory: Department of Electronics and Communication EngineeringponniNo ratings yet

- Sistec Ec - 403 DCSDocument15 pagesSistec Ec - 403 DCSmab434No ratings yet

- Adobe Scan 17 Jun 2021Document3 pagesAdobe Scan 17 Jun 2021pNo ratings yet

- Common To E&C, EI&C, CS & IS: Department of Technical Education Subject: Digital ElectronicsDocument9 pagesCommon To E&C, EI&C, CS & IS: Department of Technical Education Subject: Digital ElectronicsVikram RaoNo ratings yet

- Ec8651 Unit 2Document54 pagesEc8651 Unit 2santhoshiniNo ratings yet

- BTech II Sem Digital Electronics SyllabusDocument2 pagesBTech II Sem Digital Electronics SyllabusKasi BandlaNo ratings yet

- A Course Material On DIGITAL ELECTRONICS PDFDocument208 pagesA Course Material On DIGITAL ELECTRONICS PDFdasari_reddyNo ratings yet

- A Course Material On Digital ElectronicsDocument208 pagesA Course Material On Digital Electronicssritama royNo ratings yet

- Digital Electronics & Logic Design (Sub. Code: 210245) : S. E. (Computer Engineering) 2019 CourseDocument77 pagesDigital Electronics & Logic Design (Sub. Code: 210245) : S. E. (Computer Engineering) 2019 CourseTCOA77 Ruturaj jadhav100% (1)

- Satellite Communication Lesson Plan 2018Document11 pagesSatellite Communication Lesson Plan 2018Raja PirianNo ratings yet

- Ee 8002 Dem CP FinalDocument8 pagesEe 8002 Dem CP FinalsivakumarsarvananNo ratings yet

- Digital Logic Families Characteristics and Circuit ImplementationDocument1 pageDigital Logic Families Characteristics and Circuit Implementationdhdw kwhdhwNo ratings yet

- Mca Lab-Ece-3014-Manual - Ay 2022-23Document49 pagesMca Lab-Ece-3014-Manual - Ay 2022-23bushraarhaan02No ratings yet

- Integrated Circuits and Applications: CO1 CO2 CO3 CO4 CO5Document72 pagesIntegrated Circuits and Applications: CO1 CO2 CO3 CO4 CO5Chinsdazz KumarNo ratings yet

- RFIC COURSE HANDOUT NewDocument5 pagesRFIC COURSE HANDOUT NewN.NAGENDRANo ratings yet

- 20EC503 Data Communication Networks Unit 3Document107 pages20EC503 Data Communication Networks Unit 3Ms. Meenakshi G M MCA. Associate ProfessorNo ratings yet

- WB Unit 3Document71 pagesWB Unit 3DORAIRAJ ADARSH Y UEC19132No ratings yet

- Unit - 5 - Multiple Antenna TechniquesDocument65 pagesUnit - 5 - Multiple Antenna TechniquesDORAIRAJ ADARSH Y UEC19132No ratings yet

- Ece 4750 Pset 4Document10 pagesEce 4750 Pset 4Aman TyagiNo ratings yet

- DPCO syllabus (Theory cum Practical ).docxDocument2 pagesDPCO syllabus (Theory cum Practical ).docxyogeshwaran.r2022lcseNo ratings yet

- DDE 1313 Digital Electronics 1 LODocument6 pagesDDE 1313 Digital Electronics 1 LOAhmad FadzlyNo ratings yet

- Assignment - Qns B Sec With Vtu No.Document4 pagesAssignment - Qns B Sec With Vtu No.PIYUSH KUMARNo ratings yet

- Deca ChoDocument9 pagesDeca ChoTARANGITNo ratings yet

- Ec 8094 UNIT 2 Satellite Communication - RMK NotesDocument93 pagesEc 8094 UNIT 2 Satellite Communication - RMK NotesAkNo ratings yet

- 01 PM 072008002900001Document78 pages01 PM 072008002900001Om BhosaleNo ratings yet

- Digital Electronics Course OverviewDocument3 pagesDigital Electronics Course Overviewtushar vermaNo ratings yet

- THEORY CCC 18 RegulationDocument6 pagesTHEORY CCC 18 RegulationMohan KumarNo ratings yet

- Common To E&C, EI&C, CS&E & IS&E: Subject: Digital Electronics-1Document9 pagesCommon To E&C, EI&C, CS&E & IS&E: Subject: Digital Electronics-1Vikram RaoNo ratings yet

- Dr. MPS Memorial College of Business Studies, Agra (Department of IT)Document528 pagesDr. MPS Memorial College of Business Studies, Agra (Department of IT)Anupma MalhotraNo ratings yet

- EC8691-Microprocessor and Microcontroller Department of IT 2021-2022Document24 pagesEC8691-Microprocessor and Microcontroller Department of IT 2021-2022ManjariNo ratings yet

- Digital System Design FundamentalsDocument2 pagesDigital System Design FundamentalsRaut Amit DattatrayNo ratings yet

- Bti 402 Digital ElectronicsDocument1 pageBti 402 Digital ElectronicsSanjay Kr SinghNo ratings yet

- Attachment Circular 2023081115025923 Ic 001Document9 pagesAttachment Circular 2023081115025923 Ic 001shivam.cs667No ratings yet

- DSP Implementation of a DVB-S2 Baseband DemodulatorDocument9 pagesDSP Implementation of a DVB-S2 Baseband Demodulatorkuang.fanNo ratings yet

- DLD Micro Lesson PlaN 2 - Section CDocument4 pagesDLD Micro Lesson PlaN 2 - Section CMadhavarao K0% (1)

- 8-4-2-1 Decimal CodeDocument2 pages8-4-2-1 Decimal CodeponniNo ratings yet

- Subject: Communication Theory: Department of Electronics and Communication EngineeringDocument12 pagesSubject: Communication Theory: Department of Electronics and Communication EngineeringponniNo ratings yet

- Fly Miy Nghy Epw FHJ Kfpo R Rpak Fhiy GDP Nghy Fhzhky NGHFK JD GKK CQ Fs XW Wikia Nkyk XD Wpizf FK RPW RPW T+Ly FSK CQ Fs Tho Tpy VD WK Epiyf F Tho J JF Fs $WKDocument2 pagesFly Miy Nghy Epw FHJ Kfpo R Rpak Fhiy GDP Nghy Fhzhky NGHFK JD GKK CQ Fs XW Wikia Nkyk XD Wpizf FK RPW RPW T+Ly FSK CQ Fs Tho Tpy VD WK Epiyf F Tho J JF Fs $WKponniNo ratings yet

- Department of Electronics and Communication Engineering: R.No Register No. Name of The Student Status ProgressDocument5 pagesDepartment of Electronics and Communication Engineering: R.No Register No. Name of The Student Status ProgressponniNo ratings yet

- Ec8072 Unit 1Document50 pagesEc8072 Unit 1ponniNo ratings yet

- Electromagnetic Interference and CompatiDocument2 pagesElectromagnetic Interference and CompatiponniNo ratings yet

- EMI & Compatibility Test for 4th Year ECE StudentsDocument1 pageEMI & Compatibility Test for 4th Year ECE StudentsponniNo ratings yet

- Communication Theory Course Plan Final - To Be EditedDocument9 pagesCommunication Theory Course Plan Final - To Be EditedponniNo ratings yet

- Unit-I Basic Theory Part - A (2 Marks) Define Inter and Intra System EMIDocument10 pagesUnit-I Basic Theory Part - A (2 Marks) Define Inter and Intra System EMIponniNo ratings yet

- Electromagnetic Interference and CompatiDocument2 pagesElectromagnetic Interference and CompatiponniNo ratings yet

- Elecomagnetic Inteference and CompatibilityDocument11 pagesElecomagnetic Inteference and CompatibilityponniNo ratings yet

- Kings College EMC Test QuestionsDocument2 pagesKings College EMC Test QuestionsponniNo ratings yet

- Ed 21.12.15Document158 pagesEd 21.12.15ponniNo ratings yet

- Unit VDocument1 pageUnit VponniNo ratings yet

- Blooms TaxonomyDocument1 pageBlooms TaxonomyponniNo ratings yet

- FIVDocument1 pageFIVponniNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- Characteristics of Innovative TeachersDocument1 pageCharacteristics of Innovative TeachersponniNo ratings yet

- Comm LabDocument22 pagesComm LabponniNo ratings yet

- Civics OrginalDocument17 pagesCivics OrginalNeb coolNo ratings yet

- Ozark River Bank Cases: 20210821 - Case AnalysisDocument6 pagesOzark River Bank Cases: 20210821 - Case AnalysisTresna AswinNo ratings yet

- Store LocationDocument16 pagesStore LocationChaitanya PillalaNo ratings yet

- MGT162Document23 pagesMGT162ZulaiqhaAisya50% (2)

- Ramthar - March, 2011Document36 pagesRamthar - March, 2011Mizoram Presbyterian Church SynodNo ratings yet

- A.C. No - .10138Document8 pagesA.C. No - .10138Anonymous KgPX1oCfrNo ratings yet

- Robert FrostDocument8 pagesRobert FrostARIESGA, NICOLE FRANCINE M.No ratings yet

- The Use of MuseScore (A Music Transcribing Computer Software) As A Tool in Enhancing The Knowledge and Skills of Non-Music Major Teachers of Tayabas West Central School - IDocument13 pagesThe Use of MuseScore (A Music Transcribing Computer Software) As A Tool in Enhancing The Knowledge and Skills of Non-Music Major Teachers of Tayabas West Central School - IRyan Chester ManzanaresNo ratings yet

- REduce BAil 22Document2 pagesREduce BAil 22Pboy SolanNo ratings yet

- LT033 PDFDocument38 pagesLT033 PDFAlexandr ChuvakovNo ratings yet

- People v Garaygay Ruling on Motion to Quash Search WarrantDocument1 pagePeople v Garaygay Ruling on Motion to Quash Search WarrantchiccostudentNo ratings yet

- A Self-Biased Mixer in CMOS For An Ultra-Wideband ReceiverDocument9 pagesA Self-Biased Mixer in CMOS For An Ultra-Wideband ReceiverwwwNo ratings yet

- Verbal and Nonverbal Communication - Business Communication Skills For ManagersDocument7 pagesVerbal and Nonverbal Communication - Business Communication Skills For ManagersCINDY BALANONNo ratings yet

- ShakespeareDocument4 pagesShakespeareVrinda PatilNo ratings yet

- Onagolonka CV WeeblyDocument2 pagesOnagolonka CV Weeblyapi-247895223No ratings yet

- Activity Guide and Evaluation Rubric - Activity 7 - Creating A WIX PageDocument5 pagesActivity Guide and Evaluation Rubric - Activity 7 - Creating A WIX PageLina VergaraNo ratings yet

- PhilosophyDocument1 pagePhilosophyElena Luneta-BibeNo ratings yet

- Basic Calculus L2Document14 pagesBasic Calculus L2Abbie MalutoNo ratings yet

- 2023 - 002075129500001316312023 - Error CJALDocument7 pages2023 - 002075129500001316312023 - Error CJALFabian Quiroz VergelNo ratings yet

- Affidavit of lost check issued by LANDBANKDocument1 pageAffidavit of lost check issued by LANDBANKMelcris EmeterioNo ratings yet

- AFM Shark-EN 60 - 2017-05-21 - FinalDocument104 pagesAFM Shark-EN 60 - 2017-05-21 - FinalLance Montgomery BoyleNo ratings yet

- Lawki Final ProjectDocument2 pagesLawki Final Projectapi-291471651No ratings yet

- Blooms Taxonomy and Costas Level of QuestioningDocument6 pagesBlooms Taxonomy and Costas Level of QuestioningChris Tine100% (1)

- Reference: A Visual Dictionary By: D.K. Ching: ArchitectureDocument75 pagesReference: A Visual Dictionary By: D.K. Ching: ArchitectureRemzskie PaduganaoNo ratings yet

- Standard Procedure For Acoustic Emission TestDocument10 pagesStandard Procedure For Acoustic Emission TestprendoascroccoNo ratings yet

- Chpater 5 - Conduct of HostilitiesDocument129 pagesChpater 5 - Conduct of Hostilitieswellsbennett100% (1)

- Lesson 4-The Taximan StoryDocument3 pagesLesson 4-The Taximan StoryZian Tallongon100% (2)

- Journal of Cleaner Production: Fabíola Negreiros de Oliveira, Adriana Leiras, Paula CerynoDocument15 pagesJournal of Cleaner Production: Fabíola Negreiros de Oliveira, Adriana Leiras, Paula CerynohbNo ratings yet

- RitzeDocument4 pagesRitzeLalai IskolatongNo ratings yet

- Brown v. Board of EducationDocument1 pageBrown v. Board of EducationSam TaborNo ratings yet