Professional Documents

Culture Documents

Microprocessors and Microcontrollers Question Bank

Uploaded by

heraldOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Microprocessors and Microcontrollers Question Bank

Uploaded by

heraldCopyright:

Available Formats

FORMAT : QP09 KCE/DEPT.

OF ECE

DEPARTMENT OF ELCTRONICS AND COMMUNICATION ENGINEERING

SUBJECT NAME: MICROPROCESSORS AND MICROCONTROLLERS

YEAR / SEMESTER : III / VI

QUESTION BANK (EC8691)

(Version- 3)

PREPARED BY

Mr.A.HERALD, AP/ECE

MPMC 1. 1 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

EC 8691 MICROPROCESSORS AND MICROCONTROLLERS L TP C

3 0 0 3

UNIT I THE 8086 MICROPROCESSOR 9

Introduction to 8086 – Microprocessor architecture – Addressing modes - Instruction set

and assembler directives – Assembly language programming – Modular Programming -

Linking and Relocation - Stacks - Procedures – Macros – Interrupts and interrupt service

routines – Byte and String Manipulation.

UNIT II 8086 SYSTEM BUS STRUCTURE 9

8086 signals – Basic configurations – System bus timing – System design using 8086 – I/O

programming – Introduction to Multiprogramming – System Bus Structure –

Multiprocessor configurations – Coprocessor, Closely coupled and loosely Coupled

configurations – Introduction to advanced processors.

UNIT III I/O INTERFACING 9

Memory Interfacing and I/O interfacing -Parallel communication interface –Serial

communication interface –D/A and A/D Interface -Timer –Keyboard /display controller –

Interrupt controller –DMA controller –Programming and applications Case studies:

Traffic Light control, LED display , LCD display, Keyboard display interface and Alarm

Controller.

UNIT IV MICROCONTROLLER 9

Architecture of 8051 –Special Function Registers(SFRs) -I/O Pins Ports and Circuits -

Instruction set -Addressing modes -Assembly language programming.

UNIT V INTERFACING MICROCONTROLLER 9

Programming 8051 Timers - Serial Port Programming - Interrupts Programming – LCD &

Keyboard Interfacing - ADC, DAC & Sensor Interfacing - External Memory Interface -

Stepper Motor and Waveform generation - Comparison of Microprocessor,

Microcontroller, PIC and ARM processors

TOTAL: 45 PERIODS

SIGNATURE OF STAFF INCHARGE HOD/ECE

Mr.A.Herald

MPMC 1. 2 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

DEPARTMENT OF ELCTRONICS AND COMMUNICATION ENGINEERING

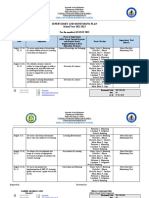

COURSE PLAN

COURSE PLAN

Sub. Code : EC 8691 Branch / Year / Sem : B.E ECE / III/ VI

Sub.Name : Microprocessors And Microcontrollers Batch : 2020-2024

Staff Name : Mr.A.Herald Academic Year : 2022-23 (EVEN)

COURSE OBJECTIVE

1. To understand the Architecture of 8086 microprocessor.

2. To learn the design aspects of I/O and Memory Interfacing circuits.

3. To interface microprocessors with supporting chips.

4. To study the Architecture of 8051 microcontroller.

5. To design a microcontroller based system

TEXT BOOKS

T1:Yu-Cheng Liu, Glenn A.Gibson, ―Microcomputer Systems: The 8086 / 8088 Family

-Architecture, Programming and Design, Second Edition, Prentice Hall of India, 2007.

(UNIT I-III)

T2:Mohamed Ali Mazidi, Janice Gillispie Mazidi, Rolin McKinlay, The 8051 Microcontroller

and Embedded Systems: Using Assembly and C, Second Edition, Pearson education,2011.

(UNIT IV-V)

REFERENCE BOOKS

R1. Doughlas V.Hall, ―Microprocessors and Interfacing, Programming and Hardware,

TMH,2012

R2. A.K.Ray,K.M.Bhurchandi,"Advanced Microprocessors and Peripherals" 3rd edition,

Tata McGrawHill,2012

WEB RESOURCES

W1:http://www.gpcet.ac.in/wp-content/uploads/2017/02/MPI-LECTURE-NOTES-II-II-

R15_2.pdf (Topic.No:03)

W2 : https://www.cosc.brocku.ca/~bockusd/3p92/Lectures/8_IO.ppt (Topic.No:14)

W3 : https://www.cs.cmu.edu/~mtschant/15414-f07/lectures/traffic.ppt (Topic.No:29)

W4 : http://faculty.kfupm.edu.sa/COE/masud/RichText/Microcontroller

%208051-%201.ppt (Topic.No:33)

W5 : https://www.slideshare.net/KanchanPatil34/8051-interfacing (Topic.No:41)

W6 : https://techdifferences.com/difference-between-microprocessor-and-

microcontroller.html (Topic.No:45)

W7 : https://www.elprocus.com/difference-between-avr-arm-8051-and-pic-microcontroller/

(Topic.No:46)

MPMC 1. 3 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

Topic Topic Books for Page No. Teaching No. of Cumulative

No Reference Methodology Hours No. of

Required periods

MPMC 1. 4 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

UNIT I THE 8086 MICROPROCESSOR (10)

01 Introduction to 8086 T1 1-20 BB/PPT 1 1

02 Microprocessor

T1 25-34 NPTEL 1 2

architecture

03 T1 35-39

Addressing modes R1 41-45 L.VIDEO 1 3

W1

04 Instruction set and T1 100-118

BB/PPT 2 5

assembler directives R1 46 - 82

05 Assembly language

T1 53-99 BB/PPT 1 6

programming-

06 Modular Programming T1 141-143 BB/PPT 1 7

07 Linking and Relocation-

T1 143-168 BB/PPT

Stacks -Procedures 1

8

08 T1 174-183

Macros BB/PPT

R1 150 -152

09 Interrupts and interrupt

T1 169-173 BB/PPT 1 9

service routines

10 Byte and String

T1 207-212 BB/PPT 1 10

Manipulation.

LEARNING OUTCOME

At the end of unit, students should be able to ,

Describe the basic concept of microprocessor.

Identify the various programming methodology of microprocessor.

Use the interrupt techniques for various controls.

Analyze various interrupt service routines.

UNIT II 8086 SYSTEM BUS STRUCTURE (10)

8086 signals- Basic T1 310-323

11 BB/PPT 1 11

configurations R1 8-14

12 System bus timing T1 324-329 BB/PPT 1 12

System design using

13 T1 141-191 L.VIDEO 1 13

8086

T1 229-267

14 I/O programming BB/PPT 1 14

W2

Introduction to

15 T1 272-306 BB/PPT 1 15

Multiprogramming

16 System Bus Structure T1 308-310 BB/PPT 1 16

Multiprocessor

17 T1 450-456 BB/PPT 1 17

configurations

T1 456-460

18 Coprocessor BB/PPT 1 18

R2 365-376

Closely coupled and

19 loosely Coupled T1 460-477 BB/PPT 1 19

configurations

Topic Topic Books for Page No. Teaching No. of Cumulative

No Reference Methodology Hours No. of

Required periods

20 Introduction to R1 543-546 BB/PPT 1 20

MPMC 1. 5 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

advanced processors

LEARNING OUTCOME

At the end of unit, students should be able to ,

State the various signals and its uses in the 8086 microprocessor.

Explain the various signals in 8086 microprocessor.

Describe the timing diagram and its uses.

Analyze the different configurations in coprocessor.

UNIT III I/O INTERFACING (10)

Memory Interfacing and T1 346-349

21 BB/PPT 1 21

I/O interfacing R1 158-163

Parallel communication

369-374

22 interface –Serial T1 L.VIDEO 1 22

349-352

communication interface

23 D/A and A/D Interface R2 212-228 BB/PPT 1 23

24 Timer T1 378-383 BB/PPT 1 24

Keyboard display T1 383-395

25 BB/PPT 1 25

controller R2 266-278

26 Interrupt controller R2 249-265 BB/PPT 1 26

T1 395-402

27 DMA controller BB/PPT 1 27

R2 294-302

Programming and

applications , Case

28 T1 385-387 BB/PPT 1 28

studies: Traffic Light

control,

R2 267-270

29 LED display,LCD display SEMINAR 1 29

W3

Keyboard display

T1 383-387

30 interface and Alarm SEMINAR 1 30

R2 276-277

Controller.

LEARNING OUTCOME

At the end of unit, students should be able to ,

State the various interfacing techniques.

Identify the different types interreupts.

Describe concept of DMA controller.

Analyse the concepts used in different applications using case study.

UNIT IV MICROCONTROLLER (10)

31. Architecture of 8051 R2 647-653 BB/PPT 2 32

Special Function

32. Registers(SFRs) T2 92-93 BB/PPT 2 34

I/O Pins Ports and T2 75-85

33. Circuits L.VIDEO 1 35

W4

Instruction set

34. T2 454-479 BB/PPT 2 37

Topic Topic Books for Page No. Teaching No. of Cumulative

No Reference Methodology Hours No. of

Requir periods

ed

MPMC 1. 6 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

Addressing modes T2 89-110

35. BB/PPT 1 38

R2 662-665

Assembly language

36. T2 115-146 BB/PPT 2 40

programming.

LEARNING OUTCOME

At the end of unit, students should be able to ,

Understand the architecture of 8051microcontroller.

Able to explain the functions of Special Function Registers.

Compare the various instructionsets used in 8051.

Analyze the various addressing modes and its uses.

UNIT V INTERFACING MICROCONTROLLER (10)

Programming 8051

37. T2 201-235 BB/PPT 1 41

Timers

38. Serial Port Programming T2 237-265 BB/PPT 1 42

39. Interrupts Programming T2 271-294 BB/PPT 1 43

LCD & Keyboard

40. Interfacing T2 299-319 L.VIDEO 1 44

ADC, DAC Interfacing T2

41. 321-354 BB/PPT 1 45

W5

42. Sensor Interfacing T2 349-350 BB/PPT 1 46

External Memory T2

43. 355-387 BB/PPT 1 47

Interface

Stepper Motor and T2

44. Waveform generation 432-440 BB/PPT 1 48

Comparison of

45. Microprocessor, W6 - BB/PPT 1 49

Microcontroller

46. PIC and ARM processors W7 - BB/PPT 1 50

LEARNING OUTCOME

At the end of unit, students should be able to ,

Describe the different types of programming techniques followed in 8051 Microcontroller.

Able to develop interacing for different applications.

State the different types of sensors and its uses.

Identify the functions of microprocessor and microcontroller.

COURSE OUTCOME

At the end of the course, the students will be able to

Understand and execute programs based on 8086 microprocessor.

Design Memory Interfacing circuits.

Design and interface I/O circuits.

Design and implement 8051 microcontroller based systems.

CONTENT BEYOND THE SYLLABUS

Introduction to Raspberry Pi,working and its applications.

INTERNAL ASSESSMENT DETAILS

ASST. NO. CAT-I CAT-II MODEL

MPMC 1. 7 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

Topic Nos. 1-15 16-30 1-46

Date

ASSIGNMENT DETAILS

ASSIGNMENT No. I II

Topic Nos. for reference 1-15 PCE

Deadline

ASSIGNMENT DETAILS:

ASSIGNMENT-I (50 Marks) ASSIGNMENT II (50 Marks)

(Before CAT-1) (Before CAT – II)

Written Assignment PCE Activity

Activity 1: Case study presentation

Part-A Traffic Light Controller using 8086 &

1. List the addressing modes of 8086? Give 8051.

examples.

LED Controller using 8086 & 8051..

2. Name the hardware interrupts of 8086.

3. Why do we use macros?

Activity 2: Quiz

4. List the features of memory mapped I/O.

Online test

5. What are the advantages of the

multiprocessor systems?

Activity 3: Mind Mapping

8086 & 8051 Interface

Part-B

Activity 4: APH

1. With neat block diagram, explain the

Addressing modes of 8086 & 8051

architecture of 8086 microprocessor.

Instruction sets of 8086 & 8051

2. Discuss the maximum mode and

Advanced processor

minimum mode configuration of 8086 by

with a neat diagram.

Activity 5: Poster Presentation

3. Draw the pin diagram of 8086 CPU and

Architecture of 8086 & 8051

explain the functions of the pins in 8086.

Activity 6: GATE paper solving

Recent question papers

Activity 7: Roll play

Architecture of 8086 & 8051

COURSE ASSESSMENT PLAN

MPMC 1. 8 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

CO Co Description Weightage CAT1 CAT2 MODEL Assign1. PCE AU

CO1 Understand and 40

execute programs

based on 8086

microprocessor

CO2 Design Memory 10

Interfacing circuits

CO3 Design and interface 30

I/O circuits

CO4 Design and 20

implement 8051

microcontroller

based systems

COURSE OUTCOME ALLIGNMENT MATRIX – MODEL EXAM SAMPLE QUESTION SET

Q.No. Question Marks BTL CO PO PI

1 What are the flags available in 8086? 2 L1 CO 1 PO1 1.3.1

2 Identify the difference between Macro

2 L2 CO 1 PO2 2.1.1

and subroutine.

3 Distinguish the LOCK and TEST signal? 2 L2 CO 2 PO2 2.2.4

4 List the advantages of multiprocessor

configurations. 2 L1 CO 2 PO2 2.4.3

5 Name the applications of programmable

interval timer. 2 L1 CO 3 PO1 1.3.1

6 Summarize the modes used by the DMA

processor to transfer data. 2 L2 CO 3 PO1 1.4.1

7 Illustrate the PSW. 2 L2 CO 4 PO1 1.3.1

8 Write the size of memory systems used in

8051 microcontroller? 2 L1 CO 4 PO1 1.3.1

9 What are the types of sensors used for

interfacing? 2 L1 CO 4 PO1 1.4.1

10 How to change the stepper motor

direction? 2 L2 CO 4 PO1 1.4.1

11.a. (i) Examine the various addressing modes 7

available in 8086 with an example. L3 CO 4 PO1 1.3.1

11.a. (ii) Write a program based on 8086

instruction set to compute the average of

6 L3 CO 1 PO2 2.1.3

‘n’ number of bytes stored in the

memory.

11.b. (i) Discuss what happens if interrupts INT0,

TFO and INT1 are activated at the same

time. Assume priority levels were set by 7 L3 CO 1 PO2 2.4.4

the power-up reset and that the external

hardware interrupts are edge-triggered.

MPMC 1. 9 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

11.b. (ii) Categorize the data transfer group and

logical group of 8086 instruction with 6 L3 CO 1 PO1 1.4.1

necessary examples.

12.a. Assess the various schemes used to solve

the bus arbitration problem in 13 L3 CO 1 PO2 2.2.4

multiprocessors.

12.b. Describe the maximum mode signals, bus

cycles, and maximum mode system

13 L3 CO 2 PO1 1.3.1

configuration of 8086 Microprocessor in

detail.

13.a.(i) Develop the ALP for traffic light

controller with busy north to south lane 7 L3 CO 3 PO2 2.1.2

is busier than east to west lane.

13.a(ii) Write a program to initialize 8255 in the

configuration below. (Assume address of

the CW register as 23H).

6 L3 CO 3 PO2 2.1.2

(1)Port A: output with handshake

(2) Port B: input with handshake

(3)Port CL: output (4)Port CU : input

13.b.(i) Draw the block diagram of the 8251 and

discuss how it caters to serial 7 L3 CO 3 PO4 4.1.2

communication. Write the steps in

13.b.(ii) transmitting one byte ofbetween

Draw the connections data serially.

an ADC

and 8086 using 8255 as an interface and 6 L3 CO 3 PO4 4..1.2

explain.

14.a. (i) Give PSW of 8051 and describe the uses

7 L2 CO 4 PO1 1.2.1

of each bit.

14.a(ii) Summarize the functions of the following

6 L2 CO 4 PO1 1.3.1

signals in 8051: RST, EA, PSEN and ALE.

14.b(i) Criticize the internal RAM structure and

6 L2 CO 4 PO1 1.3.1

SFR memory of 8051.

14.b(ii) Classify the bit and byte addressable

registers in 8051 and explain register 7 L2 CO 4 PO1 1.3.1

bank switching.

15.a. What are the functions of

timers/counters? Explain the modes of 13 L3 CO 4 PO1 1.3.1

15.b operation.he various interrupts and their

Evaluate

associated priorities in 8051 13 L3 CO 4 PO2 2.2.4

microcontroller.

16.a Write an ALP using 8051 instructions to

receive bytes of data serially and put 15 L1 CO 4 PO3 3.1.6

them in P1. Set the baud rate at 4800, 8-

bit data, and 1 stop bit

16.b Draw the architecture block diagram of

8086 with its registers. 15 L1 CO 4 PO1 1.3.1

ASSESSMENT PAPER QUALITY MATRIX

MPMC 1. 10 KCE/ECE/QB/III YR/MPMC

FORMAT : QP09 KCE/DEPT. OF ECE

PART Level-1 Level-2 Level-3 Level-4 Level-5 Level-6

A 1,4,5,8,9 2,3,6,7,10 - - - -

11.a &11.b

12.a & 12.b

B - 14.a & 14.b - - -

13.a &13.b

15.a & 15.b

C 16.a ,16.b - - - - -

TOTAL 25% 23% 52% - - -

Distribution 48 52

Prepared by Verified by

A.HERALD, AP/ECE HOD/ECE

Approved by

PRINCIPAL

MPMC 1. 11 KCE/ECE/QB/III YR/MPMC

You might also like

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureFrom EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureRating: 1 out of 5 stars1/5 (1)

- Modern Component Families and Circuit Block DesignFrom EverandModern Component Families and Circuit Block DesignRating: 5 out of 5 stars5/5 (1)

- Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesLesson Plan Microprocessor and Micro COntrollerRaja Pirian0% (2)

- EC8691 Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesEC8691 Lesson Plan Microprocessor and Micro COntrollerlauro eugin brittoNo ratings yet

- MPMC CP FinalDocument9 pagesMPMC CP Finalsimman8371029No ratings yet

- Eee-Iii-Ii Lesson Plans (A & B)Document31 pagesEee-Iii-Ii Lesson Plans (A & B)JeronimoNo ratings yet

- RMK Group A4 PPT - MPMC - Ec8691 - Unit 1Document127 pagesRMK Group A4 PPT - MPMC - Ec8691 - Unit 1Gowtham Reddy Rekkala100% (1)

- Department Electronics Communication Course PlanDocument4 pagesDepartment Electronics Communication Course PlansarvanmeNo ratings yet

- 1151EC110MICROPROCESSORANDMICROCONTROLLERDocument3 pages1151EC110MICROPROCESSORANDMICROCONTROLLERTheanmozhi SNo ratings yet

- EE2354Document7 pagesEE2354swathi_grenNo ratings yet

- Mahendra Engineering College Syllabus: V SemesterDocument3 pagesMahendra Engineering College Syllabus: V SemesterJ.Gowri ShankarNo ratings yet

- EC8691-Microprocessor and Microcontroller Department of IT 2021-2022Document24 pagesEC8691-Microprocessor and Microcontroller Department of IT 2021-2022ManjariNo ratings yet

- Communication Networks Lesson PlanDocument9 pagesCommunication Networks Lesson Planramarajan100% (2)

- Mca Lab-Ece-3014-Manual - Ay 2022-23Document49 pagesMca Lab-Ece-3014-Manual - Ay 2022-23bushraarhaan02No ratings yet

- 8085 LPDocument6 pages8085 LPVenkat RamananNo ratings yet

- Microprocessor 8085 & Microcontroller 8051 CourseDocument2 pagesMicroprocessor 8085 & Microcontroller 8051 CoursePrasanthNo ratings yet

- Lecture Plan COMPUTER NETWORKSDocument3 pagesLecture Plan COMPUTER NETWORKSsamNo ratings yet

- MPMCDocument1 pageMPMCSurya RNo ratings yet

- Digital Electronics Question BankDocument10 pagesDigital Electronics Question BankponniNo ratings yet

- De&mp Unit - 4Document36 pagesDe&mp Unit - 4Mahesh BabuNo ratings yet

- Ec8691 MPMC Question BankDocument31 pagesEc8691 MPMC Question Banksujithaa13No ratings yet

- Microprocessor and Its ApplicationsDocument166 pagesMicroprocessor and Its ApplicationsDhivya Gokul100% (1)

- 18EC2028 Teaching Plan in FormatDocument5 pages18EC2028 Teaching Plan in FormatMerin JohnNo ratings yet

- Microprocessor & Microcontroller NotesDocument80 pagesMicroprocessor & Microcontroller Notesgokul docNo ratings yet

- Mano MPMC Lesson PlanDocument4 pagesMano MPMC Lesson Plantmuthu123No ratings yet

- Microcontrollers & Applications QBDocument7 pagesMicrocontrollers & Applications QBKeerthe VaasanNo ratings yet

- Tp2 Initation Kit Com3lab (20202021)Document2 pagesTp2 Initation Kit Com3lab (20202021)Na DaNo ratings yet

- De&mp Unit - 5Document30 pagesDe&mp Unit - 5Mahesh BabuNo ratings yet

- Mahatma Education Society's PILLAI COLLEGE OF ENGINEERING, NEW PANVEL Microprocessor and Peripherals Question BankDocument19 pagesMahatma Education Society's PILLAI COLLEGE OF ENGINEERING, NEW PANVEL Microprocessor and Peripherals Question BankYESHUDAS MUTTUNo ratings yet

- SDH Rdso 53 09Document12 pagesSDH Rdso 53 09GURNAYANNo ratings yet

- 18ec51 MPMCDocument2 pages18ec51 MPMCKaran JaganathNo ratings yet

- Course Outcomes (Cos)Document38 pagesCourse Outcomes (Cos)Kushal 157No ratings yet

- Microprocessor Architecture and Programming AssignmentsDocument3 pagesMicroprocessor Architecture and Programming AssignmentsDonika MarkandeNo ratings yet

- Lecturer Plan Microprocessor and MicrocontrollerDocument3 pagesLecturer Plan Microprocessor and MicrocontrollerRathan NNo ratings yet

- VTU Microprocessors and Controllers Midterm ExamDocument2 pagesVTU Microprocessors and Controllers Midterm ExamDheeraj13No ratings yet

- Microprocessors and MicrocontrollersDocument3 pagesMicroprocessors and MicrocontrollersNathanNo ratings yet

- Ec8691 Micro Processor and Micro ControllerDocument53 pagesEc8691 Micro Processor and Micro ControllerHema TNo ratings yet

- Cat-352 MP Unit 3.1Document23 pagesCat-352 MP Unit 3.1Ashish YadavNo ratings yet

- Ug-r20-Eee & Ece MPMC SyllabusDocument3 pagesUg-r20-Eee & Ece MPMC SyllabusSanoxNo ratings yet

- Mumbai University SyllabusDocument30 pagesMumbai University SyllabusjcijosNo ratings yet

- The 8051 MicrocontollerDocument212 pagesThe 8051 Microcontollermahmudou100% (1)

- CS2252 LPDocument7 pagesCS2252 LPGidey GebrehiwotNo ratings yet

- Seminar Report On 8051 MicrocontrollerDocument21 pagesSeminar Report On 8051 MicrocontrollerChiyan RanjithNo ratings yet

- 8051 MicrocontrollerDocument23 pages8051 Microcontrollerblackhorse.nerdNo ratings yet

- Government Polytechnic, Nagpur. Course Curriculum: Teaching SchemeDocument41 pagesGovernment Polytechnic, Nagpur. Course Curriculum: Teaching SchemeAkhilesh PandeNo ratings yet

- Ec6013 Ampmc MSMDocument94 pagesEc6013 Ampmc MSMsakthi mareeswari100% (1)

- GTU Microprocessor CourseDocument3 pagesGTU Microprocessor Coursehiren456789No ratings yet

- UNIT 1 - Microprocessor Microcontroller - Lecture 4 - 8085 Instruction SetDocument99 pagesUNIT 1 - Microprocessor Microcontroller - Lecture 4 - 8085 Instruction SetHelenNo ratings yet

- 2152006Document3 pages2152006Mohamed Ismail FiazNo ratings yet

- CS8601 MC Course PlanDocument6 pagesCS8601 MC Course PlanRethina Sabapathi PandiyanNo ratings yet

- Microcontroller Course Delivery PlanDocument7 pagesMicrocontroller Course Delivery PlanMal DitaNo ratings yet

- Gujarat Technological University: Page 1 of 5Document5 pagesGujarat Technological University: Page 1 of 5Keval PatelNo ratings yet

- Advanced MicroprocessorDocument8 pagesAdvanced MicroprocessorGanesh VsNo ratings yet

- Microcontroller: 8051 Stack, I/O Port Interfacing and ProgrammingDocument39 pagesMicrocontroller: 8051 Stack, I/O Port Interfacing and ProgrammingPraveen G MNo ratings yet

- ME8791 Mechatronics - UNIT IIDocument52 pagesME8791 Mechatronics - UNIT IIUdamanNo ratings yet

- Rao & Naidu Engg. College, Ongole: CertificateDocument60 pagesRao & Naidu Engg. College, Ongole: CertificateKoundinya ChunduruNo ratings yet

- CS (Ece) (Eee) (Instr) F241 - Mpi - 2023 - 24Document3 pagesCS (Ece) (Eee) (Instr) F241 - Mpi - 2023 - 24f20212358No ratings yet

- MPMC Corse File1Document245 pagesMPMC Corse File1KiranNo ratings yet

- 8051 MC 2010Document7 pages8051 MC 2010Vikram RaoNo ratings yet

- PLC Controls with Structured Text (ST): IEC 61131-3 and best practice ST programmingFrom EverandPLC Controls with Structured Text (ST): IEC 61131-3 and best practice ST programmingRating: 4 out of 5 stars4/5 (11)

- 8086 and 8051 Microcontroller QuestionsDocument3 pages8086 and 8051 Microcontroller QuestionsheraldNo ratings yet

- EC3354 Signals and SystemsDocument58 pagesEC3354 Signals and SystemsheraldNo ratings yet

- Presentation On Networks and SecurityDocument14 pagesPresentation On Networks and SecurityheraldNo ratings yet

- Current to Voltage Converter ApplicationsDocument4 pagesCurrent to Voltage Converter ApplicationsheraldNo ratings yet

- Communication Lab Course Plan Ec8561Document4 pagesCommunication Lab Course Plan Ec8561heraldNo ratings yet

- Department of Electronics and Communication Engineering: Prepared byDocument6 pagesDepartment of Electronics and Communication Engineering: Prepared byheraldNo ratings yet

- Lesson PlanDocument12 pagesLesson PlanheraldNo ratings yet

- Subject: Ec8501 Digital Communication: Department of Electronics and Communication EngineeringDocument6 pagesSubject: Ec8501 Digital Communication: Department of Electronics and Communication EngineeringheraldNo ratings yet

- Vdocuments - MX Setting Procedure Evs HMF Tech Procedure Evs 11 16pdf Setting ProcedureDocument37 pagesVdocuments - MX Setting Procedure Evs HMF Tech Procedure Evs 11 16pdf Setting ProcedureKrum Kashavarov100% (1)

- Flygt 4660 EnglishDocument2 pagesFlygt 4660 EnglishVictor Manuel Lachira YarlequeNo ratings yet

- SMS Security Android AppDocument8 pagesSMS Security Android AppSuman SouravNo ratings yet

- Case3: What's in A Car 1. What Kind of Research Study Should Shridhar Undertake? Define TheDocument2 pagesCase3: What's in A Car 1. What Kind of Research Study Should Shridhar Undertake? Define TheRoshan kumar Rauniyar0% (3)

- VELMATIC Well Service Air ValveDocument2 pagesVELMATIC Well Service Air Valvecarlos37No ratings yet

- Senthamarai Kannan S V (Kannan) Oracle SCM and Oracle MFG, Oracle ASCP (PTP/OTC/WMS/ASCP/INV/PIM/OPM) Manager/Sr Manager/Functional LeadDocument8 pagesSenthamarai Kannan S V (Kannan) Oracle SCM and Oracle MFG, Oracle ASCP (PTP/OTC/WMS/ASCP/INV/PIM/OPM) Manager/Sr Manager/Functional LeadKarunya KannanNo ratings yet

- Celebrity Parents Open Up About Raising Children With Special NeedsDocument4 pagesCelebrity Parents Open Up About Raising Children With Special NeedsBarathy ChandrasegranNo ratings yet

- Itp Concrete CoatingDocument4 pagesItp Concrete Coatingkaml100% (1)

- Review Relative Clauses, Articles, and ConditionalsDocument10 pagesReview Relative Clauses, Articles, and ConditionalsNgoc AnhNo ratings yet

- Supervisory Plan 2022 2023Document4 pagesSupervisory Plan 2022 2023Jesieca Bulauan100% (12)

- Building Power and InfluenceDocument5 pagesBuilding Power and InfluenceQuang-Nam Nguyen100% (1)

- KR 280 R3080 F technical specificationsDocument1 pageKR 280 R3080 F technical specificationsDorobantu CatalinNo ratings yet

- The Impact of COVID-19 On The Steel IndustryDocument25 pagesThe Impact of COVID-19 On The Steel IndustryAyesha KhalidNo ratings yet

- Marivy Abella ResearchDocument43 pagesMarivy Abella ResearchRo Gi LynNo ratings yet

- Acid-Base Titration Using PH Meter and Finding The Equivalence Point Naoh ConcentrationDocument8 pagesAcid-Base Titration Using PH Meter and Finding The Equivalence Point Naoh ConcentrationYocobSamandrewsNo ratings yet

- DDX3035 - Audio File - KenwoodDocument5 pagesDDX3035 - Audio File - KenwoodRistho LutherNo ratings yet

- Rubber Conveyor Belt Wear ResistanceDocument5 pagesRubber Conveyor Belt Wear ResistanceBelt Power LLCNo ratings yet

- Learn From Customers to Improve Products and ServicesDocument8 pagesLearn From Customers to Improve Products and ServicesQuan Hoang AnhNo ratings yet

- HZVDocument6 pagesHZVnurrozaqNo ratings yet

- Capstone Presentation 2020Document12 pagesCapstone Presentation 2020api-539629427No ratings yet

- Siwarex Cs-En v12Document15 pagesSiwarex Cs-En v12Diego CanoNo ratings yet

- Module 5 HomeworkDocument4 pagesModule 5 HomeworkCj LinceNo ratings yet

- Cement and Concrete Research: Amin Abrishambaf, Mário Pimentel, Sandra NunesDocument13 pagesCement and Concrete Research: Amin Abrishambaf, Mário Pimentel, Sandra NunesJoseluis Dejesus AnguloNo ratings yet

- Dual Domain Image Encryption Using Bit Plane Scrambling and Sub - Band ScramblingDocument16 pagesDual Domain Image Encryption Using Bit Plane Scrambling and Sub - Band Scramblingraja rishyantNo ratings yet

- Muhammad Farrukh QAMAR - Assessment 2 Student Practical Demonstration of Tasks AURAMA006 V2Document19 pagesMuhammad Farrukh QAMAR - Assessment 2 Student Practical Demonstration of Tasks AURAMA006 V2Rana Muhammad Ashfaq Khan0% (1)

- WellBeing I193 2021Document164 pagesWellBeing I193 2021lan tranNo ratings yet

- First Aid KitDocument15 pagesFirst Aid Kitdex adecNo ratings yet

- ENGLISH CONTENT UNIT 4 2022 5tos.Document9 pagesENGLISH CONTENT UNIT 4 2022 5tos.Dylan QuiñónezNo ratings yet

- GCMS-QP2010 User'sGuide (Ver2.5) PDFDocument402 pagesGCMS-QP2010 User'sGuide (Ver2.5) PDFnguyenvietanhbtNo ratings yet

- Kuruk Etra:: Dharma-K Etra Śalya-ParvaDocument1 pageKuruk Etra:: Dharma-K Etra Śalya-ParvaRavinder Khullar100% (1)