Professional Documents

Culture Documents

RIVERA Logics - Lab 7

Uploaded by

Ricardo Edrell RiveraCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

RIVERA Logics - Lab 7

Uploaded by

Ricardo Edrell RiveraCopyright:

Available Formats

Laboratory Exercises in Logic Circuits and Design Lab Exercise No.

LCaD-07

Name: RIVERA, RICARDO EDRELL D. Date Completed:

________________

Instructor: MARK JONIEL M. LOPEZ Instructor’s Signature:

LABORATORY EXERCISE NO. LCaD-07

XOR GATE

Exercise Overview

This exercise will introduce you to the basics of Logic gates XOR

EXERCISE LEARNING OBJECTIVES

At the end of this exercise, the students are expected to

• To study the basic logic gates: XOR

• To study the representation of these functions by truth tables, logic diagrams and

Boolean algebra.

• To observe the pulse response of logic gates

EXERCISE CONTENTS

I. MATERIALS REQUIRED:

1 Power Supply (w/ 5v DC source)

LED / Logic Probe

Connecting Wires

Breadboard

1 74LS86 XOR Gate

II. PRINCIPLES:

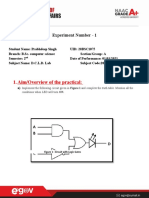

XOR - A multi-input circuit in which the output is 1 if either input is HIGH. The

symbolic representation of the XOR gate is shown in Fig. 1a.

Fig 1a.

III. PROCEDURES:

1. For the XOR gate look on the data sheets, connect the circuit on Breadboard

and test the gate.

2. Using logic switches SW1 and SW2, apply the logic levels 0 and 1 to gate

inputs

3. Create a truth table and record the results

4. Also simulate the given gate using the Circuit Wizard simulation software

5. Obtain the corresponding circuit diagram using the simulation software of the

Boolean expression F((A, B,C)=( A’B +AB’) + (B’C +BC’)

PANGASINAN STATE UNIVERSITY Prepared by: Mark Joniel M. Lopez, CpE 1

Laboratory Exercises in Logic Circuits and Design Lab Exercise No. LCaD-07

6. From the obtain circuit diagram develop the corresponding truth table

7. From the figure below obtain the equivalent Boolean expression and develop

its corresponding truth Table

NOTE: Never supply the circuit with more than 5v DC source.

LED ON = Logic 1, (High)

LED OFF = Logic 0 (Low)

A B OUTPUT Y

0 0 0

0 1 1

1 0 1

1 1 1

IV. DATA AND RESULTS: (place your answer here from 1-7) include actual photos during

bread board assembly

Using circuit wizard, simulation of XOR gate.

PANGASINAN STATE UNIVERSITY Prepared by: Mark Joniel M. Lopez, CpE 2

Laboratory Exercises in Logic Circuits and Design Lab Exercise No. LCaD-07

The corresponding circuit diagram using the simulation software of the Boolean expression

F((A, B,C)=( A’B +AB’) + (B’C +BC’)

The figure below shows the circuit diagram of the Boolean expression F(A, B,C)=( A’B

+AB’) + (B’C +BC’)

Truth table of F(A, B,C)=( A’B +AB’) + (B’C +BC’)

A B C F= ( A’B

+AB’) + (B’C +BC’)

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 0

The figure below obtains the equivalent Boolean expression and develops its

corresponding truth Table

PANGASINAN STATE UNIVERSITY Prepared by: Mark Joniel M. Lopez, CpE 3

Laboratory Exercises in Logic Circuits and Design Lab Exercise No. LCaD-07

The table above shows the truth table of the Boolean expression F= ((A’B +AB’)’+

(C’D+CD’))+ ((A’B +AB’)+(C’D+CD’)’)

A B C D F= ((A’B +AB’)’+

(C’D+CD’))+ ((A’B

+AB’)+(C’D+CD’)’)

0 0 0 0 1

0 0 0 1 1

0 0 1 0 1

0 0 1 1 1

0 1 0 0 1

0 1 0 1 1

0 1 1 0 1

0 1 1 1 1

1 0 0 0 1

1 0 0 1 1

1 0 1 0 1

1 0 1 1 1

1 1 0 0 1

1 1 0 1 1

1 1 1 0 1

1 1 1 1 1

F= ((A’B +AB’)’+(C’D+CD’))+ ((A’B +AB’)+(C’D+CD’)’)

PANGASINAN STATE UNIVERSITY Prepared by: Mark Joniel M. Lopez, CpE 4

Laboratory Exercises in Logic Circuits and Design Lab Exercise No. LCaD-07

V. OBSERVATIONS: The XOR gate is a digital logic gate that implements an

exclusive or; that is, a true output results if one, and only one, of the inputs to

the gate is true. If both inputs are false or both are true, a false output result.

VI. CONCLUSION: XOR represents the inequality function, i.e., the output is HIGH if

the inputs are not alike otherwise the output is LOW. XOR can also be viewed as

addition modulo 2. As a result, XOR gates are used to implement binary addition

in computers. A half adder consists of an XOR gate and an AND gate.

VII. CHECKING:

PANGASINAN STATE UNIVERSITY Prepared by: Mark Joniel M. Lopez, CpE 5

You might also like

- RIVERA Logics - Lab 8Document5 pagesRIVERA Logics - Lab 8Ricardo Edrell RiveraNo ratings yet

- RIVERA LOGIC CIRCUITS - Lab 2Document7 pagesRIVERA LOGIC CIRCUITS - Lab 2Ricardo Edrell RiveraNo ratings yet

- NOT/INVERTER Gate Lab ExerciseDocument5 pagesNOT/INVERTER Gate Lab ExerciseRicardo Edrell RiveraNo ratings yet

- RIVERA LOGICS - Lab 6Document4 pagesRIVERA LOGICS - Lab 6Ricardo Edrell RiveraNo ratings yet

- I. Objectives:: Logic GatesDocument4 pagesI. Objectives:: Logic GatesDonnalyn LandichoNo ratings yet

- Lab Rep 3-4Document7 pagesLab Rep 3-4Muhammad Hamza TariqNo ratings yet

- DLD manual_EXP_3Document3 pagesDLD manual_EXP_3Ahmad RazaNo ratings yet

- Experiment 2 FinalDocument9 pagesExperiment 2 Finalliddleme33No ratings yet

- Lab No. 6: Understanding The Simplification by Boolean Algebra, Truth Table and Karnaugh MapDocument4 pagesLab No. 6: Understanding The Simplification by Boolean Algebra, Truth Table and Karnaugh MapInam Ur RehmanNo ratings yet

- Experiment 7Document7 pagesExperiment 7Karan KumarNo ratings yet

- Chapter # 3Document57 pagesChapter # 3Badr AlayoubiNo ratings yet

- DIGITAL LOGIC CIRCUITS ANALYSIS AND BOOLEAN EXPRESSIONSDocument10 pagesDIGITAL LOGIC CIRCUITS ANALYSIS AND BOOLEAN EXPRESSIONSSalam ShaikhNo ratings yet

- Tutorial 2 - Electronics (2018)Document3 pagesTutorial 2 - Electronics (2018)Pasindu PramodNo ratings yet

- Fazila (21-43) MB DLD LAB ManualDocument11 pagesFazila (21-43) MB DLD LAB ManualMaryam SafdarNo ratings yet

- Module2LogicLab2 AustriaBal OtDocument12 pagesModule2LogicLab2 AustriaBal OtChester Dave Bal-otNo ratings yet

- Digital Logic Design Techniques and Boolean Expression SimplificationDocument58 pagesDigital Logic Design Techniques and Boolean Expression SimplificationHaider AliNo ratings yet

- BI2002B - Circuitos LógicosDocument30 pagesBI2002B - Circuitos LógicosHéctor Vega SantamaríaNo ratings yet

- Lab-Journal-3-30032024-104144pm (1)Document7 pagesLab-Journal-3-30032024-104144pm (1)Muhammad bilalNo ratings yet

- CpE 272 Digital Lab Report SummaryDocument9 pagesCpE 272 Digital Lab Report SummaryMayra CintoraNo ratings yet

- CS302 - Lab Manual - Week NoDocument6 pagesCS302 - Lab Manual - Week NoAtif MubasharNo ratings yet

- Answers Pre Exp3-1Document8 pagesAnswers Pre Exp3-1Mohamad MonerNo ratings yet

- Course Title: Digital Design Lab: Bahria University, IslamabadDocument15 pagesCourse Title: Digital Design Lab: Bahria University, IslamabadshahwaizNo ratings yet

- Experiment No. 1 Design and Implementation of Basic Logic Gates and Combinational CircuitsDocument17 pagesExperiment No. 1 Design and Implementation of Basic Logic Gates and Combinational CircuitsUnlimited XfinityNo ratings yet

- Assignment 1 DGEN245 Digital ElectronicDocument3 pagesAssignment 1 DGEN245 Digital ElectronicAja AzizNo ratings yet

- Combinational Logic CircuitsDocument5 pagesCombinational Logic CircuitsChristian Allan LumakinNo ratings yet

- DLD HWDocument17 pagesDLD HWNấm LùnNo ratings yet

- Exercise E51IFE: Laboratory of ElectronicsDocument14 pagesExercise E51IFE: Laboratory of Electronicsabd sinNo ratings yet

- Lec 09Document34 pagesLec 09bivaye4887No ratings yet

- FDDGDocument3 pagesFDDGaliffpadziNo ratings yet

- Combinational Logic Gate Schematic and Truth TableDocument5 pagesCombinational Logic Gate Schematic and Truth TableFaisal HaroonNo ratings yet

- Computer Organization and Architecture Lab: G L Bajaj Institute of Technology and Management Greater Noida - 201306Document28 pagesComputer Organization and Architecture Lab: G L Bajaj Institute of Technology and Management Greater Noida - 201306Anshika Chauhan100% (2)

- Digital Logic & Design: Faraz Hasan KhanDocument46 pagesDigital Logic & Design: Faraz Hasan Khanmissing wonderNo ratings yet

- Tut 3Document3 pagesTut 3MariamNo ratings yet

- Digital Circuits-I LAB: Jadavpur UniversityDocument15 pagesDigital Circuits-I LAB: Jadavpur UniversityIron PatriotNo ratings yet

- DLD THEORY ASS 01 - Izaan Ahmed Khan (FA19-BSCS-0049)Document13 pagesDLD THEORY ASS 01 - Izaan Ahmed Khan (FA19-BSCS-0049)Izaan Ahmed KhanNo ratings yet

- Complete PracticalDocument16 pagesComplete PracticalshabbirjamaliNo ratings yet

- DLD LabDocument8 pagesDLD LabAbdullah MaqsoodNo ratings yet

- Recent PHD ResultDocument72 pagesRecent PHD ResultSavita Kiran BNo ratings yet

- Lab ReportDocument7 pagesLab Reportlesh allanoNo ratings yet

- Ee222 Lab 3Document9 pagesEe222 Lab 3Jakob NandNo ratings yet

- DLD LAB 04Document11 pagesDLD LAB 04kalmaaa66No ratings yet

- Co Lab ManualDocument81 pagesCo Lab ManualShiva KumarNo ratings yet

- Experiment Number 1 Logic GatesDocument6 pagesExperiment Number 1 Logic GatesPrabh deepNo ratings yet

- I. Objectives:: Logic GatesDocument4 pagesI. Objectives:: Logic GatesDonnalyn LandichoNo ratings yet

- Digital Electronics 1 QPDocument12 pagesDigital Electronics 1 QPkhalil rehmanNo ratings yet

- Activity 3: The or Gate Objective:: A B (A) Y A+BDocument3 pagesActivity 3: The or Gate Objective:: A B (A) Y A+BChristian Allan LumakinNo ratings yet

- Application of Boolean Algebra and Discrete Maths ConceptsDocument18 pagesApplication of Boolean Algebra and Discrete Maths Conceptsraneem koutahNo ratings yet

- Implementing Logic Gates and Code ConversionsDocument28 pagesImplementing Logic Gates and Code ConversionsayushNo ratings yet

- Lab 1 - Portes LogiquesDocument18 pagesLab 1 - Portes Logiquesnoe finaritra RandriambolaNo ratings yet

- DLD Lab 03-Combinational LogicDocument6 pagesDLD Lab 03-Combinational LogicMuhammad RafayNo ratings yet

- Chapter 2 AssignmentDocument4 pagesChapter 2 AssignmentAB SHOWNo ratings yet

- Digital Logic Design: Faraz Hasan KhanDocument14 pagesDigital Logic Design: Faraz Hasan Khanmissing wonderNo ratings yet

- Verification of Logic Gates LabDocument11 pagesVerification of Logic Gates LabJeromeNo ratings yet

- Tutorial 5 - Digital SystemDocument2 pagesTutorial 5 - Digital Systembalqies281No ratings yet

- Activity 2 - Combinational WorksheetdDocument4 pagesActivity 2 - Combinational WorksheetdPopola PWNo ratings yet

- Lab 6Document3 pagesLab 6farazsiddiqui2003No ratings yet

- CS302 - Lab Manual - Week No PDFDocument5 pagesCS302 - Lab Manual - Week No PDFattiqueNo ratings yet

- Dpco LabDocument43 pagesDpco Labpriya SNo ratings yet

- Eeeb161 Lab ReportDocument7 pagesEeeb161 Lab ReportRoxas Nabeyl0% (1)

- 4 AppleDocument9 pages4 AppleSam Peter GeorgieNo ratings yet

- InfluencerDocument198 pagesInfluencerAkanksha SethiNo ratings yet

- 2016 Students ch04 - Lovelock - Developing Service Products - 6e - STUDENTDocument36 pages2016 Students ch04 - Lovelock - Developing Service Products - 6e - STUDENTbold onyxNo ratings yet

- Manual DishwashingDocument2 pagesManual Dishwashingkean redNo ratings yet

- A Geometric Method For Kinematics of Delta Robot and Its Path Tracking Control PDFDocument6 pagesA Geometric Method For Kinematics of Delta Robot and Its Path Tracking Control PDFJameszouqunNo ratings yet

- Ratio & Proportion - Important Maths For BankDocument9 pagesRatio & Proportion - Important Maths For BankXpired ZoneNo ratings yet

- Bangladesh Labour Rights ResearchDocument29 pagesBangladesh Labour Rights ResearchMd. Hasan Ali JoyNo ratings yet

- Evolution of Arbitration in IndiaDocument8 pagesEvolution of Arbitration in IndiaPururaj AggarwalNo ratings yet

- Evolution of Highrise Buildings: Architectural Design - 7 SEMDocument41 pagesEvolution of Highrise Buildings: Architectural Design - 7 SEMVismithaNo ratings yet

- Modeling Drop Structures in HEC-RAS 3.1Document29 pagesModeling Drop Structures in HEC-RAS 3.1reluNo ratings yet

- Sand Patch TestDocument5 pagesSand Patch TestgreatpicNo ratings yet

- Superior Drummer 2 ManualDocument38 pagesSuperior Drummer 2 ManualEmmanuel MarcosNo ratings yet

- EI2 Public Benefit Organisation Written Undertaking External FormDocument1 pageEI2 Public Benefit Organisation Written Undertaking External Formshattar47No ratings yet

- +1 TM Slow Learner Material For Reduced Portion 2021-22Document55 pages+1 TM Slow Learner Material For Reduced Portion 2021-22Prasanth Prasanth100% (2)

- Intelligent Platform Management Bus Communications Protocol Specification v1.0Document43 pagesIntelligent Platform Management Bus Communications Protocol Specification v1.0alexchuahNo ratings yet

- Zida Requirements of Renewal FormDocument1 pageZida Requirements of Renewal FormTafadzwa Matthew Gwekwerere P.B.CNo ratings yet

- Credit Risk ManagementDocument85 pagesCredit Risk ManagementDarpan GawadeNo ratings yet

- Capital Expenditure Decision Making ToolsDocument19 pagesCapital Expenditure Decision Making ToolsRoshan PoudelNo ratings yet

- Group 3 - Brand Architecture Assignment IDocument9 pagesGroup 3 - Brand Architecture Assignment IShijin SreekumarNo ratings yet

- Fire Resistance UL 1709Document2 pagesFire Resistance UL 1709ednavilod100% (3)

- Cbam Faq 1701387432Document34 pagesCbam Faq 1701387432zamarrillaNo ratings yet

- Judicial Watch Vs State Dept Stephen Mull DepositionDocument415 pagesJudicial Watch Vs State Dept Stephen Mull DepositionThe Conservative Treehouse100% (1)

- How To Combine Cells Into A Cell With Comma, Space and Vice VersaDocument8 pagesHow To Combine Cells Into A Cell With Comma, Space and Vice VersaClifford Marco ArimadoNo ratings yet

- Notaries Act 1999 rules for Dutch notariesDocument45 pagesNotaries Act 1999 rules for Dutch notariesAnt1603No ratings yet

- Coal PDFDocument36 pagesCoal PDFurjanagarNo ratings yet

- Madras University Time TableDocument19 pagesMadras University Time TablearvindNo ratings yet

- Cloze Test For The Upcoming SSC ExamsDocument9 pagesCloze Test For The Upcoming SSC ExamsAbhisek MishraNo ratings yet

- PR100 Locks With Aperio Wireless Technology: Key FeaturesDocument2 pagesPR100 Locks With Aperio Wireless Technology: Key FeaturesMay SamboNo ratings yet

- Republic vs. Roque - JD1ADocument4 pagesRepublic vs. Roque - JD1AQueenie Boado100% (1)

- SpirentAutomotiveLV124 LV148VDocument38 pagesSpirentAutomotiveLV124 LV148VNiculcea Cristin100% (3)