Professional Documents

Culture Documents

Dpco Lab

Uploaded by

priya SOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dpco Lab

Uploaded by

priya SCopyright:

Available Formats

lOMoARcPSD|6634547

Dpco-Lab-Manual

digital principles and system design (Anna University)

Studocu is not sponsored or endorsed by any college or university

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

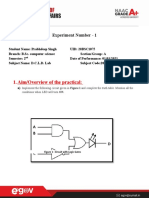

EXP. NO: 1

DATE :

VERIFICATION OF BOOLEAN THEOREMS USING BASIC GATES

Aim:

To verify the truth table of basic Boolean algebraic laws by using Basic gates.

Components Required:

S.NO COMPONENTS RANGE QUANTITY

1 Digital IC trainer kit - 1

7400 1

7402 1

7404 1

2 IC

7408 1

7432 1

7486 1

3 Bread board - 1

4 Connecting wires - As required

Theory:

Demorgan’s Theorems

First Theorem:

It states that the complement of a product is equal to the sum of the

complements.

(AB)′ =A′ +B′

Second Theorem:

It states that the complement of a sum is equal to the product of the

complements.

(A+B)′ =A′.B′

Boolean Laws:

Boolean algebra is a mathematical system consisting of a set of two or more

distinct elements, two binary operators denoted by the symbols (+) and (.) and one unary

operator denoted by the symbol either bar (-) or prime („). They satisfy the commutative,

associative, distributive and absorption properties of the Boolean algebra.

Commutative Property:

Boolean addition is commutative, given

by A+B=B+A

Boolean algebra is also commutative over multiplication,

given by A.B=B.A

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

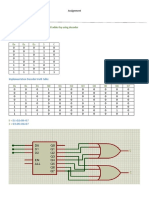

Verification of Logic Gates:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Associative Property:

The associative property of addition is given

by A+ (B+C) = (A+B) +C

The associative law of multiplication is given

by A. (B.C) = (A.B).C

Distributive Property:

The Boolean addition is distributive over Boolean multiplication,

given by A+BC = (A+B) (A+C)

Boolean multiplication is also distributive over Boolean addition

given by A. (B+C) = A.B+A.C

Realization of circuits for Boolean expression after simplification:

A binary variable can take the value of „0‟ or „1‟. A Boolean function is an

expression formed with binary operator OR, AND and a unary operator NOT,

parenthesis function can be 0 or 1.

For example, consider the function

The prime implicants are found by using the elimination of complementary function. The

circuit diagram for the function is drawn using AND.OR and NOT gates. The output for the

corresponding input of A1, A0, B1, BO is calculated and the truth table is drawn.

Procedure:

1. Test the individual ICs with its specified verification table for proper working.

2. Connections are made as per the circuit/logic diagram.

3. Make sure that the ICs are enabled by giving the suitable Vcc and

ground connections.

4. Apply the logic inputs to the appropriate terminals of the ICs.

5. Observe the logic output for the inputs applied.

6. Verify the observed logic output with the verification/truth table given.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

De-Morgan’s Theorem: 1

De-Morgan’s Theorem: 2

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Commutative Law:

Truth Table:

Input Output

A B A+B B+A

0 0 0 0

0 1 1 1

1 0 1 1

1 1 1 1

Associative Law:

Truth Table:

Input Output

A B C A+B (A+B)+C B+C A+(B+C)

0 0 0 0 0 0 0

0 0 1 0 1 1 1

0 1 0 1 1 1 1

0 1 1 1 1 1 1

1 0 0 1 1 0 1

1 0 1 1 1 1 1

1 1 0 1 1 1 1

1 1 1 1 1 1 1

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Distributive Law:

Truth Table:

Input Output

A B C B+C A.(B+C) A.B A.C A.B+A.C

0 0 0 0 0 0 0 0

0 0 1 1 0 0 0 0

0 1 0 1 0 0 0 0

0 1 1 1 0 0 0 0

1 0 0 0 0 0 0 0

1 0 1 1 1 0 1 1

1 1 0 1 1 1 0 1

1 1 1 1 1 1 1 1

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Result:

Thus the verification of Boolean laws and theorems using basic gates were performed.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

EXP. NO: 2

DATE:

DESIGN AND IMPLEMENTATION OF COMBINATIONAL CIRCUITS USING BASIC

GATES FOR ARBITRARY FUNCTIONS

Aim:

To design and implement a Half/Full Adder and Subtractor (Combinational

Circuit) using basic gates.

Components Required:

S.NO COMPONENTS RANGE QUANTITY

1 Digital IC Trainer kit - 1

7404 1

7408 2

2 IC

7432 1

7486 1

3 Connecting wires - As required

4 Bread board - 1

Theory:

Half Adder

A half-adder is a combinational circuit that can be used to add two binary bits. It has two

inputs that represent the two bits to be added and two outputs, with one producing the SUM

output and the other producing the CARRY.

The SUM output is that of an EX-OR gate, the second one representing the CARRY output

is that of an AND gate.

Full Adder

A full adder is a combinational circuit that forms the arithmetic sum of three input bits. It

consists of 3 inputs and 2 outputs. Two of the input variables, represent the significant bits

to be added. The third input represents the carry from previous lower significant position.

The full adder circuit overcomes the limitation of the half-adder, which can be used to add

two bits only. As there are three input variables, eight different input combinations are

possible. The logic diagram of the full adder can also be implemented with two halfadders

and one OR gate. The S output from the second half adder is the exclusive-OR of Cin and

the output of the first half-adder, giving

Sum = Cin (A B) [xy = x‘y+ xy‘]

= Cin (A‘B+AB‘) = C‘in (A‘B+AB‘) + Cin (A‘B+AB‘)‘ [(x‘y+xy‘)‘= (xy+x‘y‘)]

= C‘in (A‘B+AB‘) + Cin (AB+A‘B‘)

= A‘BC‘in + AB‘C‘in + ABCin + A‘B‘Cin .

The carry output is, Carry,

Cout = AB+ Cin (A’B+AB’)

= AB+ A‘BCin+ AB‘Cin = AB (Cin+1) + A‘BCin+ AB‘Cin [Cin+1= 1]

= ABCin+ AB+ A‘BCin+ AB‘Cin = AB+ ACin (B+B‘) + A‘BCin

= AB+ ACin+ A‘BCin = AB (Cin+1) + ACin+ A‘BCin [Cin+1= 1]

= ABCin+ AB+ ACin+ A‘BCin = AB+ ACin+ BCin (A +A‘) = AB+ ACin+ BCin.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Truth Table for Arbitrary Function:

Input Output

A1 A0 B1 B0 F

0 0 0 0 0 Realization of simplified Boolean

0 0 0 1 0 expression using K-Map:

0 0 1 0 0

0 0 1 1 0

0 1 0 0 1

0 1 0 1 0

0 1 1 0 0

0 1 1 1 0

1 0 0 0 1

1 0 0 1 1

1 0 1 0 0

1 0 1 1 0

1 1 0 0 1

1 1 0 1 1

1 1 1 0 1

1 1 1 1 0

HALF ADDER

Truth Table:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

FULL ADDER

Truth Table: K-Map:

EXP. NO: 3

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

HALF SUBTRACTOR

Truth Table: K-Map:

FULL SUBTRACTOR

Truth Table: K-Map:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Half Subtractor

A half-subtractor is a combinational circuit that can be used to subtract one binary digit

from another to produce a DIFFERENCE output and a BORROW output. The BORROW output

here specifies whether a 1 has been borrowed to perform the subtraction. The DIFFERENCE

(D)output is that of an exclusive-OR gate, the expression for the BORROW output (Bout) is that

of an AND gate with input A complemented before it is fed to the gate. Comparing a half-

subtractor with a half-adder, we find that the expressions for the SUM and DIFFERENCE outputs

are just the same. The expression for BORROW in the case of the half-subtractor is also similar to

what we have for CARRY in the case of the half-adder. If the input A, ie., the minuend is

complemented, an AND gate can be used to implement the BORROW output.

Full Subtractor

A full subtractor performs subtraction operation on two bits, a minuend and a subtrahend,

and also takes into consideration whether a 1 has already been borrowed by the previous adjacent

lower minuend bit or not. As a result, there are three bits to be handled at the input of a full

subtractor, namely the two bits to be subtracted and a borrow bit designated as Bin. There are two

outputs, namely the DIFFERENCE output D and the BORROW output Bo.

The logic diagram of the full-subtractor can also be implemented with two half subtractors and

one OR gate.

The difference, D output from the second half subtractor is the exclusive-OR of Bin and the output

of the first half-subtractor, giving

Difference, D= Bin (A B) [x y = x‘y+ xy‘]

= Bin (A‘B+AB‘) = B‘in (A‘B+AB‘) + Bin (A‘B+AB‘)‘ [(x‘y+xy‘)‘= (xy+x‘y‘)]

= B‘in (A‘B+AB‘) + Bin (AB+A‘B‘)

= A‘BB‘in + AB‘B‘in + ABBin + A‘B‘Bin .

The borrow output is, Borrow,

Bout= A’B+ Bin (A’B+AB’)’ [(x‘y+xy‘)‘= (xy+x‘y‘)]

= A‘B+ Bin (AB+A‘B‘)

= A‘B+ ABBin+ A‘B‘Bin

= A‘B (Bin+1) + ABBin+ A‘B‘Bin [Cin+1= 1]

= A‘BBin+ A‘B+ ABBin+ A‘B‘Bin

= A‘B+ BBin (A+A‘) + A‘B‘Bin [A+A‘= 1]

= A‘B+ BBin+ A‘B‘Bin

= A‘B (Bin+1) + BBin+ A‘B‘Bin [Cin+1= 1]

= A‘BBin+ A‘B+ BBin+ A‘B‘Bin

= A‘B+ BBin+ A‘Bin (B +B‘)

= A‘B+ BBin+ A‘Bin.

Result:

Thus, the Half/Full Adder and Subtractor using basic gates was designed, implemented and

tested its performance with truth table.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

EXP. NO: 3

DATE :

DESIGN AND IMPLEMENTATION OF 4 BIT BINARY ADDER / SUBTRACTOR

Aim:

To design and implement a four bit binary adder / subtractor using MSI devices.

Apparatus Required:

S.NO COMPONENTS RANGE QUANTITY

1 IC trainer kit - 1

7483 1

2 IC‟s

7486 1

3 Connecting wires - -

Theory:

Digital computers perform a variety of information processing tasks. Among the

functions encountered are the various arithmetic operations. The most basic arithmetic

operation is the addition of two binary digits. This simple addition consists of four possible

elementary operations: 0+0=0, 0+1=1, 1+0=0 and 1+1=10.

A binary adder-subtractor is a combinational circuit that performs the arithmetic

operations of addition and subtraction with binary numbers. A combinational circuit that

performs the addition of two bits is called half adder. One that performs the addition of

three bits is a full adder. A binary adder is a digital circuit that produces the arithmetic

sum of two binary numbers.

Procedure:

1. Connect the circuit as per the circuit diagram.

2. Power supply is switched ON and a voltage of 5v is maintained.

3. Four bit binary number is given and verifies the sum result.

4. If the adder or subtractor signal is low addition is performed.

5. If the adder or subtractor signal is high subtractor result is verified.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Logic Diagram:

Pin Diagram:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Verification Table:

Terminology Input Variables Binary inputs

Augend A3 A2 A1 A0

Addend B3 B2 B1 B0

Results Cin Cout

Addition

Subtraction

Result:

Thus the 4 bit parallel adder/subtractor was implemented and tested using the

MSI device – IC 7483.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

EXP. NO:4

DATE :

DESIGN AND IMPLEMENTATION OF CODE CONVERTERS

Aim:

To design and implement of convert gray code to Binary, Binary to Gray Code, BCD

to Excess-3 and Excess-3 to BCD .

Components Required:

S.NO COMPONENTS RANGE QUANTITY

1 Digital IC Trainer kit - 1

7404 1

7408 2

2 IC

7432 1

7486 1

3 Connecting wires - As required

4 Bread board - 1

Theory:

Binary to Gray – Vice versa:

The binary coded decimal (BCD) code is one of the early computer codes. Each decimal

digit is independently converted to a 4 bit binary number. A binary code will have some

unassigned bit combinations if the number of elements in the set is not a multiple power of 2.

The 10 decimal digits form such a set. A binary code that distinguishes among 10 elements

must contain at least four bits, but 6 out of the 16 possible combinations remain unassigned.

Different binary codes can be obtained by arranging four bits in 10 distinct combinations. The

code most commonly used for the decimal digits is the straight binary assignment. This is

called binary coded decimal.

The gray code is used in applications where the normal sequence of binary numbers

may produce an error or ambiguity during the transition from one number to the next. If

binary numbers are used, a change from 0111 to 1100 may produce an intermediate

erroneous number 1001 if the rightmost bit takes longer to change in value than the other

three bits. The gray code eliminates this problem since only one bit changes in value during

any transition between two numbers.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Truth Table (Gray to Binary):

Gray (Input) Binary (Output)

G3 G2 G1 G0 B3 B2 B1 B0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 1

0 1 0 1 0 1 1 0

0 1 1 0 0 1 0 0

0 1 1 1 0 1 0 1

1 0 0 0 1 1 1 1

1 0 0 1 1 1 1 0

1 0 1 0 1 1 0 0

1 0 1 1 1 1 0 1

1 1 0 0 1 0 0 0

1 1 0 1 1 0 0 1

1 1 1 0 1 0 1 1

1 1 1 1 1 0 1 0

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Truth Table (Binary to Gray):

Binary (Input) Gray (Output)

B3 B2 B1 B0 G3 G2 G1 G0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 0

0 1 0 1 0 1 1 1

0 1 1 0 0 1 0 1

0 1 1 1 0 1 0 0

1 0 0 0 1 1 0 0

1 0 0 1 1 1 0 1

1 0 1 0 1 1 1 1

1 0 1 1 1 1 1 0

1 1 0 0 1 0 1 0

1 1 0 1 1 0 1 1

1 1 1 0 1 0 0 1

1 1 1 1 1 0 0 0

Logic Diagram:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

BCD to Excess 3 – Vice versa:

Excess 3 code is a modified form of a BCD number. The excess 3 code can be

derived from the natural BCD code by adding 3 to each coded number. For example,

decimal 6 can be represented in BCD as 0110. Now adding 3 to the given number yield

equivalent excess 3 code i.e., 6 + 3 = 9 0110 + 0011 = 1001. Thus for the entire

sequence of BCD value (i.e., 0 to 9) excess 3 equivalent table should be made so that the

realization of Boolean expression for the circuit implementation is feasible. In the reverse

process of designing a code converter from excess 3 to BCD the same procedure is

followed. Here are the general steps to be followed while going for a code converter

design,

– start with the specification of the circuit to be designed.

– Identify the inputs and outputs

– Derive truth table

– Obtain simplified Boolean equations

– Draw the logic diagram

– Check the design to verify correctness with the truth/verification table.

Procedure:

1. Test the individual ICs with its specified verification table for proper working.

2. Connections are made as per the circuit/logic diagram.

3. Make sure that the ICs are enabled by giving the suitable Vcc and

ground connections.

4. Apply the logic inputs to the appropriate terminals of the ICs.

5. Observe the logic output for the inputs applied.

Verify the observed logic output with the verification/truth table given.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Truth Table:

BCD Input Excess 3 output

Decimal

Value A B C D W X Y z

0 0 0 0 0 0 0 1 1

1 0 0 0 1 0 1 0 0

2 0 0 1 0 0 1 0 1

3 0 0 1 1 0 1 1 0

4 0 1 0 0 0 1 1 1

5 0 1 0 1 1 0 0 0

6 0 1 1 0 1 0 0 1

7 0 1 1 1 1 0 1 0

8 1 0 0 0 1 0 1 1

9 1 0 0 1 1 1 0 0

Realization of Boolean Expression for BCD to Excess 3 Converter:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Circuit Diagram:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Truth Table:

Decimal Excess 3 Input BCD Output

Value

W X Y z A B C D

0 0 0 1 1 0 0 0 0

1 0 1 0 0 0 0 0 1

2 0 1 0 1 0 0 1 0

3 0 1 1 0 0 0 1 1

4 0 1 1 1 0 1 0 0

5 1 0 0 0 0 1 0 1

6 1 0 0 1 0 1 1 0

7 1 0 1 0 0 1 1 1

8 1 0 1 1 1 0 0 0

9 1 1 0 0 1 0 0 1

Realization of Boolean Expression for Excess 3 to BCD Converter:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Circuit Diagram:

Result:

Thus, the code converter using logic gates were designed, implemented

andtested with truth table.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

EXP. NO: 5

DATE:

IMPLEMENTATION OF BCD ADDER ENCODER AND DECODER CIRCUITS

Aim:

To design and implement BCD adder, Encoder and Decoder Circuits

Apparatus Required:

S.NO COMPONENTS RANGE QUANTITY

1 IC trainer kit - 1

7483 1

2 IC‟s 7410 2

7404 1

7432 1

3 Connecting wires - -

Theory:

Decimal Adder (BCD Adder): The digital system handles the decimal number in the form of

binary coded decimal numbers (BCD). A BCD adder is a circuit that adds two BCD bits and

produces a sum digit also in BCD. Consider the arithmetic addition of two decimal digits in BCD,

together with an input carry from a previous stage. Since each input digit does not exceed 9, the

output sum cannot be greater than 9+ 9+1 = 19; the 1 is the sum being an input carry. The adder

will form the sum in binary and produce a result that ranges from 0 through 19. These binary

numbers are labeled by symbols K, Z8, Z4, Z2, Z1, K is the carry. The columns under the binary

sum list the binary values that appear in the outputs of the 4- bit binary adder. The output sum of

the two decimal digits must be represented in BCD.

In examining the contents of the table, it is apparent that when the binary sum is equal to or less

than 1001, the corresponding BCD number is identical, and therefore no conversion is needed.

When the binary sum is greater than 9 (1001), we obtain a non-valid BCD representation. The

addition of binary 6 (0110) to the binary sum converts it to the correct BCD representation and

also produces an output carry as required. The logic circuit to detect sum greater than 9 can be

determined by simplifying the Boolean expression of the given truth table.

To implement BCD adder we require:

• 4-bit binary adder for initial addition

• Logic circuit to detect sum greater than 9 and

• One more 4-bit adder to add 01102 in the sum if the sum is greater than 9 or carry is 1.

The two decimal digits, together with the input carry, are first added in the top4- bit binary adder

to provide the binary sum. When the output carry is equal to zero, nothing is added to the binary

sum. When it is equal to one, binary 0110 is added to the binary sum through the bottom 4-bit

adder. The output carry generated from the bottom adder can be ignored, since it supplies

information already available at the output carry terminal. The output carry from one stage must

be connected to the input carry of the next higher-order stage.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

BCD ADDER

Truth Table:

Logic Diagram:

Verification Table:

Terminology Input Variables Binary inputs

Augend A3 A2 A1 A0

Addend B3 B2 B1 B0

Results

Addition

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

LOGIC DIAGRAM FOR ENCODER:

TRUTH TABLE:

INPUT OUTPUT

Y1 Y2 Y3 Y4 Y5 Y6 Y7 A B C

1 0 0 0 0 0 0 0 0 1

0 1 0 0 0 0 0 0 1 0

0 0 1 0 0 0 0 0 1 1

0 0 0 1 0 0 0 1 0 0

0 0 0 0 1 0 0 1 0 1

0 0 0 0 0 1 0 1 1 0

0 0 0 0 0 0 1 1 1 1

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

ENCODER:

An encoder is a digital circuit that performs inverse operation of a decoder. An encoder has

2n input lines and n output lines. In encoder the output lines generates the binary code

corresponding to the input value. In octal to binary encoder it has eight inputs, one for each octal

digit and three output that generate the corresponding binary code. In encoder it is assumed that

only one input has a value of one at any given time otherwise the circuit is meaningless. It has an

ambiguila that when all inputs are zero the outputs are zero. The zero outputs can also be generated

when D0 = 1.

DECODER:

A decoder is a multiple input multiple output logic circuit which converts coded input into

coded output where input and output codes are different. The input code generally has fewer bits

than the output code. Each input code word produces a different output code word i.e. there is one

to one mapping can be expressed in truth table. In the block diagram of decoder circuit the encoded

information is present as n input producing 2n possible outputs. 2n output values are from 0 through

out 2n – 1.

Procedure:

1. Connect the circuit as per the circuit diagram.

2. Power supply is switched ON and a voltage of 5v is maintained.

3. Four bit binary number is given and verifies the sum result.

4. If the adder or subtractor signal is low addition is performed.

5. If the adder or subtractor signal is high subtractor result is verified.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

LOGIC DIAGRAM FOR DECODER:

TRUTH TABLE:

INPUT OUTPUT

E A B D0 D1 D2 D3

1 0 0 1 1 1 1

0 0 0 0 1 1 1

0 0 1 1 0 1 1

0 1 0 1 1 0 1

0 1 1 1 1 1 0

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

RESULT:

Thus, the BCD Adder, the encoder and decoder have been implemented.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

EXP. NO: 6

DATE :

IMPLEMENTATION OF FUNCTIONS USING MULTIPLEXERS

Aim: To design and implement the combinational logic using multiplexers

Components required:

S. Components Name Range Type Quantity

No

1 Digital IC trainer kit - - 1

2 IC - 74151 2

3 Connecting wires - - As required

Theory:

The Block diagram shows the implementation of Boolean function using 8:1

multiplexer. The implementation table is nothing but the list of the inputs of the multiplexer

and under them list of all the minterms in two columns. The first column lists all the minterms

where least significant variable is complemented (C’), and the second column lists all the

minterms with least significant variable is un-complemented (C). The minterms given in the

function are circled and then each row is inspected separately as follows.

Procedure:

1. Test the individual ICs with its specified verification table for proper working.

2. Connections are made as per the circuit/logic diagram.

3. Make sure that the ICs are enabled by giving the suitable Vcc and ground

connections.

4. Apply the logic inputs to the appropriate terminals of the ICs.

5. Observe the logic output for the inputs applied.

6. Verify the observed logic output with the verification/truth table given.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Implementation of the following Boolean function F=Σ m (2, 3, 6, 7) using multiplexer

Truth table

Inputs Output

Minterm

A B C (F)

0 0 0 0 0

1 0 0 1 0

2 0 1 0 1

3 0 1 1 1

4 1 0 0 0

5 1 0 1 0

6 1 1 0 1

7 1 1 1 1

Pin diagram:

Result:

Thus, the implementation of the given Boolean function using multiplexer was

designed, implemented and verified with its truth table.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

EXP. NO: 7

DATE :

DESIGN AND IMPLEMENTATION OF SYNCHRONOUS COUNTER

Aim:

To design and implement a 3-bit synchronous binary up and down counter using JK

flip- flop.

Components Required:

S.NO COMPONENTS RANGE QUANTITY

1 Digital Trainer Kit - 1

7476 2

2 IC’s 7408 1

7432 1

3 Connecting wires - As required

4 Bread Board - 1

Theory:

A Synchronous counter is also called parallel counter. In this counter the clock inputs

of all the flip-flops are connected together so that the input clock signal is applied

simultaneously to each flip-flop. Also, only the LSB flip-flop C has its J and K inputs connected

permanently to Vcc while the J and K inputs of the other flip-flops are driven by some

combination of flip-flop outputs.

3 – Bit Synchronous Binary UP Counter:

The J and K inputs of the flip-flop B are connected to with QC. The J and K inputs of

the flip-flop A, are connected with AND operated output of QC and QB. The flip-flop C

changes its state when with the occurrence of negative transition at each clock pulse. The flip-

flop B changes its state when QC = 1 and when there is negative transition at clock input. Flip-

flop A changes its state when QC = QB = 1 and when there is negative transition at clock input.

3 – Bit Synchronous Binary DOWN Counter:

The J and K inputs of the flip-flop B are connected to with QC’. The J and K inputs

of the flip-flop A, are connected with AND operated output of QC’ and QB’. The flip-flop

C changes its state when with the occurrence of negative transition at each clock pulse. The

flip-flop B changes its state when QC’ = 1 and when there is negative transition at clock

input. Flip-flop A changes its state when QC’ = QB’ = 1 and when there is negative

transition at clock input.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

State Table (3 – bit synchronous binary UP counter)

Present State Next State JK Flip-Flop Inputs

A B C A B C JA KA JB KB JC KC

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

State Table (3 – bit synchronous binary DOWN counter)

Present State Next State JK Flip-Flop Inputs

A B C A B C JA KA JB KB JC KC

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

JK Excitation Table:

Qn Qn+1 J K

0 0 0 X

0 1 1 X

1 0 X 1

1 1 X 0

Result:

Thus the synchronous up and down counters were designed using JK flip-flop and

verified with their state table.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

EXP. NO: 8

DATE :

IMPLEMENTATION OF UNIVERSAL SHIFT REGISTERS

Aim:

To design, implement and verify the functioning of Universal shift right register using

D flip-flop.

Components Required:

S.NO COMPONENTS RANGE QUANTITY

1 Digital IC trainer kit - 1

7474 2

7404 1

2 ICs

74151 or 74153 2

3 Connecting wires - -

4 Bread Board - 1

Theory:

A register that is used to store binary information is known as a memory register. A register

capable of shifting binary information either to the right or the left is called a shift register. Shift registers

are classified into four types,

1. Serial-in Serial-out (SISO)

2. Serial-in Parallel-out (SIPO)

3. Parallel-in Serial-out (PISO)

4. Parallel-in Parallel-out (PIPO) Serial-in

Serial-out (SISO):

This type of shift registers accepts data serially, i.e., one bit at a time on a single input line. It

produces the stored information on its single output and the output also in serial form. Data may be

shifted left (from low to high order bits) using shift-left register or shifted right (from high to low order

bits) using shift-right register.

Serial-in Parallel-out (SIPO):

It consists of one serial input, and outputs are taken from all the flip-flop simultaneously in parallel.

In this register, data is shifted in serially but shifted out in parallel. In order to shift the data out in

parallel, it is necessary to have all the data available at the outputs at the same time. Once the data is

stored, each bit appears on its respective output line and all the bits are available simultaneously, rather

than on a bit by bit basis as with the serial output.

Procedure:

1. Test the individual ICs with its specified verification table for proper working.

2. Connections are made as per the circuit/logic diagram.

3. Make sure that the ICs are enabled by giving the suitable Vcc and ground connections.

4. Apply the logic inputs to the appropriate terminals of the ICs.

5. Observe the logic output for the inputs applied.

6. Verify the observed logic output with the verification/truth table given.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Pin Diagram:

Circuit Diagram: Serial IN Serial OUT shift Register

Circuit Diagram: Serial IN Parallel OUT shift Register

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Verification Table:

Result:

Thus, the Universal shift register using D flip-flop were implemented and studied the

operation in 2 different modes.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

EXP. NO: 9 SIMULATION BASED STUDY OF COMPUTER ARCHITECTURE

DATE :

Aim:

To study about the single instruction execution using design of a single instruction CPU.

Procedure:

This experiment study was performed using virtual labs from MHRD. It is an online virtual platform for

performing practical experiments under different disciplines. This experiment was performed using Logic

Design and Computer Organization laboratory from vlabs.

The link for performing the simulation is http://vlabs.iitkgp.ac.in/coa/exp12/index.html

Procedure to perform the experiment: CPU Design

1. Start the simulator as directed. This simulator supports 5-valued logic.

2. To perform the experiment on the given modules, we need the CPU, the working memory with a

program and data loaded, a clock input, Bit switch(to give input,which will toggle its value with a

double click), Bit displays(for seeing output), wires.

3. Load memory: click on the load memory button in the left pane. you can either load the memory by

filling the form or you can directly load the program form a text file. The memory provides 4-bit

address space and 12 bit data word, thus providing 16 memory address starting from 0000 to 1111.

For loading from file, the file should contain only binary values, it must contain 16 lines, each line

containing the content to be stored in the corresponding memory address. For example, content of

first line will be loaded to the 0000 address of the memory, similarly, the second line will correspond

to the 0001 address and so on, finally the content of last line will be fed to the 1111 address. The

progrm should use self loop for halting, for example, the instruction stored at address 1010 will cause

self loop execution, if it content of a has -1 in binary format (in 2's complement), the content of b has

0 and c is 1010, then once the execution reaches to this 1010 address, it will finally point to itself.

4. Instantiating the memory: after loading the memory, click on the memory component from the

computer design drawer in the palette of the simulator then click on the position of the design editor

where you want to put the component(no drag and drop, simple click will serve the purpose).

5. The pin configuration of the component is shown whenever the mouse is hovered on any canned

component of the palette or pressing the show pin configuration button on the toolbar will show it

constantly in the left pane. Pin numbering starts from 1 and from the bottom left corner(indicating

with the circle) and increases anticlockwise.

6. Pin configuration of the memory module:

o Input pins (upper terminals): memory enable : 30, R/W' : 29, address : 25-28, data : 13-24

(13 is LSB)

o Output pins(lower terminals): data output : 1-12 (1 is MSB)

7. Instantiate the CPU from the computer design drawer in the palette of the simulator then click on the

position of the design editor where you want to put the component.

8. Pin configuration of the CPU:

o Input pins (upper terminals): data input : 20-31 (20 is MSB) ,clock input : 19

o Output pins(lower terminals): memory enable : 1, R/W' : 2, address : 3-6( 3 is MSB), data

output : 7-18 (7 is MSB)

9. To connect any two components select the Connection menu of Palette, and then click on the Source

terminal and click on the target terminal. According to the following diagram connect all the

components. Connect the memory outputs to the input terminals of the CPU, specified datapath

outputs to the inputs of the controller, the clock input, Bit switches with the inputs and Bit displays

component with the outputs (from Display and Input drawer of the pallet,if it is not seen scroll down

in the drawer). After the connection is over click the selection tool in the pallete.

10. Start clock and observe the behavior of the CPU. See the content of memory by clicking show

memory button in the left pane. Observe how the program is executing sequentially and modify the

data content as per the program.

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

Java based simulator is used and the output screen shots obtained are given below:

Output Screenshots from the Simulator:

(i) CPU and Memory Added in the simulator:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

(ii) CPU and Memory Added with clock pulse in the simulator:

(iv) CPU and Memory with changing clock pulse in the simulator:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

(iv) CPU and Memory connected with address and data lines with clock pulse in

the simulator:

(v) CPU and Memory connected with loaded Memory option:

Downloaded by priya S (nietpriya@nehrucolleges.com)

lOMoARcPSD|6634547

(vi) CPU and Memory connected with Memory loaded with data under Execution:

Result:

Thus, the execution of single instruction using design of a single instruction CPU

using virtual labs simulator is studied.

Downloaded by priya S (nietpriya@nehrucolleges.com)

You might also like

- Dpco LabDocument43 pagesDpco Labpriya SNo ratings yet

- Cs3351-Dpco Lab ManualDocument42 pagesCs3351-Dpco Lab Manual19UBCA105 SASIREKA A100% (2)

- RIVERA Logics - Lab 7Document5 pagesRIVERA Logics - Lab 7Ricardo Edrell RiveraNo ratings yet

- DLD Manual - EXP - 3Document3 pagesDLD Manual - EXP - 3Ahmad RazaNo ratings yet

- Recent PHD ResultDocument72 pagesRecent PHD ResultSavita Kiran BNo ratings yet

- Digital Lab ReportDocument9 pagesDigital Lab ReportNg Ming FengNo ratings yet

- A - 29 - Pratham - Katariya DSD Exp-1Document5 pagesA - 29 - Pratham - Katariya DSD Exp-1pratham.22211592No ratings yet

- RIVERA Logics - Lab 8Document5 pagesRIVERA Logics - Lab 8Ricardo Edrell RiveraNo ratings yet

- Lab No. 6: Understanding The Simplification by Boolean Algebra, Truth Table and Karnaugh MapDocument4 pagesLab No. 6: Understanding The Simplification by Boolean Algebra, Truth Table and Karnaugh MapInam Ur RehmanNo ratings yet

- Aboratory ILE: Computer Organization & Architecture LabDocument21 pagesAboratory ILE: Computer Organization & Architecture LabRahul GuptaNo ratings yet

- FDDGDocument3 pagesFDDGaliffpadziNo ratings yet

- PCB Reprt (1) FinalDocument8 pagesPCB Reprt (1) FinalShamma SNo ratings yet

- Experiment 2 FinalDocument9 pagesExperiment 2 Finalliddleme33No ratings yet

- Practical 9DLDDocument3 pagesPractical 9DLDAbbas AbbasiNo ratings yet

- Experiment No. 1 Design and Implementation of Basic Logic Gates and Combinational CircuitsDocument17 pagesExperiment No. 1 Design and Implementation of Basic Logic Gates and Combinational CircuitsUnlimited XfinityNo ratings yet

- Combinational Circuits Penned by Faisal HaroonDocument5 pagesCombinational Circuits Penned by Faisal HaroonFaisal HaroonNo ratings yet

- 0008-BSCS-19 MUHAMMAD JUNAID TARIQ (DLD Lab) Word FileDocument6 pages0008-BSCS-19 MUHAMMAD JUNAID TARIQ (DLD Lab) Word FileKashif KashifNo ratings yet

- Complete PracticalDocument16 pagesComplete PracticalshabbirjamaliNo ratings yet

- Computer Organization and Architecture Lab: Mr. Laxmi Kant Sagar Vishal Sharma 1901920100328Document28 pagesComputer Organization and Architecture Lab: Mr. Laxmi Kant Sagar Vishal Sharma 1901920100328ayushNo ratings yet

- Digital Logic Circuits Analysis and Converting Boolean Expressions To Digital CircuitsDocument10 pagesDigital Logic Circuits Analysis and Converting Boolean Expressions To Digital CircuitsSalam ShaikhNo ratings yet

- Best Lab ExpsDocument45 pagesBest Lab ExpsshivaNo ratings yet

- Lab Journal 3 30032024 104144pmDocument7 pagesLab Journal 3 30032024 104144pmMuhammad bilalNo ratings yet

- ECE 279 Exp. 1 To Exp 10Document29 pagesECE 279 Exp. 1 To Exp 10Shruti KumariNo ratings yet

- Computer Organization and Architecture Lab: G L Bajaj Institute of Technology and Management Greater Noida - 201306Document28 pagesComputer Organization and Architecture Lab: G L Bajaj Institute of Technology and Management Greater Noida - 201306Anshika Chauhan100% (2)

- Lab Report #6Document6 pagesLab Report #6افنان ديريةNo ratings yet

- Co Lab ManualDocument81 pagesCo Lab ManualShiva KumarNo ratings yet

- Tutorial 2 - Electronics (2018)Document3 pagesTutorial 2 - Electronics (2018)Pasindu PramodNo ratings yet

- Experiment 7Document7 pagesExperiment 7Karan KumarNo ratings yet

- Experiment-4,5 Abhay - Prabhakar 2010990014Document9 pagesExperiment-4,5 Abhay - Prabhakar 2010990014abhay prabhakarNo ratings yet

- Lab Rep 3-4Document7 pagesLab Rep 3-4Muhammad Hamza TariqNo ratings yet

- DLD HWDocument17 pagesDLD HWNấm LùnNo ratings yet

- CS3352 - Digital Principles and Computer Organization LaboratoryDocument55 pagesCS3352 - Digital Principles and Computer Organization Laboratoryakshaya vijay100% (6)

- Cse 206 - Lab 05Document4 pagesCse 206 - Lab 05Syed IrfanNo ratings yet

- Computer Servicing 4: Introduction To Logic Gates Boolean AlgebraDocument13 pagesComputer Servicing 4: Introduction To Logic Gates Boolean AlgebraJhon Keneth NamiasNo ratings yet

- Course Title: Digital Design Lab: Bahria University, IslamabadDocument15 pagesCourse Title: Digital Design Lab: Bahria University, IslamabadshahwaizNo ratings yet

- Assignment 1Document41 pagesAssignment 1Sai BharathNo ratings yet

- Department of Software Engineering: Faculty Member: Ma'am Quartulain Dated: 3-20-2021Document9 pagesDepartment of Software Engineering: Faculty Member: Ma'am Quartulain Dated: 3-20-2021Muhammad RehanNo ratings yet

- RIVERA LOGICS - Lab 6Document4 pagesRIVERA LOGICS - Lab 6Ricardo Edrell RiveraNo ratings yet

- Lab 3 Group 2 Haziq & AdamDocument16 pagesLab 3 Group 2 Haziq & AdamShamalen RajanNo ratings yet

- RIVERA LOGIC CIRCUITS - Lab 4Document5 pagesRIVERA LOGIC CIRCUITS - Lab 4Ricardo Edrell RiveraNo ratings yet

- Digital Logic Design - Lecture 05 - 2Document58 pagesDigital Logic Design - Lecture 05 - 2Haider AliNo ratings yet

- School of Engineering and Physics EE222 Lab 5Document9 pagesSchool of Engineering and Physics EE222 Lab 5Alvish NaiduNo ratings yet

- BI2002B - Circuitos LógicosDocument30 pagesBI2002B - Circuitos LógicosHéctor Vega SantamaríaNo ratings yet

- Assement 04Document5 pagesAssement 04Naina PrasharNo ratings yet

- Rajshahi University of Engineering & Technology: Heaven's Light Is Our GuideDocument38 pagesRajshahi University of Engineering & Technology: Heaven's Light Is Our GuideNafis HasanNo ratings yet

- 15.3 Hardware Cambridge CS A2Document5 pages15.3 Hardware Cambridge CS A2chirantha150No ratings yet

- Lab Report 5Document18 pagesLab Report 5Umair WaqasNo ratings yet

- Lab Assignment Digital Design - نسخةDocument5 pagesLab Assignment Digital Design - نسخةMaged SarhanNo ratings yet

- Addition Function in Logic GateDocument5 pagesAddition Function in Logic GateYosif AlanesiNo ratings yet

- Expt 06-1Document5 pagesExpt 06-1Aurongo NasirNo ratings yet

- LAB 1 - Basic Logic Gates - BERMUDEZ. - BSECE-3ADocument18 pagesLAB 1 - Basic Logic Gates - BERMUDEZ. - BSECE-3AJenny A. BermudezNo ratings yet

- Expt-8-Elements of Electronics EngineeringDocument12 pagesExpt-8-Elements of Electronics Engineeringshreyas.aiml01No ratings yet

- Exp9 1Document3 pagesExp9 1Ashley De LeonNo ratings yet

- Dpco Lab ManuaDocument54 pagesDpco Lab ManuaHANISHA SAALIHNo ratings yet

- DCLD Exp 1Document6 pagesDCLD Exp 1Prabh deepNo ratings yet

- Logic GatesDocument6 pagesLogic GatesMehar GuptaNo ratings yet

- HardaddsoftDocument8 pagesHardaddsoftSHYAMNo ratings yet

- CSE 1204 DLD Lab ManualDocument66 pagesCSE 1204 DLD Lab Manualrafsan220719No ratings yet

- RIVERA LOGIC CIRCUITS - Lab 2Document7 pagesRIVERA LOGIC CIRCUITS - Lab 2Ricardo Edrell RiveraNo ratings yet

- Dpco LabDocument43 pagesDpco Labpriya SNo ratings yet

- Review Internal I OME753Document22 pagesReview Internal I OME753priya SNo ratings yet

- Review Internal I OME753Document22 pagesReview Internal I OME753priya SNo ratings yet

- Dig Lab Manual CS8382Document53 pagesDig Lab Manual CS8382priya SNo ratings yet

- R-21 Iat QP CD2Document4 pagesR-21 Iat QP CD2priya SNo ratings yet

- Review Internal I OME753Document22 pagesReview Internal I OME753priya SNo ratings yet

- Dig Lab Manual CS8382Document53 pagesDig Lab Manual CS8382priya SNo ratings yet

- Digital Electronics Lab ManualDocument107 pagesDigital Electronics Lab ManualStephen Pranay ChelumallaNo ratings yet

- DD Practicals Master ManualDocument58 pagesDD Practicals Master Manualraghu_chandra_3No ratings yet

- Dica Lab ManualDocument88 pagesDica Lab ManualRaghavendra RaghavaNo ratings yet

- Practical and Project Copy DLD by HUSNAIN RAMZANDocument11 pagesPractical and Project Copy DLD by HUSNAIN RAMZANHasnain KhanNo ratings yet

- Design and Implementation of Full Subtractor Using CMOS 180nm TechnologyDocument6 pagesDesign and Implementation of Full Subtractor Using CMOS 180nm TechnologyBhaskar KNo ratings yet

- Lab Rep 3-4Document7 pagesLab Rep 3-4Muhammad Hamza TariqNo ratings yet

- BLM221 Week 5 Minterm MaxtermDocument79 pagesBLM221 Week 5 Minterm MaxtermHasbiy RobbiyNo ratings yet

- DPSD Lecture NotesDocument108 pagesDPSD Lecture NotesAnonymous OmVLB3lJNo ratings yet

- COA Lab ManualDocument13 pagesCOA Lab Manualsravanicharitha MamidiNo ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230104435 Reference Material I 16-09-2022 Module 4 - Design of Data PathsDocument27 pagesFALLSEM2022-23 BECE102L TH VL2022230104435 Reference Material I 16-09-2022 Module 4 - Design of Data PathsVarunNo ratings yet

- Lab 5 - Combinational Logic-Adders and SubtractorsDocument11 pagesLab 5 - Combinational Logic-Adders and SubtractorsAngelicaNo ratings yet

- Verilog EXPERIMENT 2Document11 pagesVerilog EXPERIMENT 2udayNo ratings yet

- Adder and Subtractor Circuits PDFDocument8 pagesAdder and Subtractor Circuits PDFSoumya Ranjan MohantyNo ratings yet

- Multiplexer & de Multiplexer-4Document48 pagesMultiplexer & de Multiplexer-4Mritunjay YadavNo ratings yet

- Binary Adder: A Full Adder CircuitDocument8 pagesBinary Adder: A Full Adder CircuitSejal KankriyaNo ratings yet

- A.V.C.College of Engineering Mannampandal, Mayiladuthurai-609 305Document111 pagesA.V.C.College of Engineering Mannampandal, Mayiladuthurai-609 305Laks Sadeesh100% (1)

- Lic Lab MannualDocument103 pagesLic Lab MannualAnusha NatarajanNo ratings yet

- SubtractorDocument11 pagesSubtractorRocky SamratNo ratings yet

- Experiment 3: BackgroundDocument6 pagesExperiment 3: Backgroundmunib zafarNo ratings yet

- CA PracticalDocument29 pagesCA PracticalDurgesh DhoreNo ratings yet

- Quiz U2Document12 pagesQuiz U2pavithra.jNo ratings yet

- Post LabDocument25 pagesPost LabMugunthan KrishnaNo ratings yet

- Module 7 - Digital Arithmetic CircuitDocument9 pagesModule 7 - Digital Arithmetic CircuitFebruaryNo ratings yet

- DSDV Complete NotespdfDocument82 pagesDSDV Complete Notespdfjainhassan4848No ratings yet

- cs3351 Lab Manual FinalDocument64 pagescs3351 Lab Manual FinalNajih RafeequeNo ratings yet

- Exp. LogicDocument2 pagesExp. LogicJhon David TabunanNo ratings yet

- Half Adder, Full Adder, MultiplierDocument7 pagesHalf Adder, Full Adder, MultiplierDemin revisNo ratings yet

- Full SubtractorDocument6 pagesFull SubtractorPrerna Sharma100% (1)

- LT Teacher Computer Science BookDocument70 pagesLT Teacher Computer Science BookraghaveshideaNo ratings yet

- CSC 209 Notes SplitDocument57 pagesCSC 209 Notes SplitBello TaiwoNo ratings yet