Professional Documents

Culture Documents

Expt 06-1

Uploaded by

Aurongo NasirOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Expt 06-1

Uploaded by

Aurongo NasirCopyright:

Available Formats

EXPT.

NO: 06

SEC: A1

NAME OF THE EXPT: ARITHMATIC CIRCUIT DESIGN

ROLL NO: 0106031

OBJECTIVE:

The objective of this experiment is to design arithmetic circuits using logic gates and implement of

those circuits.

PROBLEMS:

1. Using IC-74154 design a 2-bit comparator to compare 2-bit numbers P and Q. The circuit

should provide 3 output lines to indicate P>Q, P=Q and P<Q

2. Design a 1-bit full sub tractor circuit using basic logic gates

3. Design a 4-bit CLA (Carry Look Ahead) adder circuit.

REQUIRED INSTRUMENTS:

No Name Model Quantity

1. Trainer Board 1 piece

2. IC – Extractor 1 piece

3. IC (4 to 16 Decoder) 74LS154 1 piece

4. IC ( Hex-Inverter) 74LS04 1 piece

5. IC (Quad 2 input AND) 74LS08 1 piece

6. IC (Quad 2 input OR) 74LS32 1 piece

7. IC (8 input NAND Gate) 74LS30 2 piece

8. IC (Dual 4 input NAND Gate) 74LS20 1 piece

9. IC (Quad 2 input XOR Gate) 74LS86 1 piece

10. IC (Look Ahead Carry Generator) 74LS182 1 piece

11. Wires A lot

12. Hand Book 1 piece

PROBLEM -01: Using IC-74154 design a 2-bit comparator to compare 2-bit numbers P and Q. The

circuit should provide 3 output lines to indicate P>Q, P=Q and P<Q

TRUTH TABLE:

A B f1 f2 f3

A1 A0 B1 B0 A>B A=B A<B

0 0 0 0 0 1 0

0 0 0 1 0 0 1

0 0 1 0 0 0 1

0 0 1 1 0 0 1

0 1 0 0 1 0 0

0 1 0 1 0 1 0

0 1 1 0 0 0 1

0 1 1 1 0 0 1

1 0 0 0 1 0 0

1 0 0 1 1 0 0

1 0 1 0 0 1 0

1 0 1 1 0 0 1

1 1 0 0 1 0 0

1 1 0 1 1 0 0

1 1 1 0 1 0 0

1 1 1 1 0 1 0

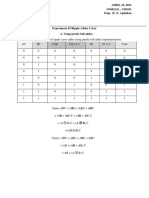

FUNCTION SIMPLIFICATION:

From the truth table we can see that,

F1 = m4 m8 m9 m12 m13 m14 m4 m8 m9 m12 m13 m14 M 4 M 8 M 9 M 12 M 13 M 14

F2 = m0 m5 m10 m15 m0 m5 m10 m15 M 0 M 5 M 10 M 15

F3 = m1 m2 m3 m6 m7 m11 m1 m2 m3 m6 m7 m11 M 1 M 2 M 3 M 6 M 7 M 11

CIRCUIT DIAGRAM AND PIN SPECIFICATIONS:

PROBLEM -02: Design a 1-bit full sub tractor circuit using basic logic gates

TRUTH TABLE:

X Y Z X-Y-Z

C S

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 1 0

1 0 0 0 1

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

FUNCTION MINIMIZATION:

From the truth table we can see that,

S = X’Y’Z + X’YZ’+XY’Z’+XYZ

=>S = Z(X’Y’+XY) +Z’(X’Y+XY’)

=>S=Z(XY)+Z’(XY)

=>S=Z(XY)’+Z’(XY)

=>S=XYZ

So S = XYZ

And

C=X’Y’Z+ X’YZ’+ X’YZ+ XYZ

=>C=Z(X’Y’+XY)+X’Y(Z+Z’)

=>C=Z(XY)+X’Y

So C= Z(XY)+X’Y

CIRCUIT DIAGRAM AND PIN SPECIFICATION:

PROBLEM -03: Design a 4-bit CLA (Carry Look Ahead) adder circuit.

Let, AA3A2A1A0 And BB3B2B1B0 are two 4-bit binary number.

TRUTH TABLE:

Ai Bi Ci Si

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

FUNCTION SIMPLIFICATION:

Pi Carry Propagator

Gi Carry Generator

And By definition,

Pi =Ai Bi

G i = A i Bi

Si = Ai Bi Ci = Pi Ci

Ci+1 = AiBi + (Ai Bi) Ci = Gi + PiCi

Then,

1. P0 =A0B0 ; P1 =A1B1 ; P2 =A2B2 ; P3 =A3B3

2. G0=A0B0 ; G1=A1B1 ; G2=A2B2 ; G3=A3B3 ;

3. S0=P0C0 ; S1=P1C1 ; S2=P2C2 ; S3=P3C3 ;

C1 = G0 + P0C0

C2 = G1 + P1C1=G1+P1(G0 +P0C0)=G1+P1G0+P1P0C0

C3 = G2+P2C2=G2+ P2G1+P2P1G0+P2P1P0C0

C4 = G3+P3C3=G3+ P3G2+P3P2G1+P3P2P1G0+P3 P2 P1 P0 C0

And

If we consider, G=G3+P3G2+P3P2G1+P3P2P1G0 & P= P3 P2 P1 P0

C4 = G +C0P

CIRCUIT DIAGRAM AND PIN SPECIFICATIONS:

You might also like

- Cost Estimating Manual for Pipelines and Marine Structures: New Printing 1999From EverandCost Estimating Manual for Pipelines and Marine Structures: New Printing 1999Rating: 5 out of 5 stars5/5 (2)

- Chapter 4Document17 pagesChapter 4haiqa suhailNo ratings yet

- Digital DesignDocument4 pagesDigital DesignHasan CanarslanNo ratings yet

- Rajshahi University of Engineering & Technology: Heaven's Light Is Our GuideDocument38 pagesRajshahi University of Engineering & Technology: Heaven's Light Is Our GuideNafis HasanNo ratings yet

- Circuit DesignDocument15 pagesCircuit DesignHafiezul HassanNo ratings yet

- School of Engineering and Physics EE222 Lab 5Document9 pagesSchool of Engineering and Physics EE222 Lab 5Alvish NaiduNo ratings yet

- Ee222 Lab 3Document9 pagesEe222 Lab 3Jakob NandNo ratings yet

- Digital ElectronicsDocument3 pagesDigital Electronicsappbrk40No ratings yet

- Low Power IC Design: AOI Gate AnalysisDocument19 pagesLow Power IC Design: AOI Gate AnalysisPrìñçé ÅsîfNo ratings yet

- Assignment 1Document41 pagesAssignment 1Sai BharathNo ratings yet

- Combinational Circuit DesignDocument12 pagesCombinational Circuit DesignMuhammad WasiNo ratings yet

- Digital Logic and Microprocessor Lab Assessment 3Document10 pagesDigital Logic and Microprocessor Lab Assessment 3ANKITNo ratings yet

- Digital Electronics - Tutorial #4Document2 pagesDigital Electronics - Tutorial #4Dishawn NationNo ratings yet

- Experiment 7Document7 pagesExperiment 7Karan KumarNo ratings yet

- Digital Logic Circuit Design Experiemnet 8Document8 pagesDigital Logic Circuit Design Experiemnet 8fahadNo ratings yet

- Register Number: 2141121 Name: Kunal N Jain Class: 1 BCA B Date/Time: 30/11/21Document5 pagesRegister Number: 2141121 Name: Kunal N Jain Class: 1 BCA B Date/Time: 30/11/21Kunal N JainNo ratings yet

- Experiment-4,5 Abhay - Prabhakar 2010990014Document9 pagesExperiment-4,5 Abhay - Prabhakar 2010990014abhay prabhakarNo ratings yet

- CD4511 BCD To 7-Segment DecoderDocument9 pagesCD4511 BCD To 7-Segment DecoderBon Ndu OsonwanneNo ratings yet

- Lab 3Document7 pagesLab 32221634No ratings yet

- Experiment 2 SALAZARDocument9 pagesExperiment 2 SALAZARgerand salazarNo ratings yet

- DLD HWDocument17 pagesDLD HWNấm LùnNo ratings yet

- Practical 9DLDDocument3 pagesPractical 9DLDAbbas AbbasiNo ratings yet

- Subject: Vlsi Nano-Technology DevicesDocument5 pagesSubject: Vlsi Nano-Technology DevicesTanaya KatakkarNo ratings yet

- DLD Final Lab ReportDocument10 pagesDLD Final Lab Reporthaiqa suhail100% (1)

- Experiment 3 - CSC 204 LabDocument7 pagesExperiment 3 - CSC 204 Lab2221634No ratings yet

- Ex ADocument3 pagesEx AAniket RatnakarNo ratings yet

- Digital Electronics - Tutorial #1Document3 pagesDigital Electronics - Tutorial #1Dishawn NationNo ratings yet

- CD4511BM/BC BCD-to-7 segment decoder/driverDocument10 pagesCD4511BM/BC BCD-to-7 segment decoder/driverAVINASHNo ratings yet

- Taller Chapter 3 Sistemas DigitalesDocument4 pagesTaller Chapter 3 Sistemas DigitalesCristian PuentesNo ratings yet

- Circuitos Lógicos Combinacionales: Banda Díaz Ana KarinaDocument4 pagesCircuitos Lógicos Combinacionales: Banda Díaz Ana KarinaAnaKarinaBandaDiazNo ratings yet

- DSD ManualDocument29 pagesDSD ManualperiyasamyNo ratings yet

- CAO LAB MANUALDocument28 pagesCAO LAB MANUALabhisheksingh89208No ratings yet

- 0008-BSCS-19 MUHAMMAD JUNAID TARIQ (DLD Lab) Word FileDocument6 pages0008-BSCS-19 MUHAMMAD JUNAID TARIQ (DLD Lab) Word FileKashif KashifNo ratings yet

- CS302 - Lab Manual - Week No PDFDocument8 pagesCS302 - Lab Manual - Week No PDFattiqueNo ratings yet

- UntitledDocument7 pagesUntitledIn Fee Knee TeaNo ratings yet

- Chapter 7 - Shift RegisterDocument35 pagesChapter 7 - Shift RegisterHumna DubbiiNo ratings yet

- Encoder and Decoder Circuits Lab ReportDocument6 pagesEncoder and Decoder Circuits Lab ReportRanda Kurniawan PNo ratings yet

- UntitledDocument7 pagesUntitledIn Fee Knee TeaNo ratings yet

- Tutorial 2 - Electronics (2018)Document3 pagesTutorial 2 - Electronics (2018)Pasindu PramodNo ratings yet

- ASSIGNMENT 1 - VerilogDocument3 pagesASSIGNMENT 1 - VerilogfiitnessbynehaNo ratings yet

- Assement 04Document5 pagesAssement 04Naina PrasharNo ratings yet

- DLD Assignment#2Document3 pagesDLD Assignment#2Muhammad AliNo ratings yet

- EP01080940 - Logbook For Lab 8Document13 pagesEP01080940 - Logbook For Lab 8Pavahaariny KathegesenNo ratings yet

- Digital Design Lab ReportDocument7 pagesDigital Design Lab ReportJohn DoeNo ratings yet

- Digital Lab ReportDocument9 pagesDigital Lab ReportNg Ming FengNo ratings yet

- Computer Servicing 4: Introduction To Logic Gates Boolean AlgebraDocument13 pagesComputer Servicing 4: Introduction To Logic Gates Boolean AlgebraJhon Keneth NamiasNo ratings yet

- DLD Project Report CompleteDocument10 pagesDLD Project Report CompleteAMMAD MAHMOODNo ratings yet

- FDDGDocument3 pagesFDDGaliffpadziNo ratings yet

- EXPERIMENT # 5 - ECE 3A Cruz, JairehDale FDocument4 pagesEXPERIMENT # 5 - ECE 3A Cruz, JairehDale FJaireh Dale CruzNo ratings yet

- CpE 272 Digital Lab Report SummaryDocument9 pagesCpE 272 Digital Lab Report SummaryMayra CintoraNo ratings yet

- Data Hasil Percobaan: Tabel 6.1. Rangkaian Encoder 8 To 3Document2 pagesData Hasil Percobaan: Tabel 6.1. Rangkaian Encoder 8 To 3fardanNo ratings yet

- PCB Reprt (1) FinalDocument8 pagesPCB Reprt (1) FinalShamma SNo ratings yet

- DLD-Counters experiemntDocument6 pagesDLD-Counters experiemnt123ad0006No ratings yet

- LCD Mod3Ass TUMALIUANDocument6 pagesLCD Mod3Ass TUMALIUANmaxpein100% (1)

- Lab 3 Group 2 Haziq & AdamDocument16 pagesLab 3 Group 2 Haziq & AdamShamalen RajanNo ratings yet

- Final Solution Manual v2Document13 pagesFinal Solution Manual v2SSTGingNo ratings yet

- EXP3 ReportDocument6 pagesEXP3 Reportsedeq AlsakkfNo ratings yet

- Recent PHD ResultDocument72 pagesRecent PHD ResultSavita Kiran BNo ratings yet

- DLD Lab#08Document6 pagesDLD Lab#08Muhammad AliNo ratings yet

- Cse Part QuesDocument84 pagesCse Part QuesAurongo NasirNo ratings yet

- Channel Models For Wireless Communication SystemsDocument10 pagesChannel Models For Wireless Communication SystemsAurongo NasirNo ratings yet

- SummaryDocument42 pagesSummaryMokone Pro MokoneNo ratings yet

- Channel Models For Wireless Communication SystemsDocument10 pagesChannel Models For Wireless Communication SystemsAurongo NasirNo ratings yet

- Lecture 18 ProblemsDocument2 pagesLecture 18 ProblemsAurongo NasirNo ratings yet

- Channel Models For Wireless Communication Systems: Experiment No: 3Document27 pagesChannel Models For Wireless Communication Systems: Experiment No: 3Aurongo NasirNo ratings yet

- Applied Sciences: Path Loss Prediction Based On Machine Learning: Principle, Method, and Data ExpansionDocument18 pagesApplied Sciences: Path Loss Prediction Based On Machine Learning: Principle, Method, and Data ExpansionAurongo NasirNo ratings yet

- Theory of DLD SessionalDocument1 pageTheory of DLD SessionalAurongo NasirNo ratings yet

- Name of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabDocument7 pagesName of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabAurongo NasirNo ratings yet

- EEE 304 - AllDocument43 pagesEEE 304 - AllAurongo NasirNo ratings yet

- Experiment No.1:Introduction To Basic Gates and Logic Simplification TechniquesDocument6 pagesExperiment No.1:Introduction To Basic Gates and Logic Simplification TechniquesAurongo NasirNo ratings yet

- EEE 304 - Exp4 PDFDocument5 pagesEEE 304 - Exp4 PDFAurongo NasirNo ratings yet

- Power Control Algorithms in Wireless Communication: International Journal of Computer Applications February 2010Document9 pagesPower Control Algorithms in Wireless Communication: International Journal of Computer Applications February 2010Aurongo NasirNo ratings yet

- Evolution of The Power Control Techniques For DS-CDMA Toward 3G Wireless Communication SystemsDocument15 pagesEvolution of The Power Control Techniques For DS-CDMA Toward 3G Wireless Communication SystemsAurongo NasirNo ratings yet

- Identifier: Identifier Are The Names Used To Give For An Object (Such As Signal NameDocument6 pagesIdentifier: Identifier Are The Names Used To Give For An Object (Such As Signal NameAurongo NasirNo ratings yet

- Theory of DLD SessionalDocument1 pageTheory of DLD SessionalAurongo NasirNo ratings yet

- EEE 304 - Exp8Document7 pagesEEE 304 - Exp8Aurongo NasirNo ratings yet

- Name of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabDocument7 pagesName of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabAurongo NasirNo ratings yet

- EEE 304 Experiment No. 04 Name of The Experiment: Design of Decoder/Encoder/Multiplexer CircuitDocument5 pagesEEE 304 Experiment No. 04 Name of The Experiment: Design of Decoder/Encoder/Multiplexer CircuitAurongo NasirNo ratings yet

- Name of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabDocument7 pagesName of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabAurongo NasirNo ratings yet

- EEE 304 - Exp6Document4 pagesEEE 304 - Exp6Aurongo NasirNo ratings yet

- Experiment No.1:Introduction To Basic Gates and Logic Simplification TechniquesDocument6 pagesExperiment No.1:Introduction To Basic Gates and Logic Simplification TechniquesAurongo NasirNo ratings yet

- EEE 304 - Exp2Document7 pagesEEE 304 - Exp2Aurongo NasirNo ratings yet

- SummaryDocument42 pagesSummaryMokone Pro MokoneNo ratings yet

- BiosignalDocument27 pagesBiosignalAurongo NasirNo ratings yet

- The Ordinal Approach To Utility AnalysisDocument26 pagesThe Ordinal Approach To Utility AnalysisAurongo NasirNo ratings yet

- Design and implementation of different adder, subtractor and comparator circuitsDocument5 pagesDesign and implementation of different adder, subtractor and comparator circuitsAurongo NasirNo ratings yet

- The Ordinal Approach To Utility AnalysisDocument26 pagesThe Ordinal Approach To Utility AnalysisAurongo NasirNo ratings yet

- Voltage Fluctuations and Lamp Flicker in Power SystemsDocument12 pagesVoltage Fluctuations and Lamp Flicker in Power SystemsAurongo NasirNo ratings yet