Professional Documents

Culture Documents

Janta 050 May 2015 Elex Cgpa

Janta 050 May 2015 Elex Cgpa

Uploaded by

Hakimuddin Bohari0 ratings0% found this document useful (0 votes)

6 views4 pagesOriginal Title

janta 050 may 2015 elex cgpa

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views4 pagesJanta 050 May 2015 Elex Cgpa

Janta 050 May 2015 Elex Cgpa

Uploaded by

Hakimuddin BohariCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 4

oo

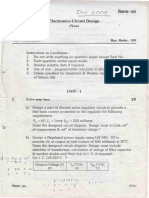

Electronic Circuit Design

(146115)

P. Pages: 4

Time : Three Hours

Instructions to Candidates

1. Do not write anything on question paper except Seat No.

2) Graph or diagram should be drawn with the black ink pen being

Used for writing paper or black HB pencil. >

. Students should note, ne supplement will be provided.

|. All questions carry equal marks.

. Assume suitable data if required.

|. Unless specified, assume material of device'as silicon (si),

- Use of programmable calculator is allowed:

Noese

UNIT -1

Answer any two. 8

iit) | #058

Draw designed cirout’glegrem. D

calculation of capacitor, diodes and transformer ratings.

Also caleulate rople factor value ofthis circuit.

») Design a dual tacking power supply using three terminal 8

Feats GRU 347 and S87 gets V4 OBA

each Vgip Tor filter capacitor is 1.2V at 40°C, drop out voltage

2. Sip to cient sharers Cestge shes coh sstarnnt

components around ICs heai sink requirement if needed and

Seeign of unregulated power supply section.

©), “Qasign @ switching regulator using 1¢ 1877/2577 tor 8

following requirements,

~/i) Input voltage to regulator Ein=8V,

ii) Output voltage from regulator Vo=12V.

‘SAP - 050 1 pro

‘SATOTaAT - 050

Ti) Numax = 0-5,

iv) M=25% of Ik max

\)_ Switcher frequency 52KHz, RON = 0.250.

VW) TA=279C, jA-85'C/w, Gjo=2° o/w. Draw designed circuit

diagram. design should include calculation of component values

and heat sink ifrequired

INo need of unregulated power supply design).

UNIT = a

2, Answer any two.

a) Design a single stage CE amplifier with partially bypassed 8

and partially unbypassed emitter resistance for Ays®50, Q

points [1mA, 5V] S=10, FI=10k82, RLy =100k2, RS=06kn,

{| =S0Hz, Use BJT having hfe = 200, hie = 10k use potential divider

bias network. Assume VRE 10% of VCC.

d) Design a single stage common gate ampitiier with self bias. 8

network for following requirements.

i) Ave =40RI< 1800, Rw = 100k, RS=500, F =20Hz

i) fy = "P82, Vos 23

ii) Vigo = Vag: whor@ Rg Is rosstance connected at source terminal

of FET, FET usod is N-channol wih Ipss =2mA, Ve=-6V,

770 = tOmt and fass= 200A.

©) Design voltage series feedback amplifier (wo-stage) 5

so as to provide

i) Af 2120

|) Use identical stages with potential divider bias network with

'S=10.and Q point (2mA, SV)

fi) Voe=10V, Ri y =

JW) “Output voltage swing Vop_p =9V Used transistors have

hfe=200, hie=2.6k2.

“erat - 050 2

UNIT = IIL

3. Answer any two.

2) Design a transformer coupled class A power amplifier for a

‘output voltage Vo =5V(ms), S=8, Voc =18V andR, = 40.

Efficiency of transformer is 90% and hfe vill be 100. Draw designed

‘circuit diagram. Design must inctude calculation of bias component,

‘Selection of transformer & transistor rating calculation Assume VRE

10% of Vic. ny

2) Design # class B transformer coupled power amplifier for 8

Pac = 10w. Ry = 42. efficiency n=80%. S=8 Voc = 18V, hie= 50.

@) Design a complementary eymmeiry power amplitie? for 8

Pac = 15w, Ry = 42, frequency response = 20Hz to 10KHz.

Design must include calculation of supply voltage, transistors

maximum ratings calculation and external capacitor.

unt =v

4. a) Design a Colpitt's oscillator circuit using FET (N-channel) for 8

i) oscillation frequency fo =5Miz_~

i) Ay =25

ii) Rin 200K 5

™) Iba =A Vong =5V and Ya =3V (Ris device source resistance)

Used FET heve, loss =2mA, rd=50K gmo=3mU, Vp =-Bv

b) Design an astable multivibrator (using BJT) to generate square a

wave of SKHz and ariplitude 10V with collector current of 2mA.

Use transistor witty hfamin = 100. Draw designed circuit along with

component rating cafculations.

¢) Design a tuned amplifier circuit using BUT as an active element for 8

Te nerabgareetorsy eee

8 irae cen «00,

iv) Input resistance Ri=10k02

v)_ “Stability factor, for bias network. 8JT have

vile =12K2, ro=180k2, nfe=100, co=2pt

‘SWFA - 050 3 PO

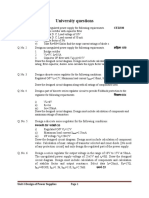

unit -v.

Answer any two.

a) Design a band pass filter for F|_ = 600Hz,TH=6KHz, with 8

_ttenuation rate of 40 dBidecade in stop band. Also tate pass band as —

flat 2s possible. Use salen key equal component approach

{Take vate of capacitor as 001i]

>) Design an AC amplifier using OPAMP 741C with single > 8

fended power supply for V

|)” Inverting mode,

i) At= 10.5,

lil) Rif = 20kQ )

\v) Voc=24V, | =2mARS=750

YW) Lower cut off frequency Fi, -20H2 741C have following

spectications

Ag = 2x109, fo=SHz, Ri=2MO, Rc =750, SR-O.5v/isec

©) Design sallen key equal component Lpt for following 8

‘specification

i) Critical frequency of SkHz.

il), Rolloft rate of 89 dB/cec ~

il) Use butterworth response. »

Wy) Gainof 10at0c =

¥) Calculate gain BW and slew rate requirements of

44C. Draw designed circuit diagram for 741C.

'¢ 0.5v/,(@6e and GBW = 1 MHz,

Filer Sectons. «Kip

Butterworth = 21.8484

Response (2) 0.765 1

‘Sima - 050 4 115140

You might also like

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Charoli 26Document7 pagesCharoli 26Hakimuddin BohariNo ratings yet

- Jaya 28Document7 pagesJaya 28Hakimuddin BohariNo ratings yet

- Ekdant 23Document5 pagesEkdant 23Hakimuddin BohariNo ratings yet

- 1090 Nov 15Document4 pages1090 Nov 15Hakimuddin BohariNo ratings yet

- All Question Paper ECDDocument63 pagesAll Question Paper ECDHakimuddin BohariNo ratings yet

- Chitrarth 24Document9 pagesChitrarth 24Hakimuddin BohariNo ratings yet

- Cel 1330Document4 pagesCel 1330Hakimuddin BohariNo ratings yet

- 185101-235101 Nov 15Document4 pages185101-235101 Nov 15Hakimuddin BohariNo ratings yet

- Unit-Iii University QuestionsDocument8 pagesUnit-Iii University QuestionsHakimuddin BohariNo ratings yet

- Unit-Ii University QuestionsDocument6 pagesUnit-Ii University QuestionsHakimuddin BohariNo ratings yet

- Unit-I University QuestionsDocument6 pagesUnit-I University QuestionsHakimuddin BohariNo ratings yet