Professional Documents

Culture Documents

Infineon TLE4299V33 DS v01 - 01 en

Uploaded by

Stelian DobreOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Infineon TLE4299V33 DS v01 - 01 en

Uploaded by

Stelian DobreCopyright:

Available Formats

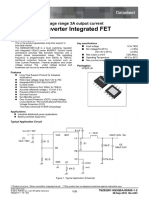

Low-Drop Fixed Voltage Regulator TLE 4299

Features

• Output voltage 3.3V ± 2%

• 150 mA Output current

• Extreme low current consumption in ON state

• Inhibit function: Below 1 µA current consumption

in off mode

• Early warning P-DSO-8-3

• Reset output low down to VQ = 1 V

• Overtemperature protection

• Reverse polarity proof

• Wide temperature range

• Green Product (RoHS compliant)

• AEC Qualified

Functional Description

The TLE 4299 is a monolithic voltage regulator with fixed P-DSO-14-3, -8, -9, -11

5-V (see data sheet TLE4299G/GM) or 3.3 V output,

supplying loads up to 150 mA. It is especially designed

for applications that may not be powered down while the

motor is off. In addition the TLE 4299GMV includes an inhibit function. When the inhibit

signal is removed, the device is switched off and the quiescent current is less than 1 µA.

To achieve proper operation of the µ-controller, the device supplies a reset signal. The

reset delay time is selected application-specific by an external delay capacitor. The reset

threshold is adjustable. An early warning signal supervises the voltage at pin SI. The

TLE 4299 is pin-compatible to the TLE 4269 and functional similar with the additional

inhibit function. The TLE 4299 is designed to supply microcontroller systems even under

automotive environment conditions. Therefore it is protected against overload, short

circuit and over temperature.

Type Package

TLE 4299 GV33 PG-DSO-8-16

TLE 4299 GMV33 PG-DSO-14-30

Datasheet 1 Rev. 1.1, 2007-10-17

TLE 4299

Circuit Description

The TLE 4299 is a PNP based very low drop linear voltage regulator. It regulates the

output voltage to VQ = 3.3 V for an input voltage range of 4.4 V ≤ VI ≤ 45 V. The control

circuit protects the device against potential damages caused by overcurrent and

overtemperature.

The internal control circuit achieves a 3.3 V output voltage with a tolerance of ± 2%.

The device includes a power on reset and an under voltage reset function with adjustable

reset delay time and adjustable reset switching threshold as well as a sense control/early

warning function. The device includes an inhibit function to disable it when the ECU is

not used for example while the motor is off.

The reset logic compares the output voltage VQ to an internal threshold. If the output

voltage drops below this level, the external reset delay capacitor CD is discharged. When

VD is lower than VST, the reset output RO is switched Low. If the output voltage drop is

very short, the VST level is not reached and no reset-signal is asserted. This feature

avoids resets at short negative spikes at the output voltage e.g. caused by load changes.

As soon as the output voltage is more positive than the reset threshold, the delay

capacitor is charged with constant current. When the voltage reaches VDT the reset

output RO is set High again.

The reset delay time and the reset reaction time are defined by the external capacitor

CD. The reset function is active down to VI = 1 V.

In addition to the normal reset function, the device gives an early warning. When the SI

voltage drops below VSI,low, the devices asserts the SI output Low to indicate the logic

and the µ-processor that this voltage has dropped. The sense function uses a hysteresis:

When the SI-voltage reaches the VSI,high level, SO is set high again. This feature can be

used as early warning function to notice the µ-controller about a battery voltage drop and

a possible reset in a short time. Of course also any other voltage can be observed by this

feature.

The user defines the threshold by the resistor-values RSI1 and RSI2.

For the exact timing and calculation of the reset and sense timing and thresholds, please

refer to the application section.

Datasheet 2 Rev. 1.1, 2007-10-17

TLE 4299

TLE 4299

I Q

Band- Current

Gap- and RSO

Reference Saturation

Control

RRO

SO

SI

Reference RO

Reset

Control

RADJ

D GND

AEB03103

Figure 1 Block Diagram TLE 4299 GV33

Datasheet 3 Rev. 1.1, 2007-10-17

TLE 4299

TLE 4299

I Q

Band- Current

Gap- and RSO

Reference Saturation

Control

Inhibit RRO

INH Control

SO

SI

Reference RO

Reset

Control

RADJ

D GND

AEB03104

Figure 2 Block Diagram TLE 4299 GMV33

Datasheet 4 Rev. 1.1, 2007-10-17

TLE 4299

PG-DSO-8-16

I 1 8 Q

SI 2 7 SO

RADJ 3 6 RO

D 4 5 GND

AEP02832

Figure 3 Pin Configuration (top view)

Pin Definitions and Functions (TLE 4299 GV33)

Pin No. Symbol Function

1 I Input; block directly to GND on the IC with a ceramic capacitor.

2 SI Sense Input; if not needed connect to Q.

3 RADJ Reset Threshold Adjust; if not needed connect to GND.

4 D Reset Delay; to select delay time, connect to GND via external

capacitor.

5 GND Ground

6 RO Reset Output; the open-collector output is linked internally to Q

via a 20kΩ pull-up resistor. Keep open, if the pin is not needed.

7 SO Sense Output; open-collector output. Keep open, if the pin is not

needed.

8 Q Output; connect to GND with a 22 µF capacitor, 0.4 Ω <

ESR < 3.7 Ω.1)

1)

see characteristic curves

Datasheet 5 Rev. 1.1, 2007-10-17

TLE 4299

PG-DSO-14-30

RADJ 1 14 SI

D 2 13 I

GND 3 12 GND

GND 4 11 GND

GND 5 10 GND

INH 6 9 Q

RO 7 8 SO

AEP02831

Figure 4 Pin Configuration (top view)

Pin Definitions and Functions (TLE 4299 GMV33)

Pin No. Symbol Function

1 RADJ Reset Threshold Adjust; if not needed connect to GND.

2 D Reset Delay; connect to GND via external delay capacitor for

setting delay time.

3, 4, 5 GND Ground

6 INH Inhibit: If not needed connect to Input pin I; A high signal

switches the regulator ON.

7 RO Reset Output; the open-collector output is linked internally to Q

via a 20kΩ pull-up resistor. Keep open, if the pin is not needed.

8 SO Sense Output; open-collector output. Keep open, if the pin is not

needed.

9 Q Output; connect to GND with a 22 µF capacitor, 0.4 Ω <

ESR < 3.7 Ω.1)

10, 11, 12 GND Ground

13 I Input; block to GND directly at the IC by a ceramic capacitor.

14 SI Sense Input; if not needed connect to Q.

1)

see characteristic curves

Datasheet 6 Rev. 1.1, 2007-10-17

TLE 4299

Absolute Maximum Ratings

Tj = – 40 to 150 °C

Parameter Symbol Limit Values Unit Notes

min. max.

Input I

Input voltage VI – 40 45 V –

Inhibit Input INH

Input voltage VINH – 40 45 V –

Sense Input SI

Input voltage VSI – 0.3 45 V –

Input current ISI -1 1 mA –

Reset Threshold Adjust RADJ

Input voltage VRADJ – 0.3 7 V –

Input current IRADJ -10 10 mA –

Reset Delay D

Voltage VD – 0.3 7 V –

Reset Output RO

Voltage VR – 0.3 7 V –

Sense Output SO

Voltage VSO – 0.3 7 V –

Output Q

Output voltage VQ – 0.3 7 V –

Output current IQ –5 – mA –

Datasheet 7 Rev. 1.1, 2007-10-17

TLE 4299

Absolute Maximum Ratings (cont’d)

Tj = – 40 to 150 °C

Parameter Symbol Limit Values Unit Notes

min. max.

Temperature

Junction temperature Tj – 150 °C –

Storage temperature TStg – 50 150 °C –

Operating Range

Input voltage VI 4.4 45 V –

Junction temperature Tj – 40 150 °C –

Thermal Data

Junction-ambient for foot Rthja – 200 K/W PG-DSO-8-16

print only1) 130 K/W PG-DSO-14-30

Junction-ambient for Rthja – 164 K/W PG-DSO-8-16

300mm2 cooling area2) 70 K/W PG-DSO-14-30

Junction-pin Rthjp – 60 K/W PG-DSO-8-163)

30 K/W PG-DSO-14-30

4)

1)

FR4, 80x80x1,5mm; 35µ Cu, 5µ Sn; Footprint only

2)

FR4, 80x80x1,5mm; 35µ Cu, 5µ Sn; 300mm2

3)

Measured to pin 5

4)

Measured to pin 4

Note: Stresses above those listed here may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect

device reliability.

In the operating range, the functions given in the circuit description are fulfilled.

Datasheet 8 Rev. 1.1, 2007-10-17

TLE 4299

Characteristics

VI = 13.5 V; Tj = – 40 °C < Tj < 150 °C

Parameter Symbol Limit Values Unit Measuring Condition

min. typ. max.

Output voltage VQ 3.23 3.30 3.37 V 1 mA ≤ IQ ≤ 100 mA;

5.5 V ≤ VI ≤ 16 V

Output voltage VQ 3.20 3.30 3.40 V IQ ≤ 150 mA;

5.5 V ≤ VI ≤ 16 V

Current limit IQ 250 400 500 mA –

Current consumption; Iq – 65 105 µA Inhibit ON;

Iq = II – IQ IQ ≤ 1 mA, Tj < 85 °C

Current consumption; Iq – 170 500 µA Inhibit ON;

Iq = II – IQ IQ = 10 mA

Current consumption; Iq – 0.7 2 mA Inhibit ON;

Iq = II – IQ IQ = 50 mA

Current consumption; Iq – – 1 µA VINH = 0 V;

Iq = II – IQ Tj = 25 °C

Load regulation ∆VQ – 5 30 mV IQ = 1 mA to 100 mA

Line regulation ∆VQ – 10 25 mV VI = 6 V to 28 V;

IQ = 1 mA

Power Supply Ripple PSRR – 66 – dB fr = 100 Hz; Vr = 1 VSS;

rejection IQ = 100 mA

Inhibit (TLE 4299 GMV33 only)

Inhibit OFF voltage range VINH OFF – – 0.8 V VQ off

Inhibit ON voltage range VINH ON 3.5 - V VQ on

High input current IINH ON – 3 5 µA VINH = 5V

Low input current IINH OFF – 0.5 2 µA VINH = 0.8 V

Datasheet 9 Rev. 1.1, 2007-10-17

TLE 4299

Characteristics (cont’d)

VI = 13.5 V; Tj = – 40 °C < Tj < 150 °C

Parameter Symbol Limit Values Unit Measuring Condition

min. typ. max.

Reset Generator

Switching threshold Vrt 3.00 3.10 3.20 V –

Reset threshold VRTHEAD 50 200 300 mV –

headroom

Reset pull up RRO 10 20 40 kΩ –

Reset low voltage VR – 0.17 0.40 V VQ < 3.0 V; internal RRO;

IR = 1 mA

External reset pull up VR ext 5.6 – – kΩ Pull up resistor Q

Delay switching threshold VDT 1.6 1.85 2.35 V –

Switching threshold VST 0.35 0.50 0.60 V –

Reset delay low voltage VD – – 0.1 V VQ < VRT

Charge current Ich 2.0 3.5 6.0 µA VD = 1 V

Power-up Reset delay td 36 51 60 ms CD = 100 nF

time

Reset reaction time trr 0.5 1.2 3.0 µs CD = 100 nF

Reset Adjust Switching VRADJ 1.26 1.36 1.44 V VQ < 3.5V

Threshold TH

Input Voltage Sense

Sense threshold high VSI high 1.34 1.45 1.54 V –

Sense threshold low VSI low 1.26 1.36 1.44 V –

Sense input switching VSI HYST 50 90 130 mV VSI HYST = VSI high – VSI low

hysteresis

Sense output low voltage VSO low – 0.1 0.4 V VSI < 1.20 V; Vi > 4.2 V;

ISO = 1mA

External SO pull up RSO ext 5.6 – – kΩ –

resistor

Sense input current ISI –1 0.1 1 µA Si > 1.0V

Datasheet 10 Rev. 1.1, 2007-10-17

TLE 4299

Characteristics (cont’d)

VI = 13.5 V; Tj = – 40 °C < Tj < 150 °C

Parameter Symbol Limit Values Unit Measuring Condition

min. typ. max.

Sense high reaction time tpd SO LH – 2.4 4.0 µs RSO ext = 5.6kΩ

Sense low reaction time tpd SO HL – 2.5 6.0 µs RSO ext = 5.6kΩ

Note: The listed characteristics are ensured over the operating range of the integrated

circuit. Typical characteristics specify mean values expected over the production

spread. If not otherwise specified, typical characteristics apply at TA = 25 °C and

the given supply voltage.

II IQ1

VI I Q1 VQ1

TLE 4299

IINH

VINH INH

(TLE4299GMV33

only) D RO VRO

CD

Ich

100 nF

IRADJ

VRADJ RADJ

ISI

VSI SI SO VSO

GND

IGND

AES02835

Figure 5 Measurement Circuit

Datasheet 11 Rev. 1.1, 2007-10-17

TLE 4299

Application Information

TLE 4299 CQ1 P

VBAT CI2 C

I Q 22 F Q2

CI1

Band- Current

Gap- and RSO

Reference Saturation

Control

RRO

RSI1 SO

SI

RO

RSI2 Reference

Reset

Control

RADJ1

RADJ

GND D

RADJ2

CD

AES03105

Figure 6 Application Diagram TLE 4299 GV33

Datasheet 12 Rev. 1.1, 2007-10-17

TLE 4299

TLE 4299 CQ1 P

VBAT CI2 C

I Q 22 F Q2

CI1

Band- Current

Gap- and RSO

Reference Saturation

Control

From

KI. 15 INH Inhibit RRO

Logic

RSI1 SO

SI

RO

RSI2 Reference

Reset

Control

RADJ1

RADJ

GND D

RADJ2

CD

AES03106

Figure 7 Application Diagram with Inhibit Function TLE4299 GMV33

The TLE 4299 supplies a regulated 3.3 V output voltage with an accuracy of 2% for an

input voltage between 4.4 V and 45 V in the temperature range of Tj = – 40 to 150 °C, in

an output current range of 1 mA to 100 mA.

The device is capable to supply 150 mA with an accuracy of 3%. For protection at high

input voltage above 25 V, the output current is reduced (SOA protection).

An input capacitor is necessary for compensating line influences and to limit steep input

edges. A resistor of approx. 1 Ω in series with CI, can damp the LC of the input inductivity

and the input capacitor.

The voltage regulator requires for stability an output capacitor CQ of at least 22 µF with

an 0.4Ω < ESR < 3.7Ω for the whole load- and temperature range. For more detailed

information, refer to the characteristical curves.

Datasheet 13 Rev. 1.1, 2007-10-17

TLE 4299

Reset

The power on reset feature is necessary for a defined start of the microprocessor when

switching on the application. For the reset delay time after the output voltage of the

regulator is above the reset threshold, the reset signal is set High again. The reset delay

time is defined by the reset delay capacitor CD at pin D.

The under-voltage reset circuitry supervises the output voltage. In case VQ decreases

below the reset threshold the reset output is set LOW after the reset reaction time. The

reset LOW signal is generated down to an output voltage VQ to 1 V. Both the reset

reaction time and the reset delay time is defined by the capacitor value.

The power on reset delay time is defined by the charging time of an external delay

capacitor CD.

CD = (td × ID) / ∆V [1]

td = CD x ∆V / ID [2]

With CD reset delay capacitor

td reset delay time

∆V = VDT, typical 1.8 V for power up reset

Ich charge current typical 3.5 µA

For a delay capacitor CD =100 nF the typical power on reset delay time is 51 ms.

The reset reaction time tRR is the time it takes the voltage regulator to set reset output

LOW after the output voltage has dropped below the reset threshold. It is typically 1.2 µs

for delay capacitor of 100 nF. For other values for CD the reaction time can be estimated

using the following equation:

tRR ∼ 10 ns / nF × CD [3]

Datasheet 14 Rev. 1.1, 2007-10-17

TLE 4299

VI

t

VQ < t RR

V RT

t

dV I D

VD =

dt C D

V DT

V ST

t RR t

td

V RO

VRO, SAT

t

Power-on-Reset Thermal Voltage Dip Undervoltage Secondary Overload

Shutdown at Input Spike at Output AED03107

Figure 8 Reset Timing Diagram

The reset output is an open collector output. An external pull-up can be added with a

resistor value of at least 5.6 kΩ.

In addition the reset switching threshold can be adjusted by an external voltage divider.

The feature is useful for microprocessors which guarantee safe operation down to volt-

ages below the internally set reset threshold of 3.10V typical. If the internal used reset

threshold of typical 3.10V is used, the pin RADJ has to beconnected to GND.

If a lower reset threshold is required by the system, a voltage divider defines the reset

threshold VRth between 2.5V and 3.10V as long as the Input Voltage VI>4.4V

VRth = VRADJ TH * (RADJ1 + RADJ2) / RADJ2 (3)

VRADJ TH is typical 1.36 V.

Datasheet 15 Rev. 1.1, 2007-10-17

TLE 4299

Early Warning

The early warning function compares a voltage defined by the user to an internal

reference voltage. Therefore the supervised voltage has to be scaled down by an

external voltage divider in order to compare it to the internal sense threshold of typical

1.36 V. The sense output pin is set low, when the voltage at SI falls below this threshold.

A typical example where the circuit can be used is to supervise the input voltage VI to

give the microcontroller a prewarning of low battery condition.

Calculation to the voltage divider can be easily done since the sense input current can

be neglected.

Sense

Input

Voltage

VSI, High

VSI, Low

Sense

t PD SO LH t PD SO HL

Output

High

Low

t

Figure 9 Sense Timing Diagram

VthHL = (RSI1 + RSI2)/RSI2 × VSI low [4]

VthLH = (RSI1 + RSI2)/RSI2 × VSI high [5]

The sense in comparator uses a hysteresis of typical 90 mV. This hysteresis of the

supervised threshold is multiplied by the resistor dividers amplification (RSI1 + RSI2)/RSI1.

The sense in comparator can also be used for receiving data with a threshold of typical

1.36 V and a hysteresis of 90 mV. Of course also the data signal can be scaled down

with a resistive divider as shown above. With a typical delay time of 2.5 µs for positive

transitions and 2.4 µs for negative transitions receiving data of up to 100 kBaud are

possible. The sense output is an open collector output.

Datasheet 16 Rev. 1.1, 2007-10-17

TLE 4299

Current Consumption Iq versus Current Consumption Iq versus Output

Junction Temperature Tj Current IQ

2_IQ-IQ.VSD

1_Iq-Tj.vsd 12

Iq [µA] Iq [mA]

VI = 13.5V

100

Tj = 150 °C

8

IQ = 1mA

6 Tj = 25 °C

10

4 Tj = -40 °C

1

2

0.01

-40 -20 0 20 40 60 80 100 120 140 0 40 80 120 160

IQ [mA]

Tj [°C]

Current Consumption Iq versus Input Output Voltage VQ versus Junction

Voltage VI Temperature Tj

3_IQ-VI.VSD

AED01671

3 3.5

T = 25°C

Iq [mA] VQ V

3.4

V Ι = 13.5 V

2 3.3

1.5 3.2

1 3.1

0.5 3.0

IQ = 10mA

IQ = 1mA

2.9

0 10 20 30 40 -40 0 40 80 120 C 160

VI [V] Tj

Datasheet 17 Rev. 1.1, 2007-10-17

TLE 4299

Maximum Output Current IQ versus Reverse Output Current IQ versus

Junction Temperature Tj Output Voltage VQ

8_IQMAX-TJ.VSD 10_IQ-VQ.vsd

550 10

IQ [mA] VI = 0 V

IQ [mA]

-20 Tj = -40 °C

450 VI = 13.5 V Tj = 25 °C

-40 Tj = 150 °C

400

-60

350

-80

300

-100

250

-40 -20 0 20 40 60 80 100 120 140 0 10 20 30 40

Tj [°C] VQ [V]

Output Voltage VQ at Input Voltage

Maximum Output Current IQ versus Extremes

Input Voltage VI

AED01808

AED03110

6

350 VQ [V]

Ι Q mA

300

250 4

Tj = 25 C

200

3

RL = 50 Ω

150

Tj = 125 C 2

100

1

50

0

0 0 1 2 3 4 V 5

0 10 20 30 40 V 50

VΙ

VΙ

Datasheet 18 Rev. 1.1, 2007-10-17

TLE 4299

Power Supply Ripple Rejection PSRR

Region of Stability versus Frequency f

12_ESR- 13_PSRR.VSD

100 IQ_150.VSD 90

CQ = 22µF PSRR

ESRCQ

[Ω]

Tj = 150 °C [dB]

10 VI=6V IQ = 0.1 mA

VI=25V

70

IQ = 1 mA

1 Stable 60

Region

VI=25V

IQ = 10 mA

VI=6V 50

0.1 VRIPPLE = 0.5 V

VIN = 13.5 V IQ = 100 mA

40

CQ = 22 µF Tantalum

Tj = 25 °C

0.01

0 40 80 120 160 10 100 1k 10k 100k

IQ [mA] f [Hz]

Load Transient Response Peak Voltage

Region of Stability DVQ

12_ESR-IQ_-

100 40.VSD

CQ = 22µF

ESRCQ 20_Load Trancient vs time 125.vsd

[Ω]

Tj = -40 °C

IQ1:100mA Tj=125°C

Vi=13.5V

10 VI=6V

VI=25V

1 Stable

Region

VI=25V VQ

VI=6V

0.1

0.01 T=1µs/DIV VQ=100mV/DIV

0 40 80 120 160

IQ [mA]

Datasheet 19 Rev. 1.1, 2007-10-17

TLE 4299

Line Transient Response Peak Voltage Inhibit Input Current at Input Voltage

DVQ Extremes (INH=OFF)

25_IINH vs VIN INH_off.vsd

IINH

21_Line Trancient vs time 125.vsd

[µA] INH = OFF

Tj=125°C 50

dVI 2V

Vi=13.5V

40

30

Tj = -40...150°C

VQ

20

10

T=500µs/DIV VQ=50mV/DIV

10 20 30 40

VIN [V]

Inhibut Input Current IINH at Inhibit Input Reset Trigger Threshold VRT versus

Voltage Extremes Junction Temperature Tj

24_IINH vs VINH.vsd 26_VRT VS TEMP.VSD

3.25

IINH VRT VI = 13.5 V

[µA] [V]

50

40 3.15

Tj = 150°C

30 3.10 Reset Trigger

Threshold

20 Tj = 25°C 3.05

Tj = -40°C

10 3.0

10 20 30 40 -40 -20 0 20 40 60 80 100 120 140

VINH [V] Tj [°C]

Datasheet 20 Rev. 1.1, 2007-10-17

TLE 4299

Reset Delay Time TRD versus Junction Sense Threshold High versus Junction

Temperature Tj Temperature Tj

27_RESETDELAY VS 34_VSI_HI VS TEMP.VSD

60 TEMP.VSD 1.60

TRD VI = 13.5 V VSI_Hi VI = 13.5 V

[ms] [V]

50 1.50

CD = 100nF

45 1.45

40 1.40

35 1.35

-40 -20 0 20 40 60 80 100 120 140 -40 -20 0 20 40 60 80 100 120 140

Tj [°C] Tj [°C]

Delay Capacitor Charge Current versus Sense Threshold Low versus Junction

Junction Temperature Tj Temperature Tj

27A_ID-TEMP.VSD 35_VSI_LO VS TEMP.VSD

6 1.50

ICH VI = 13.5 V VSI_Lo VI = 13.5 V

[µA] [V]

4 1.40

3 1.35

2 1.30

1 1.25

-40 -20 0 20 40 60 80 100 120 140 -40 -20 0 20 40 60 80 100 120 140

Tj [°C] Tj [°C]

Datasheet 21 Rev. 1.1, 2007-10-17

TLE 4299

Package Outlines

PG-DSO-8-16 (SMD)

(Plastic Dual Small Outline)

0.35 x 45˚

4 -0.21)

1.75 MAX.

0.175 ±0.07

0.19 +0.06

(1.45)

8 MAX.

1.27 B

0.1 0.64 ±0.25

0.41+0.1

-0.06

2)

6 ±0.2

0.2 M A B 8x 0.2 M C 8x

8 5

1 4

A

5 -0.2 1)

Index Marking

1) Does not include plastic or metal protrusion of 0.15 max. per side

2) Lead width can be 0.61 max. in dambar area

GPS01181

Green Product (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products

and to be compliant with government regulations the device is available as a green

product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable

for Pb-free soldering according to IPC/JEDEC J-STD-020).

SMD = Surface Mounted Device Dimensions in mm

Datasheet 22 Rev. 1.1, 2007-10-17

TLE 4299

PG-DSO-14-30 (SMD)

(Plastic Dual Small Outline)

0.35 x 45˚

1.75 MAX.

0.175 ±0.07

C

0.19 +0.06

1)

(1.47)

8˚MAX.

4 -0.2

1.27 B

0.1 0.64 ±0.25

2)

0.41+0.10

-0.06 6±0.2

0.2 M A B 14x

14 8 0.2 M C

1 7

1)

8.75 -0.2

A

Index Marking

1) Does not include plastic or metal protrusion of 0.15 max. per side

2) Lead width can be 0.61 max. in dambar area GPS01230

Green Product (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products

and to be compliant with government regulations the device is available as a green

product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable

for Pb-free soldering according to IPC/JEDEC J-STD-020).

SMD = Surface Mounted Device Dimensions in mm

Datasheet 23 Rev. 1.1, 2007-10-17

TLE 4299

Revision History

Version Date Changes

Rev. 1.1 2007-10-17 Initial version of RoHS-compliant derivate of TLE 4299

Page 1: AEC certified statement added

Page 1 and Page 22f: RoHS compliance statement and

Green product feature added

Page 1 and Page 22f: Package drawing changed to RoHS

compliant version

Legal Disclaimer updated

Datasheet 24 Rev. 1.1, 2007-10-17

Edition 2007-10-17

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2007 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest

Infineon Technologies Office (www.infineon.com).

Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in

question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

You might also like

- Architectural ConcreteDocument24 pagesArchitectural ConcreteSaud PathiranaNo ratings yet

- Regulador 4271-2g PLD MercedesDocument23 pagesRegulador 4271-2g PLD MercedesDiego CaceresNo ratings yet

- 4271 2GDocument24 pages4271 2GAlexandre Dantas HenriqueNo ratings yet

- Tle 4471Document26 pagesTle 4471Armando UsedaNo ratings yet

- TLE4471 InfineonTechnologiesAGDocument24 pagesTLE4471 InfineonTechnologiesAGjose luisNo ratings yet

- Data SheetDocument19 pagesData SheetDiego CaceresNo ratings yet

- A2C33648Document27 pagesA2C33648mohhizbar100% (1)

- Automotive Power: Low Dropout Linear Voltage RegulatorDocument20 pagesAutomotive Power: Low Dropout Linear Voltage RegulatorJoshua WardNo ratings yet

- Infineon TLE4275V50 DS v01 - 07 en PDFDocument17 pagesInfineon TLE4275V50 DS v01 - 07 en PDFjoseNo ratings yet

- Low Drop Voltage Regulator TLE 4274: FeaturesDocument16 pagesLow Drop Voltage Regulator TLE 4274: FeaturesAdrian MonzonNo ratings yet

- 5-V Low-Drop Fixed Voltage Regulator TLE 4271-2: FeaturesDocument20 pages5-V Low-Drop Fixed Voltage Regulator TLE 4271-2: FeaturesHla Swe Oo0% (1)

- Dual Low Drop Voltage Regulator TLE 7469: FeaturesDocument22 pagesDual Low Drop Voltage Regulator TLE 7469: FeaturesPabloLabruneNo ratings yet

- Dual Low Drop Voltage Regulator TLE 7469: FeaturesDocument21 pagesDual Low Drop Voltage Regulator TLE 7469: FeaturesTahar BenacherineNo ratings yet

- Low Drop Voltage Regulator TLE 4274: FeaturesDocument16 pagesLow Drop Voltage Regulator TLE 4274: FeaturesRuddy RalNo ratings yet

- DSA00323215Document38 pagesDSA00323215Mariano AmorNo ratings yet

- TLE4279 SiemensSemiconductorGroupDocument19 pagesTLE4279 SiemensSemiconductorGroupLuis MezaNo ratings yet

- 5-V Low-Drop Fixed Voltage Regulator TLE 4271: FeaturesDocument20 pages5-V Low-Drop Fixed Voltage Regulator TLE 4271: FeaturesPablo CervantesNo ratings yet

- Low Dropout Linear Fixed Voltage RegulatorDocument26 pagesLow Dropout Linear Fixed Voltage RegulatorNur Aishi Putri SyarilNo ratings yet

- Infineon TLE4275V33 DS v01 - 20 EN 1079989Document13 pagesInfineon TLE4275V33 DS v01 - 20 EN 1079989FrankCubidesNo ratings yet

- Mitsubishi MR-J2-D-S24: General-Purpose AC ServoDocument28 pagesMitsubishi MR-J2-D-S24: General-Purpose AC ServoBrendisNo ratings yet

- 5-V Low-Drop Voltage Regulator TLE 4263: FeaturesDocument17 pages5-V Low-Drop Voltage Regulator TLE 4263: FeaturesWelleyNo ratings yet

- LD1117 Series: Low Drop Fixed and Adjustable Positive Voltage RegulatorsDocument27 pagesLD1117 Series: Low Drop Fixed and Adjustable Positive Voltage RegulatorsDavid EstebanNo ratings yet

- RP108J Series: Low Input Voltage 3A LDO Regulator OutlineDocument29 pagesRP108J Series: Low Input Voltage 3A LDO Regulator OutlineArie DinataNo ratings yet

- Bd9g341aefj LBDocument30 pagesBd9g341aefj LBFantazsta White Trash.No ratings yet

- Infineon TLE4276 DataSheet v02 - 90 ENDocument15 pagesInfineon TLE4276 DataSheet v02 - 90 ENAdrian GarciaNo ratings yet

- TLE4260Document15 pagesTLE4260NoelNo ratings yet

- 4260 2s PDFDocument15 pages4260 2s PDFmarce822No ratings yet

- HTC Korea TAEJIN Tech LM1117GS 5 0 - C465002Document12 pagesHTC Korea TAEJIN Tech LM1117GS 5 0 - C465002allradNo ratings yet

- Tle 4260Document15 pagesTle 4260Didier DoradoNo ratings yet

- LP3872/LP3875 1.5A Fast Ultra Low Dropout Linear Regulators: General Description FeaturesDocument18 pagesLP3872/LP3875 1.5A Fast Ultra Low Dropout Linear Regulators: General Description FeaturescurzNo ratings yet

- Uc3863 Utc U863 PDFDocument9 pagesUc3863 Utc U863 PDFShailesh VajaNo ratings yet

- Ics For Consumer ElectronicsDocument29 pagesIcs For Consumer ElectronicsEduardo SierraNo ratings yet

- 3 A Low Drop Positive Voltage Regulator: Adjustable and FixedDocument27 pages3 A Low Drop Positive Voltage Regulator: Adjustable and FixedTT DVNo ratings yet

- Voltage Regulator TLE 4274 / 3.3V 2.5V: FeaturesDocument12 pagesVoltage Regulator TLE 4274 / 3.3V 2.5V: Featurespglez93No ratings yet

- LP3871/LP3874 0.8A Fast Ultra Low Dropout Linear Regulators: General Description FeaturesDocument18 pagesLP3871/LP3874 0.8A Fast Ultra Low Dropout Linear Regulators: General Description FeaturesPaulo Henrique ValérioNo ratings yet

- Surge Stopping and Reverse Voltage Protection With The LM5069 PDFDocument7 pagesSurge Stopping and Reverse Voltage Protection With The LM5069 PDFĐỗ Văn ThủyNo ratings yet

- FSDM0565R (DM0565R) & Bit3105 Flf1742-20a Ip-Board PDFDocument6 pagesFSDM0565R (DM0565R) & Bit3105 Flf1742-20a Ip-Board PDFHomer Sadych Henao Marin0% (1)

- Data SheetDocument16 pagesData Sheetcarrei JohnNo ratings yet

- FP6321A FitiDocument14 pagesFP6321A FitiJob GarciaNo ratings yet

- 7N60 7N65 Data SheetDocument7 pages7N60 7N65 Data Sheetsunder punjabiNo ratings yet

- Flexible Step-Down Switching Regulators With Built-In Power MOSFETDocument26 pagesFlexible Step-Down Switching Regulators With Built-In Power MOSFETNgân Hàng Ngô Mạnh TiếnNo ratings yet

- 5 V/10 V Low Drop Voltage Regulator TLE 4266: FeaturesDocument14 pages5 V/10 V Low Drop Voltage Regulator TLE 4266: FeaturesLuis Mariano TovillasNo ratings yet

- Dual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocument21 pagesDual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesДмитрий НичипоровичNo ratings yet

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocument21 pagesRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85No ratings yet

- DS8816ADocument21 pagesDS8816AAgustin AyalaNo ratings yet

- DatasheetDocument12 pagesDatasheetWAN MOZESNo ratings yet

- FAN4822Document10 pagesFAN482240818248No ratings yet

- AN SY8063 SilergyDocument13 pagesAN SY8063 Silergyzigmund zigmundNo ratings yet

- LD1086 Series: 1.5A Low Drop Positive Voltage Regulator Adjustable and FixedDocument21 pagesLD1086 Series: 1.5A Low Drop Positive Voltage Regulator Adjustable and FixedNafise AshrafiNo ratings yet

- TLE7209 R InfineonDocument16 pagesTLE7209 R Infineonmobil benerNo ratings yet

- LED DRIVER - DP830xDocument10 pagesLED DRIVER - DP830xHenryNo ratings yet

- 2nd Lab Edc PrintDocument7 pages2nd Lab Edc PrintdHIRAJ thPNo ratings yet

- TrasDocument11 pagesTrasAmauri RogérioNo ratings yet

- DS 2857FG 02 PDFDocument12 pagesDS 2857FG 02 PDFJohan GuanchezNo ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- 2A, 2Mhz, Synchronous Step-Down Regulator: General Description FeaturesDocument15 pages2A, 2Mhz, Synchronous Step-Down Regulator: General Description FeaturesPedrolaura BethencourtNo ratings yet

- LD7577 DS 01 PDFDocument18 pagesLD7577 DS 01 PDFLucilia Dos Santos100% (2)

- Regulador de Tension TLE4267-DS-v02 - 51-EnDocument23 pagesRegulador de Tension TLE4267-DS-v02 - 51-EnJorge Martinez PerezNo ratings yet

- Voltage Regulator TLE 4274 / 3.3V 2.5V: FeaturesDocument13 pagesVoltage Regulator TLE 4274 / 3.3V 2.5V: FeaturesdavidNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Mozal Finance EXCEL Group 15dec2013Document15 pagesMozal Finance EXCEL Group 15dec2013Abhijit TailangNo ratings yet

- Walking in Space - Lyrics and Chord PatternDocument2 pagesWalking in Space - Lyrics and Chord Patternjohn smithNo ratings yet

- Experiment - 1: Batch (Differential) Distillation: 1. ObjectiveDocument30 pagesExperiment - 1: Batch (Differential) Distillation: 1. ObjectiveNaren ParasharNo ratings yet

- I I I I: Peroxid.Q!Document2 pagesI I I I: Peroxid.Q!Diego PradelNo ratings yet

- EVOM ManualDocument2 pagesEVOM ManualHouston WhiteNo ratings yet

- List of Iconic CPG Projects in SingaporeDocument2 pagesList of Iconic CPG Projects in SingaporeKS LeeNo ratings yet

- 1 Bacterial DeseaseDocument108 pages1 Bacterial DeseasechachaNo ratings yet

- Toh MFS8B 98B 003-11114-3AG1 PDFDocument92 pagesToh MFS8B 98B 003-11114-3AG1 PDFDmitry NemtsoffNo ratings yet

- Final Selection Criteria Tunnel Cons TraDocument32 pagesFinal Selection Criteria Tunnel Cons TraMd Mobshshir NayeemNo ratings yet

- Data Asimilasi Untuk PemulaDocument24 pagesData Asimilasi Untuk PemulaSii Olog-olog PlonkNo ratings yet

- Satish Gujral - FinalDocument23 pagesSatish Gujral - Finalsatya madhuNo ratings yet

- 1Document3 pages1Stook01701No ratings yet

- Eurocode 3: Design of Steel Structures "ReadyDocument26 pagesEurocode 3: Design of Steel Structures "Readywazydotnet80% (10)

- SreenuDocument2 pagesSreenuSubbareddy NvNo ratings yet

- BJAS - Volume 5 - Issue Issue 1 Part (2) - Pages 275-281Document7 pagesBJAS - Volume 5 - Issue Issue 1 Part (2) - Pages 275-281Vengky UtamiNo ratings yet

- Understanding and Teaching Fractions: Sybilla BeckmannDocument26 pagesUnderstanding and Teaching Fractions: Sybilla Beckmannjhicks_mathNo ratings yet

- Civ Beyond Earth HotkeysDocument1 pageCiv Beyond Earth HotkeysExirtisNo ratings yet

- Morfologi Dan Citra Kota Kawasan Kauman, Kecamatan Juwana, Kabupaten Pati The Morphology and Image of Kauman Town, Juwana Sub District, Pati RegencyDocument16 pagesMorfologi Dan Citra Kota Kawasan Kauman, Kecamatan Juwana, Kabupaten Pati The Morphology and Image of Kauman Town, Juwana Sub District, Pati RegencyRABIAH ARDIANTI TUM TOMAGOLANo ratings yet

- Transportasi Distribusi MigasDocument25 pagesTransportasi Distribusi MigasDian Permatasari100% (1)

- The Kicker TranscriptionDocument4 pagesThe Kicker TranscriptionmilesNo ratings yet

- Virtual Assets Act, 2022Document18 pagesVirtual Assets Act, 2022Rapulu UdohNo ratings yet

- Brigade Product Catalogue Edition 20 EnglishDocument88 pagesBrigade Product Catalogue Edition 20 EnglishPelotudoPeloteroNo ratings yet

- Trade MarkDocument2 pagesTrade MarkRohit ThoratNo ratings yet

- Power Curbers, Inc. v. E. D. Etnyre & Co. and A. E. Finley & Associates, Inc., 298 F.2d 484, 4th Cir. (1962)Document18 pagesPower Curbers, Inc. v. E. D. Etnyre & Co. and A. E. Finley & Associates, Inc., 298 F.2d 484, 4th Cir. (1962)Scribd Government DocsNo ratings yet

- Building and Structural Construction N6 T1 2024 T2Document9 pagesBuilding and Structural Construction N6 T1 2024 T2FranceNo ratings yet

- Aakriti 1Document92 pagesAakriti 1raghav bansalNo ratings yet

- 928 Diagnostics Manual v2.7Document67 pages928 Diagnostics Manual v2.7Roger Sego100% (2)

- Famous Little Red Book SummaryDocument6 pagesFamous Little Red Book SummaryMatt MurdockNo ratings yet

- Comparative Study Between Online and Offilne Learning With Reference of Tutedude E-LearningDocument61 pagesComparative Study Between Online and Offilne Learning With Reference of Tutedude E-LearningDeeksha Saxena0% (2)