Professional Documents

Culture Documents

TLE4279 SiemensSemiconductorGroup

Uploaded by

Luis MezaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TLE4279 SiemensSemiconductorGroup

Uploaded by

Luis MezaCopyright:

Available Formats

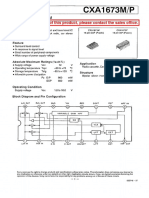

5-V Low-Drop Fixed Voltage Regulator TLE 4279

Features

• Output voltage tolerance ≤ ± 2 %

• Very low current consumption

• Early warning

• Reset output low down to VQ = 1 V

• Overtemperature protection

• Reverse polarity proof P-DIP-8-4

• Settable reset threshold

• Very low-drop voltage

• Wide temperature range

Type Ordering Code Package

TLE 4279 A on request P-DIP-8-4

TLE 4279 G Q67006-A9225 P-DSO-8-1 (SMD)

▼ TLE 4279 GM Q67006-A9307 P-DSO-14-4 (SMD) P-DSO-8-1

TLE 4279 GL Q67006-A9306 P-DSO-20-6 (SMD)

▼ New type

Functional Description

This device is a voltage regulator with a fixed 5-V output,

e.g. in a P-DSO-8-1 package. The maximum operating

P-DSO-20-6

voltage is 45 V. The output is able to drive a 150 mA

load. It is short circuit protected and the thermal

shutdown switches the output off if the junction

temperature is in excess of 150 °C. A reset signal is

generated for an output voltage of VQ < 4.6 V. The reset

threshold voltage can be decreased by external

connection of a voltage divider. The reset delay time can

be set by an external capacitor. If the application

requires pull up resistors at the logic outputs (Reset, P-DSO-14-4

Sense Out) the TLE 4269 with integrated resistors can

be used. It is also possible to supervise the input voltage by using an integrated

comparator to give a low voltage warning.

Semiconductor Group 1 1998-11-01

TLE 4279

Pin Configuration

(top view)

P-DIP-8-4 P-DSO-8-1

Ι 1 8 Q

Ι 1 8 Q

SΙ 2 7 SO

RE 3 6 R

SΙ 2 7 SO

D 4 5 GND

RE 3 6 R AEP01668

D 4 5 GND

AEP01813

Pin Definitions and Functions (TLE 4279 A and TLE 4279 G)

Pin No. Symbol Function

1 I Input; block directly to GND on the IC with a ceramic capacitor.

2 SI Sense input; if not needed connect to Q.

3 RE Reset threshold; if not needed connect to ground.

4 D Reset delay; to select the delay time, connect to GND via

external capacitor.

5 GND Ground

6 R Reset output; open-collector output

7 SO Sense output; open-collector output

8 Q 5-V output; connect to GND with a 10 µF capacitor, ESR < 10 Ω.

Semiconductor Group 2 1998-11-01

TLE 4279

Pin Configuration

(top view)

P-DSO-20-6

RE 1 20 SΙ

D 2 19 Ι

N.C. 3 18 N.C.

GND 4 17 GND

GND 5 16 GND

GND 6 15 GND

GND 7 14 GND

N.C. 8 13 N.C.

N.C. 9 12 Q

R 10 11 SO

AEP01802

Pin Definitions and Functions (TLE 4279 GL)

Pin No. Symbol Function

1 RE Reset threshold; if not needed connect to ground.

2 D Reset delay; to select delay time connect to GND via

external capacitor.

4-7, 14-17 GND Ground

10 R Reset output; open-collector output

11 SO Sense output; open-collector output

12 Q Output; connect to GND with 10 µF capacitor, ESR < 10 Ω

19 I Input; block directly to GND at the IC by a ceramic capacitor

20 SI Sense input; if not needed connect to Q

Semiconductor Group 3 1998-11-01

TLE 4279

Pin Configuration

(top view)

P-DSO-14-4

RE 1 14 SI

D 2 13 Ι

GND 3 12 GND

GND 4 11 GND

GND 5 10 GND

GND 6 9 Q

R 7 8 SO

AEP02254

Pin Definitions and Functions (TLE 4279 GM)

Pin No. Symbol Function

1 RE Reset threshold; if not needed connect to GND

2 D Reset delay; connect to GND via external delay capacitor for

setting delay time

3, 4, 5, 6 GND Ground

7 R Reset output; open-collector output

8 SO Sense output; open-collector output

9 Q 5-V output; connect to GND with 10 µF capacitor, ESR < 10 Ω

10, 11, 12 GND Ground

13 I Input; block to ground directly at the IC by a ceramic capacitor

14 SI Sense input; if not needed connect to Q

Semiconductor Group 4 1998-11-01

TLE 4279

Circuit Description

The control amplifier compares a reference voltage, made highly accurate by resistance

balancing, with a voltage proportional to the output voltage and drives the base of the

series PNP transistor via a buffer. Saturation control as a function of the load current

prevents any over-saturation of the power element.

In the reset generator block a comparator compares a reference voltage independent of

the input voltage with the scaled-down output voltage. If the output voltage reaches 4.6 V

the reset delay capacitor is discharged and the reset output is set to low. This low is

guaranteed down to an output voltage of 1 V. As the output voltage increases again,

from 4.6 V onward the reset delay capacitor is charged with constant current. When the

capacitor voltage reaches the upper switching threshold Vdt, the reset returns to high. By

choosing the value of this capacitor, the reset delay time can be selected over a wide

range. With the reset threshold input RE it is possible to lower the reset threshold Vrt. If

pin RE is connected to pin Q via a voltage divider, for example, the reset condition is

reached when this voltage is decreased below the switching threshold Vre of 1.35 V.

Another comparator compares the signal of the pin SI, normally fed by a voltage divider

from the input voltage, with the reference and gives an early warning on the pin SO. It is

also possible to superwise an other voltage e.g. of a second regulator, or to build a

watchdog circuit with few external components.

Application Description

The input capacitor CI is necessary for compensating line influences. Using a resistor of

approx. 1 Ω in series with CI, the oscillating circuit consisting of input inductivity and input

capacitance can be damped. The output capacitor CQ is necessary for the stability of the

regulating circuit. Stability is guaranteed at values ≥ 10 µF and an ESR ≤ 10 Ω within the

operating temperature range. Both reset output and sense output are open collector

outputs and have to be connected to 5 V output via external pull-up resistors ≥ 10 kΩ.

For small tolerances of the reset delay the spread of the capacitance of the delay

capacitor and its temperature coefficient should be noted.

Semiconductor Group 5 1998-11-01

TLE 4279

Ι Q

Error

Amplifier

Reference Current and

Saturation

Control

Trimming

D R

RE Reference SO

SI

AEB01955

Block Diagram

Semiconductor Group 6 1998-11-01

TLE 4279

Absolute Maximum Ratings

Tj = – 40 to 150 °C

Parameter Symbol Limit Values Unit Notes

min. max.

Input

Input voltage VI – 40 45 V –

Input current II – – – internal limited

Sense Input

Input voltage VSI – 0.3 45 V –

Input current ISI 1 1 mA –

Reset Threshold

Voltage VRE – 0.3 7 V –

Current IRE – 10 10 mA –

Reset Delay

Voltage VD – 0.3 7 V –

Current ID – – – internal limited

Ground

Current IGND 50 – mA –

Reset Output

Voltage VR – 0.3 7 V –

Current IR – – – internal limited

Sense Output

Voltage VSO – 0.3 7 V –

Current ISO – – – internal limited

Semiconductor Group 7 1998-11-01

TLE 4279

Absolute Maximum Ratings (cont’d)

Tj = – 40 to 150 °C

Parameter Symbol Limit Values Unit Notes

min. max.

5-V Output

Output voltage VQ – 0.3 7 V –

Output current IQ –5 – mA –

Temperature

Junction temperature Tj – 150 °C –

Storage temperature TStg – 50 150 °C –

Operating Range

Input voltage VI – 45 V –

Junction temperature Tj – 40 150 °C –

Thermal Data

Junction-ambient Rthja – 100 K/W P-DIP-8-4

200 K/W P-DSO-8-1

70 K/W P-DSO-14-4

70 K/W P-DSO-20-6

Rthjc – 60 K/W P-DIP-8-4

60 K/W P-DSO-8-1

30 K/W P-DSO-14-4

30 K/W P-DSO-20-6

Semiconductor Group 8 1998-11-01

TLE 4279

Characteristics

VI = 13.5 V; Tj = – 40 °C < Tj < 125 °C

Parameter Symbol Limit Values Unit Measuring

Condition

min. typ. max.

Output voltage VQ 4.90 5.00 5.10 V 1 mA ≤ IQ ≤ 100 mA

6 V ≤ VI ≤ 16 V

Current limit IQ 150 200 500 mA –

Current consumption; Iq – 150 300 µA IQ ≤ 1 mA, Tj < 85 °C

Iq = II – IQ

Current consumption; Iq – 250 700 µA IQ = 10 mA

Iq = II – IQ

Current consumption; Iq – 2 8 mA IQ = 50 mA

Iq = II – IQ

Drop voltage Vdr – 0.25 0.5 V IQ = 100 mA1)

Load regulation ∆VQ – 10 30 mV IQ = 5 mA to 100 mA

Line regulation ∆VQ – 10 40 mV VI = 6 V to 26 V

IQ = 1 mA

Reset Generator

Switching threshold Vrt 4.50 4.60 4.80 V –

Reset low voltage VR – 0.1 0.4 V Rextern = 20 kΩ

Delay switching Vdt 1.4 1.8 2.2 V –

threshold

Switching threshold Vst 0.3 0.45 0.60 V –

Reset delay low voltage VD – – 0.1 V VQ < VRT

Charge current Id 3.0 6.5 9.5 µA VD = 1 V

1)

Drop voltage = VI – VQ (measured when the output voltage has dropped 100 mV from the

nominal value obtained at 13.5 V input.)

Semiconductor Group 9 1998-11-01

TLE 4279

Characteristics (cont’d)

VI = 13.5 V; Tj = – 40 °C < Tj < 125 °C

Parameter Symbol Limit Values Unit Measuring

Condition

min. typ. max.

Delay time L → H td 17 28 – ms CD = 100 nF

Delay time H → L tt – 1 – µs CD = 100 nF

Switching voltage Vre 1.26 1.35 1.44 V VQ > 3.5 V

Input Voltage Sense

Sense threshold high Vsi, high 1.24 1.31 1.38 V –

Sence threshold low Vsi, high 1.16 1.20 1.28 V –

Sense output VSO,low – 0.1 0.4 V VSI < 1.20 V;

low voltage VI > 3 V

Rextern = 20 kΩ

Sense input current ISI –1 0.1 1 µA –

Semiconductor Group 10 1998-11-01

TLE 4279

Measuring Circuit (P-DIP-8-4, P-DSO-8-1)

VΙ

< t RR

V RT

VQ

dV Ι d

= VDT

dt C D

VST

VD

t RR

td

V RO

Power-on-Reset Thermal Voltage Dip Undervoltage Secondary Overload

Shutdown at Input Spike at Output AED01542

Reset Timing Diagram

Semiconductor Group 11 1998-11-01

TLE 4279

VΙ

< t RR

V RT

VQ

dV Ι d

= VDT

dt C D

VST

VD

t RR

td

V RO

Power-on-Reset Thermal Voltage Dip Undervoltage Secondary Overload

Shutdown at Input Spike at Output AED01542

Sence Input Timing Diagram

Semiconductor Group 12 1998-11-01

TLE 4279

Charge Current Id versus Switching Voltage Vdt and Vst versus

Temperature Tj Temperature Tj

AED01803 AED01804

16 3.2

Ιd µA VD V

14 2.8

V Ι = 13.5 V

V Ι = 13.5 V

V C = 1.0 V

12 2.4

10 2.0 Vdt

8 1.6

6 1.2

4 0.8

Vst

2 0.4

0 0

-40 0 40 80 120 C 160 -40 0 40 80 120 C 160

Tj Tj

Drop Voltage Vdr versus Reset Switching Threshold Vre

Output Current IQ versus Temperature Tj

AED01805 AED01806

500 1.7

V dr Vre V

mV

1.6

400

1.5

1.4

300

Tj = 125 C 1.3

200

1.2

Tj = 25 C

1.1

100

1.0

0 0.9

0 30 60 90 120 mA 180 -40 0 40 80 120 C 160

ΙQ Tj

Semiconductor Group 13 1998-11-01

TLE 4279

Current Consumption Iq versus Output Voltage VQ versus

Input Voltage VI Input Voltage VI

AED01807 AED01808

30 12

Ι q mA VQ

V

25 10

20 8

RL = 33 Ω

15 6

RL = 50 Ω

10 4

RL = 50 Ω

5 RL = 100 Ω 2

RL = 200 Ω

0 0

0 10 20 30 40 V 50 0 2 4 6 8 V 10

VΙ VΙ

Sense Threshold Vsi Output Voltage VQ versus

versus Temperature Tj Temperature Tj

AED01809 AED01671

1.6 5.2

V si VQ V

V

V Ι = 13.5 V

1.5 5.1

V Ι = 13.5 V

1.4 5.0

Sense Output High

1.3 4.9

Sense Output Low

1.2 4.8

1.1 4.7

1.0 4.6

-40 0 40 80 120 C 160 -40 0 40 80 120 C 160

Tj Tj

Semiconductor Group 14 1998-11-01

TLE 4279

Output Current IQ versus Current Consumption Iq versus

Input Voltage VI Output Current IQ

AED01810 AED01811

350 12

Ι Q mA Ι q mA

300

10

V Ι = 13.5 V

250 Tj = 25 C

Tj = 25 C 8

200

6

Tj = 125 C

150

4

100

2

50

0 0

0 10 20 30 40 V 50 0 20 40 60 80 mA 120

VΙ ΙQ

Current Consumption Iq versus

Output Current IQ

AED01812

1.6

Ιq mA

1.4

V Ι = 13.5 V

Tj = 25 C

1.2

1.0

0.8

0.6

0.4

0.2

0

0 10 20 30 40 mA 50

ΙQ

Semiconductor Group 15 1998-11-01

TLE 4279

Package Outlines

P-DIP-8-4

(Plastic Dual In-line Package)

GPD05583

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”

Dimensions in mm

Semiconductor Group 16 1998-11-01

TLE 4279

P-DSO-8-1 (SMD)

(Plastic Dual Small Outline Package)

GPS05121

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”

SMD = Surface Mounted Device Dimensions in mm

Semiconductor Group 17 1998-11-01

TLE 4279

P-DSO-20-6 (SMD)

(Plastic Dual Small Outline Package)

0.35 x 45˚

2.65 max

2.45 -0.2

7.6 -0.2 1)

0.2 -0.1

9

0.23 +0.0

x

8˚ ma

1.27 0.4 +0.8

0.35 +0.15 2) 0.1 10.3 ±0.3

0.2 24x

20 11

GPS05094

1 12.8 1) 10

-0.2

Index Marking

1) Does not include plastic or metal protrusions of 0.15 max per side

2) Does not include dambar protrusion of 0.05 max per side

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”

SMD = Surface Mounted Device Dimensions in mm

Semiconductor Group 18 1998-11-01

TLE 4279

P-DSO-14-4 (SMD)

(Plastic Dual Small Outline Package)

0.35 x 45˚

1.75 max

1)

1.45 -0.2

4 -0.2

0.19 +0.06

0.2 -0.1

8˚ max.

1.27

0.1 0.4 +0.8

0.35 +0.15 2)

0.2 14x

6 ±0.2

14 8

1 7

8.75 -0.21)

Index Marking

1) Does not include plastic or metal protrusion of 0.15 max. per side

2) Does not include dambar protrusion of 0.05 max. per side GPS05093

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”

SMD = Surface Mounted Device Dimensions in mm

Semiconductor Group 19 1998-11-01

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Tle 4269Document19 pagesTle 4269Edinaldo RamosNo ratings yet

- TLE4470Document24 pagesTLE4470ricahard61No ratings yet

- 5-V Low-Drop Voltage Regulator TLE 4263: FeaturesDocument17 pages5-V Low-Drop Voltage Regulator TLE 4263: FeaturesWelleyNo ratings yet

- DC Motor Driver IC Controls Up to 1ADocument13 pagesDC Motor Driver IC Controls Up to 1Atigras6010No ratings yet

- TLE7209 R InfineonDocument16 pagesTLE7209 R Infineonmobil benerNo ratings yet

- Data Sheet TLE4262G Regulador 5v 20 PinesDocument16 pagesData Sheet TLE4262G Regulador 5v 20 Pinesaagreco73No ratings yet

- Data SheetDocument19 pagesData SheetDiego CaceresNo ratings yet

- Regulador de Tension TLE4267-DS-v02 - 51-EnDocument23 pagesRegulador de Tension TLE4267-DS-v02 - 51-EnJorge Martinez PerezNo ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 FeaturesDocument29 pages7 A H-Bridge For DC-Motor Applications TLE 6209 R: 1 1.1 Featureswtn2013No ratings yet

- Control de Garganta TACDocument15 pagesControl de Garganta TACmario rosasNo ratings yet

- Infineon TLE6209R DS v03 02 enDocument30 pagesInfineon TLE6209R DS v03 02 enRoger SegoNo ratings yet

- Dual Low Drop Voltage Regulator TLE 7469: FeaturesDocument22 pagesDual Low Drop Voltage Regulator TLE 7469: FeaturesPabloLabruneNo ratings yet

- Datasheet 4269Document19 pagesDatasheet 4269Alexandre Da Silva PintoNo ratings yet

- 1 Tle5206 2 - 1Document23 pages1 Tle5206 2 - 1Fran CastanoNo ratings yet

- TLE42766 Siemens Elenota - PLDocument16 pagesTLE42766 Siemens Elenota - PLAnuar Angrac Lopez CruzNo ratings yet

- Tle5205 2Document23 pagesTle5205 2Richard MachadoNo ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pages7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareNo ratings yet

- Infineon TLE4299V33 DS v01 - 01 enDocument25 pagesInfineon TLE4299V33 DS v01 - 01 enStelian DobreNo ratings yet

- 7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetDocument4 pages7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetallisonNo ratings yet

- Repeater Interface: Technical SpecificationDocument2 pagesRepeater Interface: Technical SpecificationThanh Kieu TienNo ratings yet

- FT 28Document3 pagesFT 28joako garciaNo ratings yet

- Ne5521 Sa5521 2Document11 pagesNe5521 Sa5521 2José AdelinoNo ratings yet

- A2C33648Document27 pagesA2C33648mohhizbar100% (1)

- NCR320PAS / NCR321PAS: 1. Product ProfileDocument18 pagesNCR320PAS / NCR321PAS: 1. Product ProfileЕвгений ИвановNo ratings yet

- Sensor Less Speed Control of BLDC Motor - Rev 2Document12 pagesSensor Less Speed Control of BLDC Motor - Rev 2sureshNo ratings yet

- 8-Channel Darlington Driver for Relays & MotorsDocument8 pages8-Channel Darlington Driver for Relays & MotorsRogerNo ratings yet

- 5-V Low-Drop Voltage Regulator TLE 4260Document15 pages5-V Low-Drop Voltage Regulator TLE 4260marce822No ratings yet

- TLE4260Document15 pagesTLE4260NoelNo ratings yet

- Infineon TLE4275V50 DS v01 - 07 en PDFDocument17 pagesInfineon TLE4275V50 DS v01 - 07 en PDFjoseNo ratings yet

- 2-Phase Stepper-Motor Driver TLE 4728 G: Bipolar-IC FeaturesDocument26 pages2-Phase Stepper-Motor Driver TLE 4728 G: Bipolar-IC FeaturesMohammad RanjbarNo ratings yet

- Oscilador de PFC Fuente Toshiba 2A20112SPDocument8 pagesOscilador de PFC Fuente Toshiba 2A20112SPAntonio ChavezNo ratings yet

- PCB DiagramDocument6 pagesPCB Diagramfreitastsp9166No ratings yet

- 4279G InfenionDocument18 pages4279G InfenionAlver TuizaNo ratings yet

- 2576 LDocument9 pages2576 LclanonNo ratings yet

- NE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsDocument5 pagesNE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsAriel SanusiNo ratings yet

- SONY,,: For The Availability of This Product, Please Contact The Sales OfficeDocument8 pagesSONY,,: For The Availability of This Product, Please Contact The Sales OfficeERNANIPARNOWNo ratings yet

- Low-Drop Voltage Regulator TLE 4276: FeaturesDocument19 pagesLow-Drop Voltage Regulator TLE 4276: FeaturesshtormlNo ratings yet

- SP490E/SP491E Enhanced Full Duplex RS-485 Transceivers: DescriptionDocument12 pagesSP490E/SP491E Enhanced Full Duplex RS-485 Transceivers: DescriptionCarlos AcostaNo ratings yet

- Regulador 4271-2g PLD MercedesDocument23 pagesRegulador 4271-2g PLD MercedesDiego CaceresNo ratings yet

- Data Sheet Se5004L: 5 GHZ, 26Dbm Power Amplifier With Power Detector Applications Product DescriptionDocument9 pagesData Sheet Se5004L: 5 GHZ, 26Dbm Power Amplifier With Power Detector Applications Product DescriptionashfaqNo ratings yet

- 5-V Low-Drop Fixed Voltage Regulator TLE 4271 FeaturesDocument20 pages5-V Low-Drop Fixed Voltage Regulator TLE 4271 FeaturesPablo CervantesNo ratings yet

- 4271 2GDocument24 pages4271 2GAlexandre Dantas HenriqueNo ratings yet

- 5A, 36V, 500Khz Step-Down Converter: General Description FeaturesDocument14 pages5A, 36V, 500Khz Step-Down Converter: General Description FeaturesHitesh GambhavaNo ratings yet

- TLE 6251 G: High Speed CAN-Transceiver With Wake DetectionDocument32 pagesTLE 6251 G: High Speed CAN-Transceiver With Wake DetectionDragos CezarNo ratings yet

- RT9018ADocument12 pagesRT9018Abusamawan wayanNo ratings yet

- AL8862QDocument17 pagesAL8862QIvo MatosNo ratings yet

- Low Dropout Linear Fixed Voltage RegulatorDocument26 pagesLow Dropout Linear Fixed Voltage RegulatorNur Aishi Putri SyarilNo ratings yet

- TrasDocument11 pagesTrasAmauri RogérioNo ratings yet

- DSA00323215Document38 pagesDSA00323215Mariano AmorNo ratings yet

- DatasheetDocument16 pagesDatasheetAndres GuerreroNo ratings yet

- Rp130X Series: Low Noise 150ma Ldo RegulatorDocument33 pagesRp130X Series: Low Noise 150ma Ldo RegulatorСергей БрегедаNo ratings yet

- PH5030AL: 1. Product ProfileDocument14 pagesPH5030AL: 1. Product ProfileJosue Rafael BorjasNo ratings yet

- 81r PDFDocument29 pages81r PDFDjalma MotaNo ratings yet

- PLL XR2212 ExarCorporationDocument20 pagesPLL XR2212 ExarCorporationHoan TranNo ratings yet

- DatasheetDocument14 pagesDatasheetsamaya egNo ratings yet

- Richtek Tech R7731AGE C250411Document14 pagesRichtek Tech R7731AGE C250411Игорь ПочепаNo ratings yet

- System Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS SwitchesDocument50 pagesSystem Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS Switchescork_ieNo ratings yet

- Samsung Ua22!26!32c4000p Chassis n98bDocument61 pagesSamsung Ua22!26!32c4000p Chassis n98bLuis MezaNo ratings yet

- Service Manual DLA-32H1 080402Document36 pagesService Manual DLA-32H1 080402elyuyaNo ratings yet

- Panel LedDocument25 pagesPanel LedAsallimitNo ratings yet

- Global LCD Panel Specification GuideDocument27 pagesGlobal LCD Panel Specification GuideLuis MezaNo ratings yet

- Panel LedDocument25 pagesPanel LedAsallimitNo ratings yet

- Panel LedDocument25 pagesPanel LedAsallimitNo ratings yet

- Panel LedDocument25 pagesPanel LedAsallimitNo ratings yet

- Panel LedDocument25 pagesPanel LedAsallimitNo ratings yet

- Panel LedDocument25 pagesPanel LedAsallimitNo ratings yet

- Silcostart: Static Motor Softstarter Solving Starting ProblemsDocument4 pagesSilcostart: Static Motor Softstarter Solving Starting ProblemsMohamed AlkharashyNo ratings yet

- EyeQueue User Guide Version 8.0.8Document318 pagesEyeQueue User Guide Version 8.0.8Jeff EdstromNo ratings yet

- Liebert NPS-IDocument38 pagesLiebert NPS-IMahesh KumbharNo ratings yet

- Configure a L2TPDocument3 pagesConfigure a L2TPVentas Nature PrimeNo ratings yet

- Everything You Need to Know About Rekeying Schlage LocksDocument19 pagesEverything You Need to Know About Rekeying Schlage LocksPKMNo ratings yet

- On Target (2019 - Vol. 1) Diagnostic FordDocument6 pagesOn Target (2019 - Vol. 1) Diagnostic FordcherokewagNo ratings yet

- Service Manual: Blu-Ray Disc /DVD ReceiverDocument130 pagesService Manual: Blu-Ray Disc /DVD Receiverboroda241090% (10)

- AnnabellaBracco Resume 2021Document1 pageAnnabellaBracco Resume 2021ANNABELLA BRACCONo ratings yet

- Apple TimelineDocument1 pageApple Timelinekunwar.avneeshNo ratings yet

- Introduction To Civil Engineering (Engineering Method)Document11 pagesIntroduction To Civil Engineering (Engineering Method)ongica jamesNo ratings yet

- 02 5G Xhaul Transport - BRKSPM-2012 BRKSPG-2680Document98 pages02 5G Xhaul Transport - BRKSPM-2012 BRKSPG-2680MakusNo ratings yet

- Loan Prediction SystemDocument31 pagesLoan Prediction SystemFakorede Akinwande alexNo ratings yet

- Design and Build An Automatic PCB Drilling MachineDocument4 pagesDesign and Build An Automatic PCB Drilling MachinemoysesdutraNo ratings yet

- John Sloman EconomicsDocument4 pagesJohn Sloman Economicsdevyansh.dhall2807No ratings yet

- Control PSP Audio & Video with Remote, Headphones, CameraDocument1 pageControl PSP Audio & Video with Remote, Headphones, CameravadivelanNo ratings yet

- Toyota Supra 94-98 Syvecs ECU Installation GuideDocument5 pagesToyota Supra 94-98 Syvecs ECU Installation GuideRajibNo ratings yet

- IP & Capacitor Price List 14 FEB 2014 PDFDocument76 pagesIP & Capacitor Price List 14 FEB 2014 PDFPhaníiPunnamNo ratings yet

- To Study About Various Types of Mode ofDocument20 pagesTo Study About Various Types of Mode ofVikas AgrawalNo ratings yet

- Low Power MuxDocument4 pagesLow Power MuxPromit MandalNo ratings yet

- Symbol Explanations For Commissioning DiagramDocument8 pagesSymbol Explanations For Commissioning DiagramBrahim CherguiNo ratings yet

- Digilocker VacDocument5 pagesDigilocker Vacanshikasgh3012No ratings yet

- CCW332 - Digital Marketing - SyllabusDocument2 pagesCCW332 - Digital Marketing - SyllabusV ArunachalamNo ratings yet

- Method Statement For Drainage Pipe SystemDocument15 pagesMethod Statement For Drainage Pipe SystemaNo ratings yet

- CBR500R Owner'S Manual: 32MKPF10 00X32-MKP-F100Document134 pagesCBR500R Owner'S Manual: 32MKPF10 00X32-MKP-F100edwinNo ratings yet

- Usabilidad de Un Simulador para La Enseñanza de La Programación de SistemasDocument18 pagesUsabilidad de Un Simulador para La Enseñanza de La Programación de SistemasRAFAEL ANTONIO BORDA JIMENEZNo ratings yet

- LabVIEW - FPGA Module User ManualDocument62 pagesLabVIEW - FPGA Module User ManualRajasekar PichaimuthuNo ratings yet

- Curriculum Vitae: Personal InformationDocument2 pagesCurriculum Vitae: Personal InformationAnonymous 2HxqQVNo ratings yet

- Week 3 L4 (Design Thinking)Document16 pagesWeek 3 L4 (Design Thinking)buy inviteeNo ratings yet

- b0700bp CDocument90 pagesb0700bp Cyoucef hamzaNo ratings yet

- Guidelines For Passenger Services at European AirportsDocument120 pagesGuidelines For Passenger Services at European AirportsJPFJ12100% (2)