Professional Documents

Culture Documents

Computer Organization and Software Systems: BITS Pilani Contact Session

Computer Organization and Software Systems: BITS Pilani Contact Session

Uploaded by

SUBRAMANIAM NOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Computer Organization and Software Systems: BITS Pilani Contact Session

Computer Organization and Software Systems: BITS Pilani Contact Session

Uploaded by

SUBRAMANIAM NCopyright:

Available Formats

Computer Organization

and Software Systems

CONTACT SESSION 3

BITS Pilani

Pilani Campus

Today’s Session

Contact List of Topic Title Text/Ref

Hour Book/external

resource

5-6 • Memory Hierarchy T1

• Cache Memories

• Generic Cache Memory Organization

• Direct-Mapped Caches

• Fully Associative Caches

BITS Pilani, Pilani Campus

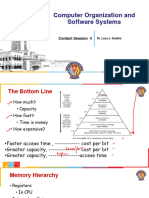

Memory Hierarchy

• Registers

– In CPU

• Internal or Main memory

– May include one or more levels of cache

– “RAM”

• External memory

– Backing store

BITS Pilani, Pilani Campus

Faster access time, __________________cost per bit.

Greater Capacity, __________________cost per bit.

Greater Capacity,___________________Access time.

BITS Pilani, Pilani Campus

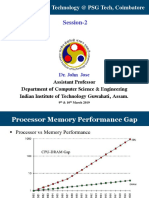

Performance enhancement -

Motivation

BITS Pilani, Pilani Campus

Performance enhancement -

Motivation

Locality of Reference

During the course of the execution of a

program, memory references tend to

cluster

• Temporal locality: Locality in time

• If an item is referenced, it will tend

to be referenced again soon

• Spatial locality: Locality in space

• If an item is referenced, items

whose addresses are close by will

tend to be referenced soon.

BITS Pilani, Pilani Campus

Example

product = 1;

for ( i = 0; i < n-1; i++)

product = product * a[i] ;

Data :

• Access array elements in succession – spatial locality

• Reference to “product” in each iteration – Temporal

locality

Instructions :

• Reference instructions in sequence : Spatial locality

• Looping through : Temporal locality

BITS Pilani, Pilani Campus

Performance enhancement -

Motivation

BITS Pilani, Pilani Campus

Cache

BITS Pilani

Pilani Campus

Cache

• Small, fast memory

• Sits between normal main memory and CPU

• May be located on CPU chip or separate module

BITS Pilani, Pilani Campus

Cache and Main Memory Structure

BITS Pilani, Pilani Campus

START

Cache Read Operation

Receive address (RA)

From CPU

Is block No Access main memory

containing RA for block containing

word in Cache? RA word

Yes

Fetch RA word and Allocate cache line

deliver to CPU for main memory

block

Load main memory Deliver RA word to

block in to cache line CPU

DONE

Performance of cache

• Hit ratio : Number of Hits / total references

to memory

• Hit

• Miss

BITS Pilani, Pilani Campus

Read Hit

BITS Pilani, Pilani Campus

Read Miss

BITS Pilani, Pilani Campus

Write hit

BITS Pilani, Pilani Campus

Write miss

BITS Pilani, Pilani Campus

Mapping Function

• How memory blocks are mapped to cache lines

• Three types

– Direct mapping

– Associative mapping

– Set Associative mapping

BITS Pilani, Pilani Campus

Back

Mapping Function

• 16 Bytes main memory

– How many address bits

are required?

• Memory block size is 4

bytes

• Cache of 8 Byte

– How many cache lines?

BITS Pilani, Pilani Campus

Back

Mapping Function

• 16 Bytes main memory

– How many address bits are

required? 4 bits

• Memory block size is 4 bytes

• Cache of 8 Byte

– How many cache lines?

BITS Pilani, Pilani Campus

Back

Mapping Function

• 16 Bytes main

memory

– How many

address bits are

required?

• Memory block size

is 4 bytes cache is 2 lines

• Cache of 8 Byte ( 4 bytes per Line)

– How many cache

lines?

BITS Pilani, Pilani Campus

Back

Mapping Function

• 16 Bytes main Block 0

(4 bytes)

memory

Line 0 Block 1

– How many address (4 bytes) (4 bytes)

bits are required? Line 1 Block 2

(4 bytes) (4 bytes)

• Memory block size is

Block 3

4 bytes Cache

(4 bytes)

Memory

• Cache of 8 Byte

Main

– How many cache Memory

lines?

– cache is 2 lines ( 4

bytes per Line)

BITS Pilani, Pilani Campus

Direct Mapping

• Each block of main memory maps to

only one cache line

– i.e. if a block is in cache, it must

be in one specific place

– i = j modulo m

where i = cache line number

j = main memory block no.

m = no.of lines in the cache

• Address is split in three parts:

• Tag

• Line

• Word

BITS Pilani, Pilani Campus

Direct Mapping Cache Organization

Main Memory B0

B1

L0 B2

L1 |

|

L2

|

L3 |

|

L4 B12

B15

Cache Memory B23

B63

BITS Pilani, Pilani Campus

Direct Mapping Cache Organization

BITS Pilani, Pilani Campus

Direct mapping- Summary

Address length = (s+w) bits

Number of addressable units = 2s+w words or bytes

Block size = line size = 2w words or bytes

Number of blocks in main memory = 2s+w / 2w = 2s

Number of lines in cache = m = 2r

Size of tag =(s-r) bits

BITS Pilani, Pilani Campus

Direct mapping Summary

1 1 2

Tag s-r Line or Slot r Word w

BITS Pilani, Pilani Campus

Direct Mapping pros & cons

• Simple

• Inexpensive

• Fixed location for given block

– If a program accesses 2 blocks that map to the

same line repeatedly, cache misses are very high

BITS Pilani, Pilani Campus

Problem 1

Given :

• Cache of 64kByte, Cache block of 4 bytes

• 16MBytes main memory

Find out

a) Number of bits required to address the memory

b) Number of blocks in main memory

c) Number of cache lines

d) Number of bits required to identify a word (byte) in

a block?

e) Number of bits to identify a block

f) Tag, Line, Word

BITS Pilani, Pilani Campus

Solution

Given :

• Cache of 64kByte, Cache block of 4 bytes

• 16MBytes main memory

Find out

a) Number of bits required to address the memory

24 bits

b) Number of blocks in main memory

4M blocks

c) Number of cache lines

16K lines

BITS Pilani, Pilani Campus

Solution 1

Given :

• Cache of 64kByte, Cache block of 4 bytes

• 16MBytes main memory

Find out

d) Number of bits required to identify a word (byte) in a

block?

2 bits

e) Number of bits required to identify block

22 bits

f) Tag, Line, Word

Tag s-r Line r Word w

8 14 2

BITS Pilani, Pilani Campus

Problem 2

BITS Pilani, Pilani Campus

Solution 2

TAG =8 LINE=5 WORD=3

BITS Pilani, Pilani Campus

Solution 2

BITS Pilani, Pilani Campus

Solution 2

: Number of cache line 32

Block size : 8 bytes

Total bytes saved in cache = 32 x 8 bytes = 256bytes ( excluding tag)

Tag bits saved : 32 x 8 bits = 256 bits = 32 bytes

Total bytes saved in cache = 256bytes + 32 bytes = 288 Bytes ( including tag)

BITS Pilani, Pilani Campus

Solution 2

Two or more blocks can be mapped to same cache line.

To distinguish between the blocks, tag bits are used.

BITS Pilani, Pilani Campus

Problem 3

Consider a direct-mapped cache with 64 cache lines and

a block size of 16 bytes and main memory of 8K (Byte

addressable memory) . To what line number does byte

address 1200H map?

32nd line.

BITS Pilani, Pilani Campus

You might also like

- Grade 10 ICT English Medium Second Term Test North Western Province Paper 2018Document13 pagesGrade 10 ICT English Medium Second Term Test North Western Province Paper 2018afthab741No ratings yet

- Onity Onportal Lock Management System: User ManualDocument62 pagesOnity Onportal Lock Management System: User ManualTheHerrikoTabernaNo ratings yet

- Cache MemoryDocument72 pagesCache MemoryMaroun Bejjany67% (3)

- Cache MemoryDocument29 pagesCache MemoryBudditha HettigeNo ratings yet

- Handbook of Digital Techniques For High-Speed DesignDocument29 pagesHandbook of Digital Techniques For High-Speed DesignJustin FozzardNo ratings yet

- Programming with 64-Bit ARM Assembly Language: Single Board Computer Development for Raspberry Pi and Mobile DevicesFrom EverandProgramming with 64-Bit ARM Assembly Language: Single Board Computer Development for Raspberry Pi and Mobile DevicesNo ratings yet

- Nintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8From EverandNintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8No ratings yet

- Computer Organization and Architecture: Cache MemoryDocument57 pagesComputer Organization and Architecture: Cache MemoryRyan R. Sarco100% (1)

- COSS Mid Sem Session 1 - 8 PDFDocument412 pagesCOSS Mid Sem Session 1 - 8 PDFRaviShankar100% (1)

- Computer Organization & Architecture: BITS PilaniDocument12 pagesComputer Organization & Architecture: BITS PilaniRashmitha RavichandranNo ratings yet

- Computer Organization & ArchitectureDocument17 pagesComputer Organization & ArchitectureRashmitha RavichandranNo ratings yet

- COSS - Contact Session - 4Document34 pagesCOSS - Contact Session - 4Prasana VenkateshNo ratings yet

- Computer Organization and Software Systems 3: Contact SessionDocument60 pagesComputer Organization and Software Systems 3: Contact SessionArun chauhanNo ratings yet

- COSS - Contact Session - 4 - With AnnotatonDocument44 pagesCOSS - Contact Session - 4 - With Annotatonnotes.chandanNo ratings yet

- Cache MappingDocument44 pagesCache MappingxoeaeoxNo ratings yet

- Cache Memory - Mapping FunctionsDocument36 pagesCache Memory - Mapping FunctionsMajety S LskshmiNo ratings yet

- Chap 6Document48 pagesChap 6siddhiNo ratings yet

- 04 Cache MemoryDocument36 pages04 Cache Memorymubarra shabbirNo ratings yet

- Real Time System - : BITS PilaniDocument38 pagesReal Time System - : BITS PilanivithyaNo ratings yet

- 41 CALD Lec 41 Cache Direct Mapping Dated 19 May 2023 Lecture SlidesDocument13 pages41 CALD Lec 41 Cache Direct Mapping Dated 19 May 2023 Lecture SlidesAndrew OlsenNo ratings yet

- 15IF11 Multicore BDocument36 pages15IF11 Multicore BRakesh VenkatesanNo ratings yet

- Computer Arch 06Document41 pagesComputer Arch 06NaheedNo ratings yet

- CachesDocument56 pagesCachesAasma KhalidNo ratings yet

- Cache MemoryDocument39 pagesCache MemoryhariprasathkNo ratings yet

- 1 MergedDocument493 pages1 MergedMandheer PabrejaNo ratings yet

- Computer Organization and Software Systems: BITS Pilani Contact SessionDocument63 pagesComputer Organization and Software Systems: BITS Pilani Contact SessionSUBRAMANIAM NNo ratings yet

- 34-Cache Memory Block Identification in Direct Mapping, Associate Mapping and Set Associate-06-03-2Document36 pages34-Cache Memory Block Identification in Direct Mapping, Associate Mapping and Set Associate-06-03-2Rishabh Paul 21BCE2019No ratings yet

- Cache + Associations Ch-4Document52 pagesCache + Associations Ch-4ahsan2020azizNo ratings yet

- Cache Memory: Prepared by - : Manan Mewada (TA, IET)Document19 pagesCache Memory: Prepared by - : Manan Mewada (TA, IET)jayNo ratings yet

- Computer Organization and Software Systems Contact Session 2Document46 pagesComputer Organization and Software Systems Contact Session 2Arun chauhanNo ratings yet

- Computer Organization: Lec #10: Cache Memory Bnar MustafaDocument22 pagesComputer Organization: Lec #10: Cache Memory Bnar Mustafazara qojo (زارا)No ratings yet

- Computer Organization and Software Systems: BITS Pilani Contact SessionDocument46 pagesComputer Organization and Software Systems: BITS Pilani Contact SessionSUBRAMANIAM NNo ratings yet

- Module 4: Memory System Organization & ArchitectureDocument97 pagesModule 4: Memory System Organization & ArchitectureSurya SunderNo ratings yet

- Cache and Memory SystemsDocument100 pagesCache and Memory SystemsJay JaberNo ratings yet

- ECE875Spr23 Week07a Lecture11Document34 pagesECE875Spr23 Week07a Lecture11Sivaprasad Reddy BogireddyNo ratings yet

- 04 - Cache MemoryDocument47 pages04 - Cache MemoryuabdulgwadNo ratings yet

- 04 - Cache Memory (Compatibility Mode)Document12 pages04 - Cache Memory (Compatibility Mode)John PhanNo ratings yet

- 9장 캐시Document65 pages9장 캐시민규No ratings yet

- ESD Merged Till CS6Document237 pagesESD Merged Till CS6Rahamtulla MohammadNo ratings yet

- Cache OrganizationDocument27 pagesCache OrganizationAbhishek karwalNo ratings yet

- 3 AddressingModesDocument26 pages3 AddressingModesf20212867No ratings yet

- Embedded System Design: BITS Pilani, Pilani CampusDocument35 pagesEmbedded System Design: BITS Pilani, Pilani CampusRahamtulla MohammadNo ratings yet

- This Unit: Caches: - Basic Memory Hierarchy ConceptsDocument24 pagesThis Unit: Caches: - Basic Memory Hierarchy ConceptsjameskipkosgeiNo ratings yet

- Computer Organization & Architecture: BITS PilaniDocument13 pagesComputer Organization & Architecture: BITS PilaniRashmitha RavichandranNo ratings yet

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocument71 pagesWilliam Stallings Computer Organization and Architecture 8th Edition Cache MemoryBum TumNo ratings yet

- 04 - Cache MemoryDocument71 pages04 - Cache MemoryDoc TelNo ratings yet

- Lec 4Document31 pagesLec 4jettychetan524No ratings yet

- Course Code: CS 283 Course Title: Computer Architecture: Class Day: Friday Timing: 12:00 To 1:30Document23 pagesCourse Code: CS 283 Course Title: Computer Architecture: Class Day: Friday Timing: 12:00 To 1:30Niaz Ahmed KhanNo ratings yet

- William Stallings Computer Organization and Architecture 7th Edition Cache MemoryDocument57 pagesWilliam Stallings Computer Organization and Architecture 7th Edition Cache MemoryDurairajan AasaithambaiNo ratings yet

- Cache Memories September 30, 2008: TopicsDocument32 pagesCache Memories September 30, 2008: TopicsserarNo ratings yet

- Data Warehouse Lecture 10Document32 pagesData Warehouse Lecture 10Anshul RohillaNo ratings yet

- 04 Cache MemoryDocument75 pages04 Cache MemorySangeetha ShankaranNo ratings yet

- Microprocessor & Computer Architecture (Μpca) : Unit 4: Cache - 6 OptimizationDocument9 pagesMicroprocessor & Computer Architecture (Μpca) : Unit 4: Cache - 6 OptimizationPranathi PraveenNo ratings yet

- MCU ArchitectureDocument232 pagesMCU Architecturesachinshetty001No ratings yet

- Aca (15CS72) Module-3Document27 pagesAca (15CS72) Module-3Yogesh KumarNo ratings yet

- Sistem Memori Komputer: L3. Cache Amil Ahmad IlhamDocument19 pagesSistem Memori Komputer: L3. Cache Amil Ahmad IlhamKHairul Qalam HakimNo ratings yet

- Aos - W05Document22 pagesAos - W05GES ISLAMIA PATTOKINo ratings yet

- Unit 1 Part 2 (Chapter 4) Cache MemoryDocument53 pagesUnit 1 Part 2 (Chapter 4) Cache MemoryNITHIYA PAUL 1847244No ratings yet

- Module 5.3Document39 pagesModule 5.3Asha DurafeNo ratings yet

- William Stallings Computer Organization and Architecture 8th Edition Cache MemoryDocument71 pagesWilliam Stallings Computer Organization and Architecture 8th Edition Cache MemoryRudi GunawanNo ratings yet

- Addressing Modes: 4.1. Interpreting Memory AddressesDocument20 pagesAddressing Modes: 4.1. Interpreting Memory AddressesChina KcvrNo ratings yet

- CHAPTER 1.2 Elements of Computer System and Categories of Computer PeripheralsDocument23 pagesCHAPTER 1.2 Elements of Computer System and Categories of Computer PeripheralsCharity Rider TitomacoytvNo ratings yet

- Features: 256Kb Bytewide FRAM MemoryDocument12 pagesFeatures: 256Kb Bytewide FRAM MemoryCarlos MejíaNo ratings yet

- Anatomy of A Program in Memory - Gustavo DuarteDocument41 pagesAnatomy of A Program in Memory - Gustavo DuarteRigs JuarezNo ratings yet

- Electronics: Challenges and Applications of Emerging Nonvolatile Memory DevicesDocument24 pagesElectronics: Challenges and Applications of Emerging Nonvolatile Memory DevicesGio SssNo ratings yet

- TAPA Tutorial 1119163.14Document124 pagesTAPA Tutorial 1119163.14manojsingh474No ratings yet

- EmbeddedDocument10 pagesEmbeddedSarthak BhattacharjeeNo ratings yet

- AnswersDocument10 pagesAnswersSello HlabeliNo ratings yet

- CS6303 Computer Architecture 2Document56 pagesCS6303 Computer Architecture 2Angela KasekeNo ratings yet

- Full Form NotesDocument24 pagesFull Form NotesManzoor ElahiNo ratings yet

- Types of Cache MissesDocument30 pagesTypes of Cache MissesTran Viet Le QuangNo ratings yet

- Lecture 01b - Introduction To OS (MN404) 2020Document44 pagesLecture 01b - Introduction To OS (MN404) 2020Tauha NadeemNo ratings yet

- Solution For Chapter 4Document26 pagesSolution For Chapter 4thanhtung_bk52100% (3)

- 2017 Nov Accessories Price Book 20171119Document64 pages2017 Nov Accessories Price Book 20171119wirelesssoulNo ratings yet

- First Generation: Vacuum Tubes (1940-1956) : A UNIVAC Computer at The Census BureauDocument17 pagesFirst Generation: Vacuum Tubes (1940-1956) : A UNIVAC Computer at The Census BureauanamNo ratings yet

- Correct Answer: (B)Document41 pagesCorrect Answer: (B)Tính HuỳnhNo ratings yet

- Intel Doc PDFDocument3,284 pagesIntel Doc PDFRohit PandeyNo ratings yet

- Project SRAM - Design Review II: University of VirginiaDocument27 pagesProject SRAM - Design Review II: University of VirginiaParth RamanujNo ratings yet

- P89C51RB2/P89C51RC2/P89C51RD2: 80C51 8-Bit Flash Microcontroller FamilyDocument52 pagesP89C51RB2/P89C51RC2/P89C51RD2: 80C51 8-Bit Flash Microcontroller FamilyÁrpád HimpliNo ratings yet

- Ug QPP Programmer 19 3 683039 705024Document58 pagesUg QPP Programmer 19 3 683039 705024ATHIRA G SNo ratings yet

- Sunbeam OS Day4 MCQ'sDocument13 pagesSunbeam OS Day4 MCQ'sYash KuncolienkerNo ratings yet

- Class IX Computer NotesDocument39 pagesClass IX Computer NotesarsalanNo ratings yet

- FlashlistDocument135 pagesFlashlistfarouk keddarNo ratings yet

- Dwnload Full Operating Systems Internals and Design Principles 7th Edition Stallings Test Bank PDFDocument36 pagesDwnload Full Operating Systems Internals and Design Principles 7th Edition Stallings Test Bank PDFaranasopal218889% (9)

- Advance Computer Architecture Homework 2 SolutionDocument8 pagesAdvance Computer Architecture Homework 2 SolutionJahanzaib AwanNo ratings yet

- Qualified Vendors List (QVL)Document2 pagesQualified Vendors List (QVL)Mai PhaNo ratings yet

- Described in Task 3. Which Upgrades And/or Options Would Improve These Aspects of This Computer?Document6 pagesDescribed in Task 3. Which Upgrades And/or Options Would Improve These Aspects of This Computer?Regil Tryadi Adhiwidjaya100% (1)

- VM Page Replacement: Hank LevyDocument21 pagesVM Page Replacement: Hank LevyJunaid AkramNo ratings yet