Professional Documents

Culture Documents

Adobe Scan 25 May 2023

Uploaded by

ENTERTAINMENTOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Adobe Scan 25 May 2023

Uploaded by

ENTERTAINMENTCopyright:

Available Formats

ll,\ l \ ..

- CLK O

tH IN

'( )I l N'I 1m n AT I', O

H\ ti•FF I~

o _ ,. o UT O

~I-

F ......

VI -

t, P ~- M RF/\ 1)/ ;_, . - CL K I

\\' ~ "" rt1 ( 'OI JNTl'.I< UA'IE I

\

\\' I{ 1l'E ~ I

\ I OU lt' ~ ,,..-.- ~ l - --r- -~ OlJT l

-s- --

( , .-. .-- -,

('TRL.

CLK2

\\/ORD

GATE 2

REG

OU T2

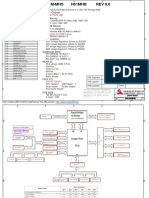

Figure Arcltitecture of 8253/8254

,:hitecture:

e prog rammable timer device 8253 contains three independ

ent 16-b it

, each with a maximum count rate of 2.6Mhz. It is thus possible to gene

rate

cpendent delays or maintain three independent counters simultaneous

ly.

l!ee counters may he independently controlled by

programming the three

·ommand word registers.

1ta Bus Buffer): The 8-bit , bidirectional data bus buffer interfac

es internal

8253 to microprocessor system bus. Data is transmitted or received

by the

•n the execution of IN or OUT instruction.

(Re~d/Write Logic): Read/write logic controls the direction of the

data

inding upon whether it is a read or a write operation It ma b

. reads data whiie OUT instruction Writes

ion data to· ., __ _Y

. • e noted that

in o . t)•1•2.· .I'

~ l) e r a tl o n . but th

h

e

e

y

th

a

re

rc

e

·

id

c o u n te rs a v ailable in sz 53

a r e .

in d c p e n d c n t r, f c--~...., .,

,-r e ~ a b l e i e n ti c a l to each other in o

, c o w n c rg ·

a n iz a ti. o n . T h

o u n te r s , a b le to e s e art: all\-, '' i

o p e ra te either in . a

C. oatt~l W ord c D o r ·

in h e x a d·cc im at- I, l"r,,

that can b e . e dRegister: The mode control word •

reg .

is te r c o n ta

u s for writin .

in s th e in fottt, ,

g o r re a d in g th Jue in to o r

e c o u n t va f r o m th

c rC1! ~

c o u n t register ~,.

U$ing the O U T a n d IN in structions.

Note-: T h e s p e c ia li ty o f the 8253

without dis tu

c o u n te rs is that the y c a n

rb in g th e clo c b e e a s il y r ead on .

k in p u t to the counter. T .

h is f a c il ty

ly~. reading o f c is c a ll e d as " u~ ,

oun ters.

1.8.3 Pin Description Of 8253/825 4:

D7 1 40 V ee

D6 2 39 WR

D5 3

38

-

RD

D4 4

37 cs

D3 5

36 Al

D2 6

8253 / 8254 35 AO

DI 7

34 CLK2

DO 8

CLKO 33 OCT2

9

ouro 10

32 GATE2

GATEO 31

lI CLK l

G\D 30

12 G.A.TE l

'"' Q

- ,J r\ 10 • .,. _

l I •

1

,,,.,

, ;..,-, ·

• •

ed inte rna lly ror 8ddt ess ing

the ~u.i drc ss mp

~ , , , 111,, •·l t'<'

•

ut p111s and ure req utr ,

f l"'"~ '

~•

1 ,,,1 rd rl.·11isccrs nnd the thr ee cou nte r reg iste

. •CS ' tin e

~~

_,,,"if ' :. ~•~

rs. A low on

n.

tti<" ~- • •

Nl) opc rut ion wil l be pe rfo rm ed by

825 3 till it is ena ble d. Ta b e '

~ ~ 1 ...,..t~f c)p crn tion

for vnr iou s con tro l inp uts .

~--

,,,,... r • ~ '"'

Tab le Ba sic ope rat ion of 825 3/8 254

'

--- -

{""S RD

I

-WR

0

Al

0

AO Sel ect ed op era tio n

- I

tl 0 Write counter 0

1 0 0

I o 1 Write cou nte r 1

- 0 1 0 1 0 Write cou nte r 2

- -

-

0 1 0 I I Write con tro l wo rd

0 0 1 0 0 Re ad cou nte r 0

0 0 1 0 1 Re ad cou nte r 1

0 . 0 l 1 0 Re ad co un ter 2

0 0 l l 1 No op era tio n (tr ist ate d)

0 I 1 X X No op era tio n (tr ist ate d)

I X X X X Di sab led (tr ist ate d) •

I

A control wo rd reg ist er ac ce pts the

8-b it co ntr ol wo rd wr itt en by th e

nicroprocessor and sto res it for controlling

the con1plete op era tio n of the specific

>unter. It may be no ted tha t, the co ntr

ol word register can only be wdttcn

nnd

onot be read as it is obvious from Table.

The CLK, GATE. and ()\ rr pin s l\tT

ilable for each of the three timer ch an ne ls.

" ~:\ - l - •ocon

~ ~.( j,·

+

}."'l;~' \ 't). ''\

'- "' ''' .\' ',,• \ \. '' ' \ \

""--

J N"OH1 ~l.U(I Fnn~

'~ ~"'••' it"t"' N'1 _a. . ,. . . . -'!i~.,_ _,,_ ti

_- o

-- --n-- -- - -- -- - -

• \~ .,, I •\ lli--d1

, , ,,~ \ \ : '~ ' \ .1

,,,nH1 C\1tod lP :sys

ru c ti

te

o

11

n

1

al

d

th re e s ta te data b

a ta b u s . Us ll ~

, '\ ( H'"- O : (" 'lo

\ t ~ \' ,, \ _,___.... ~. o k In p u t o f C ou t~ n

·,

~ )\ l'TP\ l' I' 0 .

' '·\ \ \' l

\,\ \ ' \

: O u tp u t o f C o unter o. ~

\

rl

, L·\ ~ (J

__ a te In p u t o f C o u nter 0. ~

\; ' I I I 1

1 \\ __..,--.

\RI )\JND : P o w er

\ :\ ' '

' \ \ 1

-, )\VBR : A SY. ----- S u pp ly Co nnection--.......,

\\ \ '

I

t

·" r -• -- ,

,

.,,

'

◄:

11

.WRITE coNT R

p

~

o

L

w e r su p ply co nnecti-;----,

. ; '\ \ : T h is inp u t is l o w ~

\\ '\ , cPU write op _er_a_u_ o_ n_ .-

=r= "''"-Rl - - - ---

l, P

~~~

. :~~~

I ,., I

i AD coN1'R

CPU rtlnd operttl

~ L

lo n

:T

.

h is inp ut is IOw during

K~ - -

Cl llP SELECT : A lo

l' ~ it \ w on th is in pu t enables

tilt' S25 4 to respo n d to R D an d W R signals.

JU) and W R nre ign o re d o th erwise.

A DDRFSS : Used

:\ t ~ r\ () I ! O· ,) I to s ele c t o ne of th e three

l'o11n1ers or the Con

tro l W ord R e gis te r for read

You might also like

- Gold City - The Best of Gold City Quartet (Songbook)Document49 pagesGold City - The Best of Gold City Quartet (Songbook)Pepe Gallo91% (11)

- Structurally Deficient Bridges in MassachusettsDocument860 pagesStructurally Deficient Bridges in MassachusettsBoston 25 DeskNo ratings yet

- German in 32 - LessonsDocument135 pagesGerman in 32 - LessonsvalterNo ratings yet

- International Society for Rock Mechanics: List of Members 1980From EverandInternational Society for Rock Mechanics: List of Members 1980Rating: 3.5 out of 5 stars3.5/5 (2)

- C26a2 COmpal LA-8941PDocument45 pagesC26a2 COmpal LA-8941PAbi AtaNo ratings yet

- Third Imperium Issue 4Document20 pagesThird Imperium Issue 4atpollard50% (2)

- NACA P51 Intermediate Wing Section DataDocument19 pagesNACA P51 Intermediate Wing Section Dataavialogs100% (1)

- Rechtschaffen Kales - A Manual of Standardized Terminology Techniques and Scoring System For Sleep Stages of Human SubjectsDocument59 pagesRechtschaffen Kales - A Manual of Standardized Terminology Techniques and Scoring System For Sleep Stages of Human Subjectspower199680% (5)

- Schematics Ecs H61H2 AM V1.1.OK - 2Document46 pagesSchematics Ecs H61H2 AM V1.1.OK - 2anh_sao_dem_92No ratings yet

- MSI - MS-7680 - H61 - Socket 1155Document34 pagesMSI - MS-7680 - H61 - Socket 1155andrealves-tecNo ratings yet

- Gener : AcrsDocument2 pagesGener : AcrsEldhoThomasNo ratings yet

- Boericke Bell DefDocument9 pagesBoericke Bell DefSUJEET A VAGHANINo ratings yet

- Ag SG Catalogues KL IIDocument6 pagesAg SG Catalogues KL IIkhamsone pengmanivongNo ratings yet

- Requl Tio Requl Tio:) /:i I ( /) /:i I (Document34 pagesRequl Tio Requl Tio:) /:i I ( /) /:i I (prachatNo ratings yet

- Anna University MaterialDocument7 pagesAnna University MaterialVimal MNo ratings yet

- Solid State Viva QuestionsDocument7 pagesSolid State Viva QuestionsAnanya SNo ratings yet

- gr11 Chem Record First HalfDocument16 pagesgr11 Chem Record First HalfNIGHNA BHARWANI 9266No ratings yet

- MTN 1382Document1 pageMTN 1382Zion SamuelNo ratings yet

- Cross Talk MeasuringDocument8 pagesCross Talk Measuringprashant PujariNo ratings yet

- Adobe Scan 01 Agt 2021Document3 pagesAdobe Scan 01 Agt 2021Siti Mey WulandariNo ratings yet

- Clansman Installation ManualDocument21 pagesClansman Installation ManualSteve MillerNo ratings yet

- Alllahfi /: Alfana 114/ibb9 / L OJ.ADocument2 pagesAlllahfi /: Alfana 114/ibb9 / L OJ.AAlfana AlkahfiNo ratings yet

- PlantDocument5 pagesPlantKinjalNo ratings yet

- Strategic ManagementDocument7 pagesStrategic ManagementHrutik BhandareNo ratings yet

- Mayans 122Document11 pagesMayans 122OnenessNo ratings yet

- Adobe Scan 24 Nov 2022Document2 pagesAdobe Scan 24 Nov 2022esrayani1703No ratings yet

- Accounting 2005 ExamDocument10 pagesAccounting 2005 ExamMera SamirNo ratings yet

- Optical Fiber Analog and Digital LinksDocument4 pagesOptical Fiber Analog and Digital LinksdarshanwithmomNo ratings yet

- Indicator Norme Deviz Terasament Ts VolDocument82 pagesIndicator Norme Deviz Terasament Ts VolCostin MihaiNo ratings yet

- Follows:: Origins. D T NatDocument16 pagesFollows:: Origins. D T NatBarani Kumar NNo ratings yet

- Flow Contol NotesDocument17 pagesFlow Contol NotesIsha KeshavNo ratings yet

- LTC Surity FormDocument2 pagesLTC Surity FormjyothiprakashNo ratings yet

- Scan 6 Jun 2020Document1 pageScan 6 Jun 2020praveensmanusNo ratings yet

- MS 22 Part - 2Document190 pagesMS 22 Part - 2Anh QuanNo ratings yet

- Ulp ms2Document23 pagesUlp ms2DeepakNo ratings yet

- P'1Jljra: FytenoulDocument26 pagesP'1Jljra: FytenoulAnita GajbhiyeNo ratings yet

- Zxperirnel?ter by Suzanne EL,: R.'.L - ?FR-.?Document6 pagesZxperirnel?ter by Suzanne EL,: R.'.L - ?FR-.?Bia&Eva SURPRISE SONGSNo ratings yet

- Tests 1Document6 pagesTests 1Dolly NarisNo ratings yet

- Assignment - 2 (EC502)Document15 pagesAssignment - 2 (EC502)Ritesh GhoshNo ratings yet

- Cxhznos: It, L!Iec Dmntes D JDocument7 pagesCxhznos: It, L!Iec Dmntes D JyosvaniNo ratings yet

- Adobe Scan 06 May 2023Document10 pagesAdobe Scan 06 May 2023vasu dha5058No ratings yet

- Reverse Recovery Characteristics of Power DiodeDocument3 pagesReverse Recovery Characteristics of Power Diodegopal sapkotaNo ratings yet

- Carino: Chapter 1 - Project ManagementDocument19 pagesCarino: Chapter 1 - Project ManagementDeasty JesicaNo ratings yet

- DS - Practical - 3Document16 pagesDS - Practical - 3Soha KULKARNINo ratings yet

- C.S.E 8,12,2021Document11 pagesC.S.E 8,12,2021SarfrazNo ratings yet

- Mayans 134Document7 pagesMayans 134OnenessNo ratings yet

- Mechanical Principles (1st CH)Document8 pagesMechanical Principles (1st CH)sanchitapanda0401No ratings yet

- L L I L / LDocument18 pagesL L I L / LseoversightNo ratings yet

- Dancing in The Rain NotesDocument7 pagesDancing in The Rain NotesHABEEB ANSARI ANSARINo ratings yet

- Copii CazareDocument1 pageCopii CazareTibuZ PNo ratings yet

- Is 1862Document4 pagesIs 1862mangesh sandavNo ratings yet

- 1 88-Estt (D)Document2 pages1 88-Estt (D)rvktirumalaiNo ratings yet

- CopperDocument14 pagesCopperI m legend kcNo ratings yet

- Runway LightingDocument12 pagesRunway LightingBalaji RNo ratings yet

- José Benedito - AnotaçõesDocument73 pagesJosé Benedito - Anotaçõessagrada engenhariaNo ratings yet

- Aste Management: L, Include Tuu Ce Ap EaDocument4 pagesAste Management: L, Include Tuu Ce Ap EaAnshikaNo ratings yet

- Unit 1 O XTR Pra Tice: - TourDocument2 pagesUnit 1 O XTR Pra Tice: - Tourdane gaoNo ratings yet

- Unit 2 ContouringDocument15 pagesUnit 2 ContouringgomatesgNo ratings yet

- Durga Puja For Beginners PDFDocument34 pagesDurga Puja For Beginners PDFAxel Valenzuela Bylander100% (1)

- Assignment 3Document7 pagesAssignment 3Sai prasanna BodduNo ratings yet

- Adobe Scan 01 Aug 2023Document13 pagesAdobe Scan 01 Aug 2023dhyanadhyana829No ratings yet

- 1-10 Counting of Training Period For The Purpose of Drawing Increments - No. 60-6-92-SPB-I Dt. 02.09.1993Document3 pages1-10 Counting of Training Period For The Purpose of Drawing Increments - No. 60-6-92-SPB-I Dt. 02.09.1993Pawan Kumar100% (1)

- Baher Connect 4 2022Document256 pagesBaher Connect 4 2022azze sebihiNo ratings yet

- Class 9th Geography? ? Short QADocument3 pagesClass 9th Geography? ? Short QAFull in FunNo ratings yet

- Mainboard Ms - 7046M1Document30 pagesMainboard Ms - 7046M1Ho Thanh BinhNo ratings yet

- Quanta SWH R1a Schematics-100Document42 pagesQuanta SWH R1a Schematics-100Andres BogNo ratings yet

- AMD Chipset RS690C & SB600 Power On SequenceDocument1 pageAMD Chipset RS690C & SB600 Power On SequenceEduinMaracuchoFernandezChaparroNo ratings yet

- Biostar H61MHBDocument45 pagesBiostar H61MHBAlex Manzhos100% (1)

- Dell Inspiron 17R N7110 Quanta R03 - V03 Ver 03 Rev 2A СхемаDocument42 pagesDell Inspiron 17R N7110 Quanta R03 - V03 Ver 03 Rev 2A СхемаTaras KrasinNo ratings yet

- ChpsdevsDocument3 pagesChpsdevstomoyo2009No ratings yet

- Tabelapch IntelDocument4 pagesTabelapch IntelEletrônica Goiano100% (1)

- Release NoteDocument9 pagesRelease NoteMark Laurence CatahanNo ratings yet

- Schematic Msi h61m-p31 Ms-7788 Rev 1.0Document33 pagesSchematic Msi h61m-p31 Ms-7788 Rev 1.0Newdin67% (9)

- MSI - 86b81 - MS-7037Document30 pagesMSI - 86b81 - MS-7037Débo OrellanoNo ratings yet

- Intel ChipsetDocument159 pagesIntel Chipsetzaki marufanNo ratings yet

- Ecs q67h2 Ad q65h2 Ad h67h2 AdDocument44 pagesEcs q67h2 Ad q65h2 Ad h67h2 AdDinuth DulsanduNo ratings yet

- Intel ChipsetDocument58 pagesIntel Chipsetanon_206764798No ratings yet

- Intel ChipsetDocument143 pagesIntel Chipseth2149752No ratings yet

- Manual Mother Board Ecs 61Document42 pagesManual Mother Board Ecs 61ajha6775% (4)

- DP Video Intel 15036 DriversDocument59 pagesDP Video Intel 15036 DriversJuan Carlos Gonzalez LNo ratings yet

- B75H2-AD: Elitegroup Computer Systems Elitegroup Computer Systems Elitegroup Computer SystemsDocument48 pagesB75H2-AD: Elitegroup Computer Systems Elitegroup Computer Systems Elitegroup Computer SystemsMoriel EverNo ratings yet

- DP Video Intel-XP 15101 DriversDocument18 pagesDP Video Intel-XP 15101 DriversRaphael Fagundes LopesNo ratings yet

- (QY/+XURQ5LYHU:KLVWOHU3UR ''5%/2&.',$ 5$0: Sandy Bridge Intel ProcessorDocument42 pages(QY/+XURQ5LYHU:KLVWOHU3UR ''5%/2&.',$ 5$0: Sandy Bridge Intel ProcessorInfo ByteNo ratings yet

- H61H2-LM3: ECS ConfidentialDocument39 pagesH61H2-LM3: ECS Confidentialanh_sao_dem_920% (1)

- ECS H61H2 CM2 Rev10Document40 pagesECS H61H2 CM2 Rev10anh_sao_dem_92No ratings yet

- B75H2-AD: Trung Tâm Máy Tính Av 0904701445-0968739980Document48 pagesB75H2-AD: Trung Tâm Máy Tính Av 0904701445-0968739980Xuân TrườngNo ratings yet

- Intel ChipsetDocument115 pagesIntel ChipsetO. C.No ratings yet

- Asus K46CDocument62 pagesAsus K46CBintangCompNo ratings yet

- Intel Chipset Path DriversDocument125 pagesIntel Chipset Path DriversDeepak SinghNo ratings yet

- IntelChipset - Log - NotepadDocument141 pagesIntelChipset - Log - NotepadJaycie CruzNo ratings yet