0% found this document useful (0 votes)

108 views46 pagesMOS Transistor Analysis & Design

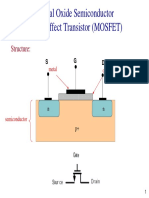

The document discusses the structure and operation of MOS transistors. It describes the key components of the MOS structure including the metal gate, insulating oxide layer, and semiconductor substrate. It explains how applying different biases to the gate results in accumulation, depletion, and inversion at the surface of the semiconductor. Threshold voltage is defined as the minimum gate voltage needed to induce inversion and form a conducting channel. Circuit symbols are provided for enhancement-mode n-channel and p-channel MOSFETs.

Uploaded by

divyansh kaliaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

108 views46 pagesMOS Transistor Analysis & Design

The document discusses the structure and operation of MOS transistors. It describes the key components of the MOS structure including the metal gate, insulating oxide layer, and semiconductor substrate. It explains how applying different biases to the gate results in accumulation, depletion, and inversion at the surface of the semiconductor. Threshold voltage is defined as the minimum gate voltage needed to induce inversion and form a conducting channel. Circuit symbols are provided for enhancement-mode n-channel and p-channel MOSFETs.

Uploaded by

divyansh kaliaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd