Professional Documents

Culture Documents

Week 13

Week 13

Uploaded by

Sandhya0 ratings0% found this document useful (0 votes)

6 views24 pagesIDDQ testing involves measuring the quiescent or idle current (IDDQ) of an integrated circuit. Small defects that cause current leaks can be detected this way. The document discusses the motivation for IDDQ testing and how it can find faults like bridging faults and floating gate defects. It also covers limitations like increased leakage currents in newer technologies making the IDDQ threshold harder to determine. Methods to improve IDDQ testing like delta IDDQ testing and building current sensors directly into chips are presented.

Original Description:

Original Title

Week_13

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentIDDQ testing involves measuring the quiescent or idle current (IDDQ) of an integrated circuit. Small defects that cause current leaks can be detected this way. The document discusses the motivation for IDDQ testing and how it can find faults like bridging faults and floating gate defects. It also covers limitations like increased leakage currents in newer technologies making the IDDQ threshold harder to determine. Methods to improve IDDQ testing like delta IDDQ testing and building current sensors directly into chips are presented.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views24 pagesWeek 13

Week 13

Uploaded by

SandhyaIDDQ testing involves measuring the quiescent or idle current (IDDQ) of an integrated circuit. Small defects that cause current leaks can be detected this way. The document discusses the motivation for IDDQ testing and how it can find faults like bridging faults and floating gate defects. It also covers limitations like increased leakage currents in newer technologies making the IDDQ threshold harder to determine. Methods to improve IDDQ testing like delta IDDQ testing and building current sensors directly into chips are presented.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 24

IDDQ Testing

Ganesh C. Patil

Tuesday, November 7, 2023

1

Motivation

Early 1990’s – Fabrication Line had 50 to 1000

defects per million (dpm) chips

IBM wants to get 3.4 defects per million (dpm) chips

Conventional way to reduce defects:

Increasing test fault coverage

Increasing burn-in coverage

Increase Electro-Static Damage awareness

New way to reduce defects:

IDDQ Testing – also useful for Failure Effect

Analysis

Tuesday, November 7, 2023

2

Basic Principle of IDDQ Testing

Measure IDDQ current through Vss bus

Tuesday, November 7, 2023

3

Faults Detected by IDDQ Tests

Tuesday, November 7, 2023

4

Stuck-at Faults Detected by IDDQ Tests

Bridging faults with stuck-at fault behavior

Levi – Bridging of a logic node to VDD or VSS –

few of these

Transistor gate oxide short

Floating MOSFET gate defects – do not

fully turn off transistor

Tuesday, November 7, 2023

5

NAND Open Circuit Defect – Floating gate

Tuesday, November 7, 2023

6

Floating Gate Defects

Small break in logic gate inputs (100 – 200

Angstroms) lets wires couple by electron

tunneling

Delay fault and IDDQ fault

Large open results in stuck-at fault – not

detectable by IDDQ test

If Vtn < Vfn < VDD - | Vtp | then detectable by

IDDQ test

Tuesday, November 7, 2023

7

Multiple IDDQ Fault Example

Tuesday, November 7, 2023

8

Capacitive Coupling of Floating Gates

Cpb – capacitance from poly to

bulk

Cmp – overlapped metal wire to

poly

Floating gate voltage depends

on capacitances and node

voltages

If nFET and pFET get enough

gate voltage to turn them on,

then IDDQ test detects this defect

Tuesday, November 7, 2023

9

Leakage Faults

Gate oxide shorts cause leaks between gate &

source or gate & drain

Mao and Gulati leakage fault model:

Leakage path flags: fGS, fGD, fSD, fBS, fBD, fBG

G = gate, S = source, D = drain, B = bulk

Assume that short does not change logic values

Tuesday, November 7, 2023

10

Weak Faults

nFET passes logic 1 as 5 V – Vtn

pFET passes logic 0 as 0 V + |Vtp|

Weak fault – one device in C-switch does not

turn on

Causes logic value degradation in C-switch

Tuesday, November 7, 2023

11

Transistor Stuck-Closed Faults

Due to gate oxide

short (GOS)

k = distance of short

from drain

Rs = short resistance

IDDQ2 current results

show 3 or 4 orders of

magnitude elevation

Tuesday, November 7, 2023

12

Gate Oxide Short

Tuesday, November 7, 2023

13

Leakage Fault Table

k = # component I/O pins

n = # component transistors

m = 2k (# of input / output combinations)

m x n matrix M represents the table

Each logic state – 1 matrix row

Entry mi j = octal leakage fault information

Flags fBG fBD fBS fSD fGD fGS

Sub-entry mi j = 1 if leakage fault detected

Tuesday, November 7, 2023

14

Example Leakage Fault Table

Flags fBG fBD fBS fSD fGD fGS

Tuesday, November 7, 2023

15

Instrumentation Problems

Need to measure < 1 mA current at

clock > 10 kHz

Off-chip IDDQ measurements degraded

Pulse width of CMOS IC transient current

Impedance loading of tester probe

Current leakages in tester

High noise of tester load board

Much slower rate of current

measurement than voltage measurement

Tuesday, November 7, 2023

16

Limitations of IDDQ Testing

Sub-micron technologies have increased

leakage currents

Transistor sub-threshold conduction

Harder to find IDDQ threshold separating good &

bad chips

IDDQ tests work:

When average defect-induced current greater

than average good IC current

Small variation in IDDQ over test sequence &

between chips

Tuesday, November 7, 2023

17

Delta IDDQ Testing -- Thibeault

Use derivative of IDDQ at test vector as

current signature

D IDDQ (i) = IDDQ (i) – IDDQ (i – 1)

Leads to a narrower histogram

Eliminates variation between chips and

between wafers

P – probability of false test decisions

Tuesday, November 7, 2023

18

IDDQ Built-in Current Testing – Maly

and Nigh

Build current sensor into ground bus of

device-under-test

Voltage drop device & comparator

Compares virtual ground VGND with Vref at end

of each clock – VGND > Vref only in bad circuits

Activates circuit breaker when bad device

found

Tuesday, November 7, 2023

19

Conceptual BIC Sensor

Tuesday, November 7, 2023

20

CMOS BIC Sensor

Tuesday, November 7, 2023

21

Setting Optimal # Transistors in Block

Must partition chip into functional units, each with

its own BIC

Too large a unit – combined leakage currents

erroneously trigger BIC sensor

Idefmin – smallest defect current

Inoisemax – maximum noise-related peak supply

current

Minimum area sensor design at Idefmin and IDDQ

intersection

Nmax – maximum # transistors in 1 BIC unit

Tuesday, November 7, 2023

22

Graph for Choosing Nmax

Tuesday, November 7, 2023

23

Thank you !!!

Tuesday, November 7, 2023

24

You might also like

- ART Tube MP ModificationDocument14 pagesART Tube MP Modificationtitov33No ratings yet

- Fiber Characterization TrainingDocument40 pagesFiber Characterization TrainingTetsusaigaNo ratings yet

- Drg. & GTP - R1 - 11 KV HG Fuse - DiskitDocument4 pagesDrg. & GTP - R1 - 11 KV HG Fuse - DiskitAnand ShekharNo ratings yet

- CMIT 796 ELE 15.17!10!0010 - 0 - Data Sheet For PowerDocument4 pagesCMIT 796 ELE 15.17!10!0010 - 0 - Data Sheet For PowerELE FutureWillNo ratings yet

- Wireless Communications Design Handbook: Interference into Circuits: Aspects of Noise, Interference, and Environmental ConcernsFrom EverandWireless Communications Design Handbook: Interference into Circuits: Aspects of Noise, Interference, and Environmental ConcernsNo ratings yet

- Chapter 7 Mosfets in Ics - Scaling, Leakage, and Other TopicsDocument43 pagesChapter 7 Mosfets in Ics - Scaling, Leakage, and Other Topicsmorcov19No ratings yet

- Physical Verification1Document163 pagesPhysical Verification1Praveen Kumar100% (1)

- Scaling Factors and Scaling ParametersDocument22 pagesScaling Factors and Scaling Parametersvirajitha159475% (4)

- Optical Metro 5100:5200 Network Planning and Link Engineering, Part 2 of 3Document286 pagesOptical Metro 5100:5200 Network Planning and Link Engineering, Part 2 of 3Bichon OttawaNo ratings yet

- Passive Optical Networks: Principles and PracticeFrom EverandPassive Optical Networks: Principles and PracticeRating: 2.5 out of 5 stars2.5/5 (2)

- K109909811S19Document4 pagesK109909811S19yashrahane04No ratings yet

- Series 117: MicronoteDocument1 pageSeries 117: Micronotelangtu74No ratings yet

- Nepal Electricity AthorityDocument22 pagesNepal Electricity AthorityShubham BaderiyaNo ratings yet

- Fin Irjmets1648712677Document5 pagesFin Irjmets1648712677yashrahane04No ratings yet

- Chenming Hu ch7 SlidesDocument43 pagesChenming Hu ch7 SlideseleenaamohapatraNo ratings yet

- Adum 7510Document12 pagesAdum 7510Med SamiNo ratings yet

- Wireless: CCNA Exploration Semester 3Document39 pagesWireless: CCNA Exploration Semester 3hem777No ratings yet

- Underground Cable Fault Detection SystemDocument4 pagesUnderground Cable Fault Detection SystemJh wNo ratings yet

- Deabb 4094 enDocument25 pagesDeabb 4094 enGinursamadNo ratings yet

- Underground Cable Fault Detection Device Using MicrocontrollerDocument6 pagesUnderground Cable Fault Detection Device Using MicrocontrollerIJRASETPublicationsNo ratings yet

- Drg. & GTP - R1 - 36 KV HG Fuse - DiskitDocument4 pagesDrg. & GTP - R1 - 36 KV HG Fuse - DiskitAnand ShekharNo ratings yet

- Project Proposal Format Edited 3Document15 pagesProject Proposal Format Edited 3Tolesa ShoreNo ratings yet

- Patch 4Document4 pagesPatch 4Maged BesharaNo ratings yet

- Non-Conventional Low Power Circuit Design TechniquesDocument9 pagesNon-Conventional Low Power Circuit Design Techniquesijire publicationNo ratings yet

- Design and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueDocument7 pagesDesign and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueGRD JournalsNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument66 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- Formulario Diligenciamiento - DeADocument3 pagesFormulario Diligenciamiento - DeAKdash Kdash SxgaNo ratings yet

- Arduino Based Underground Cable Fault de PDFDocument5 pagesArduino Based Underground Cable Fault de PDFRana AbrarNo ratings yet

- Arduino Based Underground Cable Fault DetectionDocument5 pagesArduino Based Underground Cable Fault DetectionBikila DesalegnNo ratings yet

- Week 14Document48 pagesWeek 14SandhyaNo ratings yet

- E3 238 Analog VLSI Circuits: Lecture 2: Review of Device CharacteristicsDocument11 pagesE3 238 Analog VLSI Circuits: Lecture 2: Review of Device CharacteristicsaxiomNo ratings yet

- Chp1-2 Print BookDocument40 pagesChp1-2 Print Bookbalaji_gawalwad9857No ratings yet

- R2 PDFDocument3 pagesR2 PDFpubg EdictsNo ratings yet

- Consultant RTU Weekly Site Report Week 50Document3 pagesConsultant RTU Weekly Site Report Week 50tayyab zafarNo ratings yet

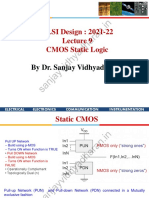

- Lec 9 CMOS Static LogicDocument19 pagesLec 9 CMOS Static LogicMainak TarafdarNo ratings yet

- DS-NG-6460-002-002 Test Form For SAS Fiber Obtic Cables Commissioning Rev01Document3 pagesDS-NG-6460-002-002 Test Form For SAS Fiber Obtic Cables Commissioning Rev01Makesh IndhuNo ratings yet

- SiC Power Devices On QUASIC and SiCOI Smart-CutDocument7 pagesSiC Power Devices On QUASIC and SiCOI Smart-CutTeststeNo ratings yet

- SFP 1g Bx10u 1310nm 1490nm 10km Bidi Fiber Transceiver 151108 T03Document7 pagesSFP 1g Bx10u 1310nm 1490nm 10km Bidi Fiber Transceiver 151108 T03GLsun MallNo ratings yet

- PWT 2007 - 2598Document8 pagesPWT 2007 - 2598Jan MinkNo ratings yet

- Profibus RS485 WiringDocument3 pagesProfibus RS485 Wiringdjeff71No ratings yet

- TESTING of Integrated CircuitsDocument37 pagesTESTING of Integrated CircuitsEUGENNo ratings yet

- Dig-Isol-ADuM7640 7641 7642 7643Document20 pagesDig-Isol-ADuM7640 7641 7642 7643Lulu Sweet ThingNo ratings yet

- Development of Fault Distance Locator For UndergroDocument13 pagesDevelopment of Fault Distance Locator For UndergroCristian GalvezNo ratings yet

- Fault Detection in Transmission Line Using Arduino UnoDocument3 pagesFault Detection in Transmission Line Using Arduino UnoJanani KanipakamNo ratings yet

- Unit 1-VlsiDocument34 pagesUnit 1-Vlsikingzyper19No ratings yet

- Wireless Bearing Based On PON Network - Telecom Review Asia PacificDocument7 pagesWireless Bearing Based On PON Network - Telecom Review Asia Pacificwin Zaw TheinNo ratings yet

- An Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI TechnologyDocument4 pagesAn Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI Technologyapi-19668941No ratings yet

- CBC78T-DS-43 Product SpecificationsDocument5 pagesCBC78T-DS-43 Product SpecificationsJulián GiménezNo ratings yet

- CBC78T DS 43 Product SpecificationsDocument5 pagesCBC78T DS 43 Product SpecificationsJulián GiménezNo ratings yet

- Gate Level DesignDocument34 pagesGate Level DesignYOGESWARI TOLIANo ratings yet

- A Report: Verilog-A Implementation of The EKV v2.6 Long and Short Channel MOSFET ModelsDocument43 pagesA Report: Verilog-A Implementation of The EKV v2.6 Long and Short Channel MOSFET ModelsDilan ByteNo ratings yet

- Underground Cable Fault Detection and Location Finding: XXXXXXX 1XxxxxxDocument38 pagesUnderground Cable Fault Detection and Location Finding: XXXXXXX 1Xxxxxxshaik shaNo ratings yet

- Fast and Easily Implementable Detection CircuitsDocument9 pagesFast and Easily Implementable Detection CircuitsPablo Henrique Seibert JahnoNo ratings yet

- Finisar ftlx6672mcc 10g DWDM 40km Multi-Rate T-SFP Optical Transceiver Product Spec Reva02Document15 pagesFinisar ftlx6672mcc 10g DWDM 40km Multi-Rate T-SFP Optical Transceiver Product Spec Reva02Lelik GhhNo ratings yet

- Project Members: Underground Cable Fault Detection by Using GSMDocument14 pagesProject Members: Underground Cable Fault Detection by Using GSMgiribabuchowdaryNo ratings yet

- Installation Calculation Report: New - Project FullDocument14 pagesInstallation Calculation Report: New - Project FullToto SukisnoNo ratings yet

- Foam Frac NewDocument106 pagesFoam Frac Newyao nestorNo ratings yet

- Odisha Computer Application Centre Bhubaneswar Tender DocumentDocument39 pagesOdisha Computer Application Centre Bhubaneswar Tender DocumentBullzeye StrategyNo ratings yet

- Sosp-10g - RJ45Document13 pagesSosp-10g - RJ45melissaNo ratings yet

- Bridge Technology ReportFrom EverandBridge Technology ReportNo ratings yet

- The Traffic in A Telecommunication Network Is Meas 6079580d177630e4554f7be8Document2 pagesThe Traffic in A Telecommunication Network Is Meas 6079580d177630e4554f7be8SandhyaNo ratings yet

- Uppcl Je EcDocument62 pagesUppcl Je EcSandhyaNo ratings yet

- 621c9156535964eb612ecc76 English6351267666bce4c2e910e148 MergedDocument40 pages621c9156535964eb612ecc76 English6351267666bce4c2e910e148 MergedSandhyaNo ratings yet

- Week 7Document68 pagesWeek 7SandhyaNo ratings yet

- RealLAB2 ManualDocument5 pagesRealLAB2 ManualDiscord GrindNo ratings yet

- A High Power Headphone Amplifier Reference DesignDocument41 pagesA High Power Headphone Amplifier Reference DesignGERRY LNo ratings yet

- Strongarm SADocument6 pagesStrongarm SASayandip KarNo ratings yet

- Radio 1 Up Down ConversionDocument15 pagesRadio 1 Up Down Conversionayal gezeNo ratings yet

- Marshall MS2 4Document5 pagesMarshall MS2 4Mika Foric100% (1)

- Examen AdcDocument5 pagesExamen AdcValeria_Andree_2513No ratings yet

- Pulse and Digital Circuits LabDocument69 pagesPulse and Digital Circuits LabKrishna Chaitanya T100% (1)

- Flip Flops, R-S, J-K, D, T, Master Slave - D&E NotesDocument7 pagesFlip Flops, R-S, J-K, D, T, Master Slave - D&E NotesNida AhmedNo ratings yet

- Zen Er DiodeDocument2 pagesZen Er DiodeRanjan KumarNo ratings yet

- How To Build Linear FM 50watt With BLY90 (Circuit Diagram)Document7 pagesHow To Build Linear FM 50watt With BLY90 (Circuit Diagram)mohamed lamine elbiskriNo ratings yet

- Microelectronics: Circuit Analysis and DesignDocument15 pagesMicroelectronics: Circuit Analysis and DesignMei QiiNo ratings yet

- Logic FamiliesDocument7 pagesLogic Familiesjen2007No ratings yet

- DM74LS90/DM74LS93 Decade and Binary Counters: General DescriptionDocument10 pagesDM74LS90/DM74LS93 Decade and Binary Counters: General DescriptionThế giới điện tửNo ratings yet

- Datasheet 747cnDocument9 pagesDatasheet 747cnAhmad N Effendi KälteNo ratings yet

- CH 08 Solutions Practice ProblemsDocument6 pagesCH 08 Solutions Practice Problemsarjun raj0% (1)

- Class Notes For MOSFETSDocument4 pagesClass Notes For MOSFETSCedric MontianoNo ratings yet

- Transistor Biasing Represents . ConditionsDocument8 pagesTransistor Biasing Represents . ConditionsRaj PatelNo ratings yet

- Lecture (05) Boolean Algebra and Logic Gates: By: Dr. Ahmed ElshafeeDocument12 pagesLecture (05) Boolean Algebra and Logic Gates: By: Dr. Ahmed ElshafeevenkateshNo ratings yet

- MC14538B Dual Precision Retriggerable/Resettable Monostable MultivibratorDocument13 pagesMC14538B Dual Precision Retriggerable/Resettable Monostable MultivibratorAnonymous JoB5ZxgNo ratings yet

- Sel Guide TIDocument101 pagesSel Guide TIPaul VajdovicsNo ratings yet

- 2.sequential CircuitsDocument170 pages2.sequential CircuitsModyKing99No ratings yet

- Sgx524 Regulating Pulse-Width Modulators: 1 Features 3 DescriptionDocument30 pagesSgx524 Regulating Pulse-Width Modulators: 1 Features 3 DescriptionMarcus MapareNo ratings yet

- EEE1001 Basic Electrical and Electronics EngineeringDocument2 pagesEEE1001 Basic Electrical and Electronics Engineeringbhavay 07100% (1)

- 10 DC RegulatedDocument3 pages10 DC Regulatedamandeepsingh_adsNo ratings yet

- ISL8560IRZ DatasheetzDocument17 pagesISL8560IRZ Datasheetzpermadi uyeNo ratings yet

- Measurement Science Sensors Readout and Signal ConditioningDocument32 pagesMeasurement Science Sensors Readout and Signal Conditioningjorge Alberto Palacios HernandezNo ratings yet

- VLSI Record PDFDocument59 pagesVLSI Record PDFvaishnaviNo ratings yet

- Digital Logics and Microprocessor Lab Assessment 4: Registration No.: 19BIT0267 Name: Ankit Kumar Slot: L47 + L48Document9 pagesDigital Logics and Microprocessor Lab Assessment 4: Registration No.: 19BIT0267 Name: Ankit Kumar Slot: L47 + L48ANKITNo ratings yet

- Low-Power and Fast Full Adder by Exploring New and Gates: XOR XnorDocument13 pagesLow-Power and Fast Full Adder by Exploring New and Gates: XOR XnorBhargav Naidu PulugujjuNo ratings yet