Professional Documents

Culture Documents

Exos

Uploaded by

Ai ChaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Exos

Uploaded by

Ai ChaCopyright:

Available Formats

Exercises Unit 4: Sequential Systems Fundamentals of Computer Technology

Sequential Systems Exercises

Exercise 1:

Let X be a 3-bits number. Design a circuit that sets a JK flip-flop to “1” when X contains an odd number of “1” and

to “0” otherwise.

Exercise 2:

Identify the type of latch or flip-flop that has produced this time diagram -chronogram- as output.

C lk

t

Q

t

Exercise 3:

Design a 1/4 frequency divider that produces the following time diagram as output.

S a lid a

t

Exercise 4:

Knowing the inputs CLK and IN of a 5-bits register that initially is in the “00000” state, fill the following

chronogram with the time evolution of (Q0-Q4)

IN Q0 Q1 Q2 Q3 Q4

D Q D Q D Q D Q D Q

clk clk clk clk clk

CLK

CLK

IN

Q0

Q1

Q2

Q3

Q4

DEPARTAMENTO DE AUTOMÁTICA. UNIVERSIDAD DE ALCALÁ

Exercises Unit 4: Sequential Systems Fundamentals of Computer Technology

Exercise 5:

Deduce the four parallel outputs (A-D) of a shift-register made with 4 falling edge-triggered D-latches when the

serial input IN is the one shown in the following chronogram. Which data will be obtained after 6 clock cycles?

CLK

IN

Exercise 6:

Assuming that the following chronogram corresponds to a parallel input / serial output shift-register, deduce the

value of the serial output S in each cycle when the inputs D3-D0 are 1010, and the Shift/Load# signal takes the

shown values.

D3D0

Shift/Load# S

CLK

CLK

Shift/Load#

Exercise 7:

Suppose that the following time diagram corresponds to a bidirectional shift register in which the serial input is in

LOW level and the indicated control input RIGHT/LEFT# is applied. Deduce the state of the register in each cycle

if its initial value is Q0-Q3 = 1101 and the synchronization is with the rising edge of the clock.

R/L#

CLK

Q0

Q1

Q2

Q3

DEPARTAMENTO DE AUTOMÁTICA. UNIVERSIDAD DE ALCALÁ

Exercises Unit 4: Sequential Systems Fundamentals of Computer Technology

Exercise 8:

Deduce state Q0-Q4 of a universal shift register when the shown inputs are applied. Assume that the

synchronization is with the rising edge of the clock, that the only non-synchronous signal is CLR, and that the

control inputs S0-S1 work as follows: (S0, S1)=(1,1) parallel load; (0,0) no change; (0,1) left-shift, and (1,0) right-

shift. SR-ser and SL-ser are the Shift-Right and Shift-Left serial inputs respectively.

CLK

S0

S1

CLR

SR-ser

SL-ser

D0

D1

D2

D3

Q0

Q1

Q2

Q3

Exercise 9:

Design an asynchronous up counter from 2 to 12 with JK flip-flops.

Exercise 10:

Design an asynchronous down counter from 15 to 3 with JK flip-flops.

Exercise 11:

Design an synchronous up counter from 0 to 3 with D flip-flops.

Exercise 12:

Design an synchronous up/down counter from 0 to 7 with J-K flip-flops.

Exercise 13:

Design a synchronous down counter from 5 to 0 with D flip-flops. If the counter is in a state other than 5 to 0, it

must go to 0 in the next clock pulse.

DEPARTAMENTO DE AUTOMÁTICA. UNIVERSIDAD DE ALCALÁ

Exercises Unit 4: Sequential Systems Fundamentals of Computer Technology

Exercise 14:

Design a synchronous counter with JK flip-flops that follows the sequence 1,4,2,7.

Exercise 15:

Design a synchronous counter with D flip-flops and with JK flip-flops that follows the sequence 0,1,3,2,6,7,5,4.

Exercise 16:

Design a circuit with JK flip-flops that detects in the input X the sequence “101” setting the output Z to 1.

Exercise 17:

Design a circuit with D flip-flops that detects in the input X four consecutive “1” setting the output Z to 1.

Exercise 18:

Design a circuit with an input X and an output Y that must take the value “1” whenever the last two bits in the

input are equal, and “0” otherwise.

DEPARTAMENTO DE AUTOMÁTICA. UNIVERSIDAD DE ALCALÁ

You might also like

- D-Type Latch IIDocument19 pagesD-Type Latch IIjames-lawsonNo ratings yet

- MOSIS Counter Report Spring 2008Document60 pagesMOSIS Counter Report Spring 2008atom_2334No ratings yet

- Digital LabDocument51 pagesDigital LabBala SubramanianNo ratings yet

- L4: Sequential Building Blocks (Flip - Flops, Latches and Registers)Document24 pagesL4: Sequential Building Blocks (Flip - Flops, Latches and Registers)ggk87No ratings yet

- Sequential Circuit Design Using PLDsDocument8 pagesSequential Circuit Design Using PLDsJacob ChakoNo ratings yet

- Digital Logic Design Lab CountersDocument7 pagesDigital Logic Design Lab CountersDr-Eng Imad ShaheenNo ratings yet

- D and JK FFDocument22 pagesD and JK FFRawan AyyoubNo ratings yet

- Unit 3Document24 pagesUnit 3Raja BenitaNo ratings yet

- Lab Session # 8 Implementation of Registers: 3.1 Parallel-Load RegisterDocument8 pagesLab Session # 8 Implementation of Registers: 3.1 Parallel-Load RegisterAhmad M. HammadNo ratings yet

- Universidad Carlos III de Madrid Digital Electronics ExercisesDocument9 pagesUniversidad Carlos III de Madrid Digital Electronics ExercisesTrendkill Trendkill TrendkillNo ratings yet

- Exp No 8Document3 pagesExp No 8Gopinathan MNo ratings yet

- Registers and Counters Lecture SummaryDocument24 pagesRegisters and Counters Lecture SummaryPiyooshTripathiNo ratings yet

- Multiplication of Signed Numbers: CSE 430 - Assignment 3Document15 pagesMultiplication of Signed Numbers: CSE 430 - Assignment 3alam sifatNo ratings yet

- JK Flip Flop Experiment 9Document5 pagesJK Flip Flop Experiment 9Nev Callejo50% (2)

- ECET105 Lab 7 Enhanced Adder-SubtractorDocument14 pagesECET105 Lab 7 Enhanced Adder-SubtractorMicro EmissionNo ratings yet

- 6 111 l4 Seqntl BlocksDocument24 pages6 111 l4 Seqntl BlocksysakeunNo ratings yet

- Chapter 7 - Flip Flop and Registers2020Document25 pagesChapter 7 - Flip Flop and Registers2020SYAFIQAH BATRISYIA MOHD ZAHIRNo ratings yet

- Design Sequential Circuits LabDocument6 pagesDesign Sequential Circuits LabTarunesh PandeyNo ratings yet

- 17-Clock Skew PDFDocument2 pages17-Clock Skew PDFKrishna MohanNo ratings yet

- Part A: Flip Flops: Sequential CircuitsDocument18 pagesPart A: Flip Flops: Sequential CircuitssuriantoNo ratings yet

- Flip FlopsDocument29 pagesFlip FlopsShweta RoyNo ratings yet

- D Flipflop T Flipflop by VerilogDocument4 pagesD Flipflop T Flipflop by Verilogtungbk123100% (3)

- IIT Kanpur Introduction to Counters and Sequential CircuitsDocument3 pagesIIT Kanpur Introduction to Counters and Sequential CircuitsKeshav MusunuriNo ratings yet

- Emb 2Document7 pagesEmb 2ballmerNo ratings yet

- 07 Registers and CountersDocument28 pages07 Registers and CountersChandravadhana NarayananNo ratings yet

- Week 7Document21 pagesWeek 7İBRAHİM YÜMLÜNo ratings yet

- Combinational Circuits: ALU: AND OR ADD SUB SLT Zero (A B)Document16 pagesCombinational Circuits: ALU: AND OR ADD SUB SLT Zero (A B)anbaneNo ratings yet

- Prof. Anantha Chandrakasan and Prof. Don TroxelDocument10 pagesProf. Anantha Chandrakasan and Prof. Don TroxelCristian CastroNo ratings yet

- Experiment 9 Sequential Circuits Introduction To CountersDocument3 pagesExperiment 9 Sequential Circuits Introduction To CountersSai SaurabNo ratings yet

- Arithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitDocument22 pagesArithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitBadrul Afif ImranNo ratings yet

- DR - NGP Institute of Technology Coimbatore - 48: Department of Cse & ItDocument3 pagesDR - NGP Institute of Technology Coimbatore - 48: Department of Cse & ItParandaman Sampathkumar SNo ratings yet

- Digital Logic Design: Lecture # 17 University of TehranDocument23 pagesDigital Logic Design: Lecture # 17 University of TehranAbhishek BhardwajNo ratings yet

- 9 Counter CircuitsDocument9 pages9 Counter CircuitsWaseem AhmadNo ratings yet

- Chapter 7 - Flip FlopsDocument12 pagesChapter 7 - Flip FlopsAmeer AzharNo ratings yet

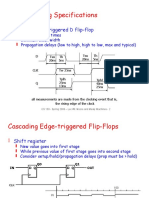

- Typical Timing Specifications: Positive Edge-Triggered D Flip-FlopDocument50 pagesTypical Timing Specifications: Positive Edge-Triggered D Flip-Flopanusha killariNo ratings yet

- 4 Bit Counter Design - Spring 2004Document15 pages4 Bit Counter Design - Spring 2004sandyk_24No ratings yet

- Lec8 Slides RTLDocument25 pagesLec8 Slides RTLAbdalrhman juberNo ratings yet

- DLD Exp 8 Student ManualDocument8 pagesDLD Exp 8 Student ManualS M AkashNo ratings yet

- Lab D4 CounterDocument8 pagesLab D4 Counterdhanabadee.kNo ratings yet

- WAVEFORM EXPLAINATION WholeDocument10 pagesWAVEFORM EXPLAINATION Whole12 EC ATUL KUMAR SRIVASTAVANo ratings yet

- VHDL Contadores e Registradores: IC/Unicamp 2011s2 Prof Mario CôrtesDocument19 pagesVHDL Contadores e Registradores: IC/Unicamp 2011s2 Prof Mario CôrtesLeonardo GonçalvesNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Er Sacchu SrivastavaNo ratings yet

- Experiment 9 (Flip Flops)Document7 pagesExperiment 9 (Flip Flops)groupidb3100% (3)

- Lab 1 ReportDocument12 pagesLab 1 ReportHarining TyasNo ratings yet

- CS1104 Lecture on Counters and RegistersDocument79 pagesCS1104 Lecture on Counters and RegistersKelvin YipNo ratings yet

- (Counter) Paper - 1 - 7967 - 163 PDFDocument57 pages(Counter) Paper - 1 - 7967 - 163 PDFmaprofNo ratings yet

- TTTTT Eeee AsDocument20 pagesTTTTT Eeee AsEric GongNo ratings yet

- Shift registers, counters, and their applicationsDocument13 pagesShift registers, counters, and their applicationsElizabeth AliazNo ratings yet

- Experiment 6: ObjectiveDocument9 pagesExperiment 6: Objectivedjun033No ratings yet

- Digital Ic Design TutorialDocument4 pagesDigital Ic Design Tutorialkrishna kanthNo ratings yet

- DLD Lab6 UpdatedDocument29 pagesDLD Lab6 UpdatedThành Nhân VũNo ratings yet

- Solution ST1 Set ADocument12 pagesSolution ST1 Set Agaurika.sawhney2003No ratings yet

- Assignment 3 Attempt Any 5 Question and Submit It On BB Submission Is 15 Jan, 2022Document5 pagesAssignment 3 Attempt Any 5 Question and Submit It On BB Submission Is 15 Jan, 2022EakanshNo ratings yet

- Experiment - 6Document2 pagesExperiment - 6Yashwant ChaudharyNo ratings yet

- Lesson 8 2 Asynchronous Counters11Document30 pagesLesson 8 2 Asynchronous Counters11Chris TineNo ratings yet

- MG4 HD4Document9 pagesMG4 HD4VIJAYPUTRANo ratings yet

- Report On Binary Decade CounterDocument2 pagesReport On Binary Decade CounterKruger BreedNo ratings yet

- Digital Design: An Embedded Systems Approach Using Verilog: Sequential BasicsDocument73 pagesDigital Design: An Embedded Systems Approach Using Verilog: Sequential Basicsavinash_yuvarajNo ratings yet

- Digital Electronics ProblemsDocument3 pagesDigital Electronics Problemschintu333No ratings yet

- The Most Complete Starter Kit For UNODocument158 pagesThe Most Complete Starter Kit For UNOShantan KajjamNo ratings yet

- Simplify Logic Circuits with Karnaugh MapsDocument10 pagesSimplify Logic Circuits with Karnaugh MapsChethan JayasimhaNo ratings yet

- DMD Schematic - Freetronics ForumDocument6 pagesDMD Schematic - Freetronics ForumapofviewNo ratings yet

- Experiment No. 14: Laboratory Hand Book Implementation of Siso, Sipo, Piso and Pipo Shift RegisterDocument9 pagesExperiment No. 14: Laboratory Hand Book Implementation of Siso, Sipo, Piso and Pipo Shift Register5611 M.Mubeen M.yaseenNo ratings yet

- Computer Architecture and OrganizationDocument39 pagesComputer Architecture and OrganizationchilledkarthikNo ratings yet

- Data Sheet: HEF40195B MSIDocument9 pagesData Sheet: HEF40195B MSIPedroZevallosNo ratings yet

- Digital Electronics Course OutlineDocument15 pagesDigital Electronics Course OutlineYash KuncolienkerNo ratings yet

- EET206 M4 Ktunotes - inDocument195 pagesEET206 M4 Ktunotes - inKhaled AlshurmanNo ratings yet

- Implementation of Barker Code PDFDocument9 pagesImplementation of Barker Code PDFBoby DubeyNo ratings yet

- Computer Organization and Design NotesDocument7 pagesComputer Organization and Design Notesishtiaq hussainNo ratings yet

- Me2009 - Control System Technology Lab Assignment 1: Hochiminh City University of Technology Mechatronics DepartmentDocument18 pagesMe2009 - Control System Technology Lab Assignment 1: Hochiminh City University of Technology Mechatronics DepartmentThanh HiếuNo ratings yet

- The Scan-Path Technique For Testable Sequential Circuit DesignDocument11 pagesThe Scan-Path Technique For Testable Sequential Circuit DesignLavanya Bj100% (1)

- Ardunio Language ReferenceDocument25 pagesArdunio Language ReferenceAlamcoNo ratings yet

- Digital Circuits and Systems Lab Manual For Iii Year/ V Semester B.Tech (Ee) LAB CODE (EE-306)Document55 pagesDigital Circuits and Systems Lab Manual For Iii Year/ V Semester B.Tech (Ee) LAB CODE (EE-306)NATIONAL XEROXNo ratings yet

- ECE216Document3 pagesECE216Abhishek KumarNo ratings yet

- A Single-Channel 10bit 160 MSs SAR ADC in 65 NM CMOSDocument9 pagesA Single-Channel 10bit 160 MSs SAR ADC in 65 NM CMOSZulfiqar AliNo ratings yet

- Cs3351-Dpco Lab ManualDocument42 pagesCs3351-Dpco Lab Manual19UBCA105 SASIREKA A100% (2)

- TTL Texas Instruments: 7400 Series Integrated CircuitsDocument14 pagesTTL Texas Instruments: 7400 Series Integrated CircuitsRickey Castillo ValenzuelaNo ratings yet

- Post-Grad Labview Course Exercise 11: G BoormanDocument3 pagesPost-Grad Labview Course Exercise 11: G BoormanDaud JanNo ratings yet

- BSRDocument4 pagesBSRRitesh SharmaNo ratings yet

- NEY VULCAN Instruction ManualDocument48 pagesNEY VULCAN Instruction ManualAlfredo MarcanoNo ratings yet

- GE Fanuc Series One PlusDocument300 pagesGE Fanuc Series One PlusRubén SánchezNo ratings yet

- Fifo Controller PresentationDocument26 pagesFifo Controller PresentationthemikulNo ratings yet

- LTP1245 Technical ReferenceDocument74 pagesLTP1245 Technical Referencemihai_damian_2No ratings yet

- Fujitsu mb1502Document15 pagesFujitsu mb1502haha2012No ratings yet

- Digital Ellectronics Book by Prabhakar SharmaDocument10 pagesDigital Ellectronics Book by Prabhakar SharmaRuth AlvaradoNo ratings yet

- Jtagboundary Scantest Apracticalapproach Harrybleeker Petervandeneijnden Fransdejong Kluweracademic 130617173055 Phpapp01 PDFDocument241 pagesJtagboundary Scantest Apracticalapproach Harrybleeker Petervandeneijnden Fransdejong Kluweracademic 130617173055 Phpapp01 PDFTuyen DinhNo ratings yet

- MD Rakibul Islam Rakib - LabReport5Document4 pagesMD Rakibul Islam Rakib - LabReport5A H MNo ratings yet

- CO Module 2 PPTDocument83 pagesCO Module 2 PPTIshu ishuNo ratings yet

- Fairchild by Element14 Batch 1Document9 pagesFairchild by Element14 Batch 1aoctaNo ratings yet