Professional Documents

Culture Documents

VLSI Lab Experiment List

Uploaded by

Shivam SanwariaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI Lab Experiment List

Uploaded by

Shivam SanwariaCopyright:

Available Formats

1.

Outline a model of seven-segment decoder to display HEX digits and translate the same

into

VHDL/Verilog/SystemVerilog RTL code. Simulate the design and find errors, if any.

Observe

and show the results.

2. Sketch/draw layouts of 2-input CMOS NAND gate and 2-input CMOS NOR gate by the

direct

translation of their schematics. Perform DRC (design rule checking) on the dawn layout and

find design rule errors, if any. Simulate and observe/examine the results. Interpret the same

for

the correctness of their functionality.

3. Outline a VHDL/Verilog model and write RTL code for a Moore machine with the

following state transition diagram. Simulate/compile the same using the Xilinx development

software

(Xilinx ISE 8.1i./10.1i) and find errors, if any. Test for its operation and analyse the results.

4. Outline a VHDL/Verilog model and write RTL code for a Mealy machine with the

following state transition diagram. Simulate/compile the same using the Xilinx development

software

(Xilinx ISE 8.1i./10.1i) and find errors, if any. Test for its operation and analyse the results.

5. Write a VHDL/Verilog/SystemVerilog RTL code to develop a tri-stated buffer controlled

4channel multiplexer with each channel carrying 4 signals. Simulate/compile the same using

the Xilinx development software (Xilinx ISE 8.1i./10.1i) and find errors, if any. Test and

evaluate the obtained results.

6. Write VHDL/Verilog/SystemVerilog RTL code and develop/design an adder that adds

three 8-bit binary number. Simulate using the Xilinx development software (Xilinx ISE

8.1i./10.1i and find errors, if any, test and validate its operation.

9. Design 2-input NAND gate using SCMOS and pseudo-nMOS logic families with given

specifications with the Virtuoso ADE of Cadence and design a 2-input XOR using symbols

of 2-input SCMOS NAND gate to achieve propagation delay (tp) not longer than 20 ns and

average power consumption (Pavg) not higher than 10 μW. Simulate the designs, test and

validate your anticipation. Simulate and report the propagation delay (tp) and power

consumption (Pavg) of your XOR gate. Load the input and output of XOR gate with

singlestage NAND to make the input and output realistic.

20. Write a VHDL/Verilog/SystemVerilog model and develop a 4:1-bit multiplexer. Simulate

and synthesize the CPLD design using the Xilinx development software (Xilinx ISE 8.1i.)

and find errors, if any. Create the CPLD configuration bitstream file (*.jed), use Spartan-2

CPLD Trainer Kit and download CPLD design (using the iMPACT programming software

and the JTAG cable) onto it, demonstrate and interpret the results displayed on the kit.

21. Develop a VHDL/Verilog/SystemVerilog model and design a parameterized 4-bit parity

generator circuit. The model should provide both an odd parity and an even parity output.

Simulate and compile/synthesize the FPGA design using the Xilinx development software,

create the FPGA configuration bitstream file (*.bit), download FPGA design (using the

iMPACT programming software and the USB cable) onto the prototyping kit (use Spartan-3E

FPGA Starter Kit), test and validate its operation.

22. Write a VHDL/Verilog model and develop a 4 16 decoder. Simulate the design using the

Xilinx development software (Xilinx ISE 8.1i/10.1i) and find errors, if any. Observe/examine

the results. Interpret the same for the correctness of their functionality.

23. Outline a model of 4-bit ripple carry full adder and translate/express the same into

VHDL/Verilog RTL code. Simulate/compile the same using the Xilinx development software

(Xilinx ISE 8.1i./10.1i) and find errors, if any. Observe and show the results and explain the

same.

24. Outline a VHDL/Verilog model and write RTL code for a synchronous counter` with the

following states. Simulate/compile the same using the Xilinx Integrated Synthesis

Environment (ISE) 8.1i./10.1i) and find errors, if any. Test for its operation and analyse the

results.

You might also like

- Vlsi Lab Manual 2013Document64 pagesVlsi Lab Manual 2013harish33330% (1)

- Vlsi RecordDocument61 pagesVlsi RecordRaghul MNo ratings yet

- Verilog HDL Lab QuizDocument69 pagesVerilog HDL Lab Quizsrilakshmi0850% (2)

- EC8661 VLSI Design Lab ManualDocument76 pagesEC8661 VLSI Design Lab ManualN.S.Priyanga 33100% (3)

- Lab1a v2 PDFDocument5 pagesLab1a v2 PDFKucing HitamNo ratings yet

- List of Lab Exercises For VHDL LabDocument3 pagesList of Lab Exercises For VHDL LabDivyanshu ShekharNo ratings yet

- Vlsi Manual 2013-2014Document36 pagesVlsi Manual 2013-2014hr_suresh_kNo ratings yet

- Experiment-1 Realization of Logic Gates: Cycle-IDocument57 pagesExperiment-1 Realization of Logic Gates: Cycle-Irameshkumar_aNo ratings yet

- EC8661-VLSI DESIGN LAB-116516724-Vlsi Lab ManualDocument149 pagesEC8661-VLSI DESIGN LAB-116516724-Vlsi Lab ManualAngelin ArulNo ratings yet

- EC6612 - VLSI Design Laboratory ManualDocument39 pagesEC6612 - VLSI Design Laboratory ManualSriramNo ratings yet

- F (A, B, C) A'BC' + A'BC+A' B' C'+ABC in SPO and POS Forms?: //casex ExampleDocument4 pagesF (A, B, C) A'BC' + A'BC+A' B' C'+ABC in SPO and POS Forms?: //casex ExampleSHREENo ratings yet

- Ec3561-Vlsi Design LabDocument144 pagesEc3561-Vlsi Design LabperiyasamyNo ratings yet

- mcb1700 LAB - Intro - ARM Cortex m3Document22 pagesmcb1700 LAB - Intro - ARM Cortex m3RagulANNo ratings yet

- HDL LAB Manual - OneDocument93 pagesHDL LAB Manual - Onebalajibs203285No ratings yet

- Ece5950 Tut4 Vcs GLDocument5 pagesEce5950 Tut4 Vcs GLVijay Kumar NNo ratings yet

- VlsilabDocument82 pagesVlsilabk poornimaNo ratings yet

- ProblemDocument12 pagesProblemrahul kapurNo ratings yet

- Cadence Tutorial PDFDocument61 pagesCadence Tutorial PDFJinesh Kb100% (1)

- Padmaja ResumeDocument4 pagesPadmaja Resumepadmajakavuri2000No ratings yet

- Verilog ADocument75 pagesVerilog Amano6690No ratings yet

- Ecad & Vlsi LabDocument98 pagesEcad & Vlsi LabbitseceNo ratings yet

- Lab ManualDocument36 pagesLab ManualKeerthana SahadevanNo ratings yet

- List of ExperimentsDocument58 pagesList of ExperimentsPraveen KumarNo ratings yet

- Project 2012fallDocument5 pagesProject 2012fallATHIRA V RNo ratings yet

- Project 12springDocument5 pagesProject 12springFarzin GhotbiNo ratings yet

- EC8661-VLSI DESIGN LAB-116516724-vlsi Lab Manual PDFDocument146 pagesEC8661-VLSI DESIGN LAB-116516724-vlsi Lab Manual PDFSathish Kumar G Assistant Professor ECE KingstonNo ratings yet

- Sample DSD Lab ManualDocument125 pagesSample DSD Lab ManualRajuNo ratings yet

- Lab ManualDocument78 pagesLab Manualgurusandhya11No ratings yet

- Verilog AMS TutorialDocument29 pagesVerilog AMS TutorialSiva KrishnaNo ratings yet

- VLSI Lab ManualDocument83 pagesVLSI Lab ManualSri SandhiyaNo ratings yet

- EC8661 VLSI Design Laboratory PDFDocument53 pagesEC8661 VLSI Design Laboratory PDFSINDHUNo ratings yet

- EC8661 VLSI Design LaboratoryDocument53 pagesEC8661 VLSI Design LaboratorySriram100% (4)

- VHDL Samples1Document55 pagesVHDL Samples1ramu143416305No ratings yet

- Lab Manual Exp 2 2022 23Document3 pagesLab Manual Exp 2 2022 23Anjali ShrivastavNo ratings yet

- Lab1 DocDocument14 pagesLab1 DocThanos GkanNo ratings yet

- Silvaco EDA DemoDocument11 pagesSilvaco EDA DemobhataviNo ratings yet

- HDL Manual 2018 19 UpdatedDocument59 pagesHDL Manual 2018 19 UpdatedNisha TNo ratings yet

- Embedded System Lab: Session Second - VHDLDocument4 pagesEmbedded System Lab: Session Second - VHDLBsal SokoNo ratings yet

- VLSI Front End Lab ManualDocument88 pagesVLSI Front End Lab ManualAllanki Sanyasi RaoNo ratings yet

- Vlsi Lab Manual: Department of Information TechnologyDocument135 pagesVlsi Lab Manual: Department of Information TechnologyVijay MythryNo ratings yet

- 06 HDL DebuggingDocument57 pages06 HDL DebuggingVasa VeerabhadraraoNo ratings yet

- Vlsi Ecad Lab Manual 2nd Cycle Exp 2019Document25 pagesVlsi Ecad Lab Manual 2nd Cycle Exp 2019Nilasha NilaNo ratings yet

- Experiment 7 Concurrent CodeDocument3 pagesExperiment 7 Concurrent CodeMohamd barcaNo ratings yet

- Exp - No.2 Design and Verification of Combinational Circuits Using VeriloghdlDocument72 pagesExp - No.2 Design and Verification of Combinational Circuits Using VeriloghdlAakanksha SharmaNo ratings yet

- Spring 2010 ELEC5200/6200 CPU Design Project Assigned Feb 8, 2010Document5 pagesSpring 2010 ELEC5200/6200 CPU Design Project Assigned Feb 8, 2010Qung NguyenNo ratings yet

- "L" Scheme - Sub Code: 24057: VLSI LaboratoryDocument1 page"L" Scheme - Sub Code: 24057: VLSI LaboratoryKarthikeyan JhkNo ratings yet

- Ece5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Document3 pagesEce5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Daniel MNo ratings yet

- VLSI ManualDocument40 pagesVLSI Manualgg.ganapathyNo ratings yet

- Question BankDocument4 pagesQuestion BankChetan GowdaNo ratings yet

- EC6612 VLSI Design LabDocument130 pagesEC6612 VLSI Design LabbalabaskerNo ratings yet

- ECE 515 Design of 3D Integrated Systems: Mixed Signal Simulation Using Cadence AMSDocument24 pagesECE 515 Design of 3D Integrated Systems: Mixed Signal Simulation Using Cadence AMSAzim ShihabNo ratings yet

- MC Lab Manual-2013Document76 pagesMC Lab Manual-2013saisuchandanNo ratings yet

- Mixed Mode VLSI Design - Cadence TutorialDocument8 pagesMixed Mode VLSI Design - Cadence TutorialRockstar_rohithNo ratings yet

- DCD QB Dec 2023 StudentDocument7 pagesDCD QB Dec 2023 StudentPranav VasudevNo ratings yet

- HDL ManualDocument44 pagesHDL ManualNithish ManjuNo ratings yet

- Department of Electronics & Communication Engineering.: Question BankDocument4 pagesDepartment of Electronics & Communication Engineering.: Question BankRamachandra TurkaniNo ratings yet

- Intermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingFrom EverandIntermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingNo ratings yet

- C Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingFrom EverandC Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Power-Star, US Patent #10666092Document16 pagesPower-Star, US Patent #10666092Shawn Paul BoikeNo ratings yet

- Digital Communication (1000 MCQS)Document181 pagesDigital Communication (1000 MCQS)Md Siraj Uddin100% (2)

- Learning Activity Sheet In: Computer Systems ServicingDocument12 pagesLearning Activity Sheet In: Computer Systems ServicingCarvalds 0315100% (1)

- PCB HelpDocument207 pagesPCB HelpRaraNo ratings yet

- Q2 Module1 G9 CSSDocument6 pagesQ2 Module1 G9 CSSAubz Almelia NavarroNo ratings yet

- Exercises With Finite State Machines: CS 64: Computer Organization and Design Logic Lecture #17 Winter 2019Document17 pagesExercises With Finite State Machines: CS 64: Computer Organization and Design Logic Lecture #17 Winter 2019Gabriel CañadasNo ratings yet

- Low Voltage Alternator - 4 Pole: 410 To 660 kVA - 50 HZ / 510 To 825 kVA - 60 HZ Electrical and Mechanical DataDocument12 pagesLow Voltage Alternator - 4 Pole: 410 To 660 kVA - 50 HZ / 510 To 825 kVA - 60 HZ Electrical and Mechanical DataMohamedOsmanNo ratings yet

- Jadwal Sholat Semester Ganjil 2022-2023 FinalDocument3 pagesJadwal Sholat Semester Ganjil 2022-2023 Finalwinata candraNo ratings yet

- Homework Set # 1Document4 pagesHomework Set # 1John SmithNo ratings yet

- CCTV Ajay DubeyDocument2 pagesCCTV Ajay DubeyAjay DubeyNo ratings yet

- HY Hanyoung Series CatalogueDocument2 pagesHY Hanyoung Series CatalogueTrần NguyênNo ratings yet

- Voltage Controlled Voltage SourceDocument1 pageVoltage Controlled Voltage SourceMd Aminul HaqueNo ratings yet

- Blank Letterhead..... PDF - 20240120 - 143356 - 0000Document1 pageBlank Letterhead..... PDF - 20240120 - 143356 - 0000jrsrecyclingltdNo ratings yet

- Honeywell LTP Sensors RT CurveDocument8 pagesHoneywell LTP Sensors RT CurveSwapneel BoseNo ratings yet

- Specification ChillerDocument28 pagesSpecification Chillermishtinil100% (1)

- 2VAA003058 B en AO01 AnalogOutputModuleDocument99 pages2VAA003058 B en AO01 AnalogOutputModulesabiulNo ratings yet

- Pes td2020 PDFDocument144 pagesPes td2020 PDFRody Garay100% (1)

- The Ranges: ABB Catalogue - 2/1Document3 pagesThe Ranges: ABB Catalogue - 2/1Martono Abu HanifNo ratings yet

- DENHAM TOWN HIGH SCHOOL-grade 9 Final DraftDocument6 pagesDENHAM TOWN HIGH SCHOOL-grade 9 Final DraftGuyan Gordon0% (1)

- Sd3 (U) Over Speed: Application Point of DetectionDocument1 pageSd3 (U) Over Speed: Application Point of DetectionAce Noah SomintacNo ratings yet

- Varplus M.PDF VallejosDocument4 pagesVarplus M.PDF VallejosJazmín SampierNo ratings yet

- Silicon PNP Power TransistorsDocument4 pagesSilicon PNP Power TransistorsEkoAriansyahNo ratings yet

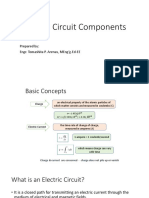

- 2-Electrical Circuit ComponentsDocument20 pages2-Electrical Circuit ComponentsTomashita ArenasNo ratings yet

- Rip550sha enDocument2 pagesRip550sha enJoonasNo ratings yet

- ECU® Trouble Shoot Guide For Engine-: ControlsDocument6 pagesECU® Trouble Shoot Guide For Engine-: ControlsAsad AbbasNo ratings yet

- Fronius tp1500 Service ManualDocument117 pagesFronius tp1500 Service Manualjulio lopezNo ratings yet

- Digital Signal Processing Lecture-03: Arnisha Akhter Lecturer, Dept. of CSE Jagannath UniversityDocument44 pagesDigital Signal Processing Lecture-03: Arnisha Akhter Lecturer, Dept. of CSE Jagannath UniversityKashfi ShormitaNo ratings yet

- Iec Standard: IEC 61089 - OVERHEAD CONDUCTOR-e.pdf IEC61089-amd1 PDFDocument2 pagesIec Standard: IEC 61089 - OVERHEAD CONDUCTOR-e.pdf IEC61089-amd1 PDFHosam AlzubairyNo ratings yet

- NeuroAmp ManualDocument36 pagesNeuroAmp ManualAlberto Barradas100% (1)

- Electrical Power Connectors: Product BrochureDocument68 pagesElectrical Power Connectors: Product BrochureWhite TigerNo ratings yet