Professional Documents

Culture Documents

M4-04 Memories

Uploaded by

Ahmed ShafeekCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

M4-04 Memories

Uploaded by

Ahmed ShafeekCopyright:

Available Formats

VLSI Design

ECE314

Spring 2022

M4: Digital Building Blocks

Lecture 4

Memories

DiaaEldin Khalil

Ain Shams University

Integrated Circuits Laboratory

D. Khalil ECE314 – M4 Lecture 4 1

Outline

• Memories

– Classifications

– Structure (Building Blocks)

– Memory core (Cells)

D. Khalil ECE314 – M4 Lecture 4 2

Classifications

Memories can be classified based on different factors

Most important classification is based on:

• Read/Write ability: read-only vs. read-write

• Value retention: non-volatile vs. volatile

3 main categories of memories: Non-volatile read-write memories,

(volatile) read-write memories, read-only memories

Other important classification is based on:

• Functionality: storage, portable storage, stand-alone, embedded,

cache, inside processor (instruction/data memory, register file)

• Access pattern: random vs. serial (FIFO, LIFO/stack, video)

• Storage mechanism: hard-wired vs. programmable vs. static vs.

dynamic

• I/O capability: single-port vs. multiple-port

• Addressability: byte, word, line

D. Khalil ECE314 – M4 Lecture 4 3

Classifications

Examples of popular memories and their classification

Hard-Wired Programmable Static Dynamic

FIFO,

Serial

LIFO,

RWM Access

Video

SRAM DRAM

EPROM,

Random

NVRWM EEPROM,

Access

Flash

ROM ROM PROM

• Size, speed, and power are also very important parameters

in evaluating memories

D. Khalil ECE314 – M4 Lecture 4 4

Basic Structure of Memory

• Memory core (storage cells)

Stores the values of N words, each of M bits,

in an NxM bit array (NxM is the size in bits)

• Peripherals

‒ Address decoder

Decodes K bits of address to N selectors

(called word-lines) to allow selecting only

1 word (line) of the core

‒ Sense amplifiers

Senses the voltage on vertical wires connecting

same bit in all words (bit-lines) to determine

the read value of the selected bit

‒ Drivers

Drives the voltage on vertical wires connecting same bit in all words

(bit-lines) to deliver the write value to the selected bit

‒ Control

Controls timing of different peripherals to ensure proper read/write

D. Khalil ECE314 – M4 Lecture 4 5

Square Structure of Memory

• N/M is called Aspect Ratio (AR)

• As N increase, bit-lines

become much longer,

and limits performance

& size (to almost 512 bits)

• Improve design to have

large N by keeping

AR close to 1

• Divide long column to

multiple smaller ones

and select one of them

using column multiplexer

• Performance & size

limitation improved

(to almost 256 kbits)

D. Khalil ECE314 – M4 Lecture 4 6

Hierarchical Structure of Memory

• Larger size is realized by combining multiple square structures

(blocks) into a larger memory with unified address and port

• Now some bits of the address are used to select a block

• Address is divided to 3 parts to select: a block, a column, and a line

• Block address can also be used save power by putting unselected

blocks in power saving mode

8Mbit SRAM

Byte addressable

Size=8x220=223bits

= 220B

Address=20bits

I/O-port=8bits

Max block size 256kbit

Block size=28x210=218

Row address=18/2=9

Column address=9-3=6

Block address=20-9-6=5

D. Khalil ECE314 – M4 Lecture 4 7

Memory Cells – NOR ROM

• In ROM, a single MOSFET can

form a cell that represent 0 or 1

• In NOR ROM, the MOSFET is

placed as pull-down device

in a NOR gate

• When a word-line is selected,

it is high and all others are low

• If MOSFET exists,

the bit-line is pulled down

• If MOSFET does not exist,

the bit-line remains precharged

• Needs ground lines in parallel to

word-lines (takes area)

D. Khalil ECE314 – M4 Lecture 4 8

Memory Cells – NAND ROM

• Another option is NAND ROM

• In NAND ROM, the MOSFET is

placed as pull-down device

in a NAND gate

• The word-lines have inverted logic

all are high except selected word

• If MOSFET exists,

the bit-line cannot be pulled down

• If MOSFET does not exist,

the bit-line is pulled down through

other MOSFETs

• Slower pull-down than NOR ROM

(many series MOSFETs)

• No needs for ground lines (saves area)

• More popular (less cost)

D. Khalil ECE314 – M4 Lecture 4 9

Memory Cells – PROM / NVRAM

• A MOSFET with programmable VT would be very useful

to have programmable ROM

• When VT is normal, it can be ON as previously explained

• When VT is too high, it cannot be ON (as if it does not exist)

• Must have a mechanism to increase VT (write) and reduce it to

normal (erase) and read (like previously explained)

• Dual-gate MOSFETs are nice devices to achieve this

(like FAMOS, FLOTOX, and ETOX)

• Write mechanisms: Avalanche hot-e injection or tunneling

• Erase mechanisms: UV irradiation or tunneling

• Needs additional high supply 12V to 25V to slowly write/erase

• Can be used to create PROM

and NVRWM like EPROM, EEPROM, and Flash

D. Khalil ECE314 – M4 Lecture 4 10

Memory Cells – SRAM (6T Cell)

• In volatile RWM (simply RAM),

some mechanism must allow

fast write/erase without

additional high supply

• Write/erase write (0 or 1)

• In SRAM, 2 inverters are connected

back-to-back forming a static latch

that can store 0 or 1 & 2 MOSFETs

are used to access stored value to

either read it or force it to desired value

• To read: BL & BL are precharged to mid-voltage, WL is enabled to

access Q & Q, BL & BL change values slightly depending on them,

sense amplifier amplifies difference

• To write: BL & BL are driven to desired value, WL is enabled to

access Q & Q, driven value is forced

• SRAM read & write are very fast

D. Khalil ECE314 – M4 Lecture 4 11

Memory Cells – DRAM (3T Cell)

• In DRAM, dynamic charge storage

replaces static latch

• Charge is stored on gate capacitance

of M2 altering the state of M2 (ON/OFF),

M1 is used to change stored value, and

M3 is used to read the stored value through

M2 drain rather than gate (to keep it safe)

• To read: BL2 is precharged to VDD, RWL is enabled to access M2,

BL is discharged/unchanged depending on X, sense amplifier

amplifies difference

• To write: BL1 is driven to desired value, WWL is enabled to access

X, X is charged/discharged to driven value

• Some other 3T variants exist

• Slower than SRAM but much smaller

D. Khalil ECE314 – M4 Lecture 4 12

Memory Cells – DRAM (1T Cell)

• Smallest RAM cell is achieved by 1T DRAM

• Sometimes called 1T-1C DRAM (needs capacitor)

• Charge is stored on capacitor Cs

& M1 is used to access stored value

to either read it or force it to desired value

• To read: BL is precharged to mid-voltage, WL is enabled to access

X, BL is discharged/charged slightly depending on X, sense

amplifier amplifies BL difference, X becomes mid-voltage and need

to be refreshed, sense amplifier drives BL to read value to

charge/discharge X back to original value (refresh).

• To write: BL is driven to desired value, WL is enabled to access X,

X is charged/discharged to driven value

• Smallest and least cost RAM (very popular)

• Much slower and needs refresh after each read

and regularly due to leakage

D. Khalil ECE314 – M4 Lecture 4 13

References

• Rabaey, section 12.1 & 12.2

D. Khalil ECE314 – M4 Lecture 4 14

You might also like

- 05 - Internal MemoryDocument34 pages05 - Internal Memoryobaid awanNo ratings yet

- Memory and Programmable LogicDocument52 pagesMemory and Programmable LogicMoayid AldeebNo ratings yet

- CH 5.ppt Type IDocument33 pagesCH 5.ppt Type Ilegal dexterNo ratings yet

- Memory Sub-System: CT101 - Computing SystemsDocument46 pagesMemory Sub-System: CT101 - Computing SystemstopherskiNo ratings yet

- Ch04 The Memory SystemDocument45 pagesCh04 The Memory SystemAlok SinghNo ratings yet

- 04-Chap5-Internal MemoryDocument37 pages04-Chap5-Internal Memoryabdul shakoorNo ratings yet

- 04-Chap5-Internal Memory RAMDocument10 pages04-Chap5-Internal Memory RAMabdul shakoorNo ratings yet

- Lecture 3: Memory Buffers and SchedulingDocument21 pagesLecture 3: Memory Buffers and SchedulingGere TassewNo ratings yet

- Memory and Programmable LogicDocument47 pagesMemory and Programmable Logicdewantosatrio50% (2)

- Chapter 2Document66 pagesChapter 2mayazyounasNo ratings yet

- 2.2 CU Memory System DesignDocument75 pages2.2 CU Memory System Designprakuld04No ratings yet

- Unit V - Memories - VDocument82 pagesUnit V - Memories - V040-NishanthNo ratings yet

- Unit 3 OF ESDDocument22 pagesUnit 3 OF ESDTanveer ShariffNo ratings yet

- Digital Integrated Circuits: Designing Memory and Array StructuresDocument70 pagesDigital Integrated Circuits: Designing Memory and Array StructuresShubham GargNo ratings yet

- Memory Devices, Circuits, and Subsystem Design: The 8088 and 8086 Microprocessors, Triebel and Singh 1Document55 pagesMemory Devices, Circuits, and Subsystem Design: The 8088 and 8086 Microprocessors, Triebel and Singh 1Ivan-Jeff AlcantaraNo ratings yet

- 05 Internal MemoryDocument73 pages05 Internal Memorybree789No ratings yet

- Internal Memory 3rdDocument64 pagesInternal Memory 3rdDare DevilNo ratings yet

- 11 Cache Memory, Internal, ExternalDocument102 pages11 Cache Memory, Internal, Externalbezelx1No ratings yet

- Module 5.3Document39 pagesModule 5.3Asha DurafeNo ratings yet

- Computer Organization Architecture - Topic 5Document36 pagesComputer Organization Architecture - Topic 5asj233510377No ratings yet

- 05 Internal MemoryDocument33 pages05 Internal MemoryfikaduNo ratings yet

- Memories CompleteDocument51 pagesMemories Completeyeswanth chowdary nidamanuriNo ratings yet

- Unit 6 Memory 2Document53 pagesUnit 6 Memory 2Shiv shankar SinghNo ratings yet

- 5 - Internal MemoryDocument22 pages5 - Internal Memoryerdvk100% (1)

- 05 - Internal MemoryDocument33 pages05 - Internal MemoryRangpur Habhit PolytechnicNo ratings yet

- CH 5Document26 pagesCH 5DraxZebNo ratings yet

- SramDocument34 pagesSramRicha GuptaNo ratings yet

- 05 - Internal MemoryDocument63 pages05 - Internal MemoryKashif AmjadNo ratings yet

- Sistem Mikroprosessor - W2S1Document46 pagesSistem Mikroprosessor - W2S1Josep HuluNo ratings yet

- 05 - Internal MemoryDocument25 pages05 - Internal Memorymubarra shabbirNo ratings yet

- William Stallings Computer Organization and Architecture 8th Edition Internal MemoryDocument22 pagesWilliam Stallings Computer Organization and Architecture 8th Edition Internal MemoryabbasNo ratings yet

- Week 9 Internal External MemoriesDocument43 pagesWeek 9 Internal External Memoriesmuhammad maazNo ratings yet

- Lect 6Document24 pagesLect 6King RobleNo ratings yet

- 14 Ram&romDocument40 pages14 Ram&romvenikiranNo ratings yet

- Programmable Logic DevicesDocument38 pagesProgrammable Logic DevicesgayathriNo ratings yet

- Chat 6 SummaryDocument2 pagesChat 6 SummaryPrincess CutabNo ratings yet

- Chapter 5 Memory and Memory InterfaceDocument56 pagesChapter 5 Memory and Memory InterfacePetra KalasaNo ratings yet

- WINSEM2017-18 - ECE5023 - TH - TT531A - VL2017185001741 - Reference Material I - Copy of Lecture 2&3Document33 pagesWINSEM2017-18 - ECE5023 - TH - TT531A - VL2017185001741 - Reference Material I - Copy of Lecture 2&3AashishNo ratings yet

- CSPC 36 3rd Unit 8 NitDocument28 pagesCSPC 36 3rd Unit 8 NitRashika KhannaNo ratings yet

- Memory and IO DesignDocument91 pagesMemory and IO DesignMworozi DicksonNo ratings yet

- Module 5Document15 pagesModule 5iron manNo ratings yet

- Internal Memory: Computer Architecture and OrganizationDocument38 pagesInternal Memory: Computer Architecture and OrganizationSidra MallickNo ratings yet

- Chapter 5 - Internal MemoryDocument33 pagesChapter 5 - Internal MemoryHPManchester100% (1)

- 14 Ram&romDocument40 pages14 Ram&rompatilrajucNo ratings yet

- MemoryDocument97 pagesMemorynerdmehNo ratings yet

- Chapter 4 Memory ElementDocument87 pagesChapter 4 Memory ElementWann FarieraNo ratings yet

- Random Access MemoryDocument3 pagesRandom Access MemoryJi Rawat JiNo ratings yet

- 8086 Full NotesDocument50 pages8086 Full NotesPREETHINo ratings yet

- William Stallings Computer Organization and Architecture 8th Edition Internal MemoryDocument20 pagesWilliam Stallings Computer Organization and Architecture 8th Edition Internal MemorySheikh ZainNo ratings yet

- RAM 2522 DKDocument40 pagesRAM 2522 DKDon Nipuna PandithasundaraNo ratings yet

- Chap 6Document48 pagesChap 6siddhiNo ratings yet

- Memory Related To VLSIDocument63 pagesMemory Related To VLSIIndrajeet GautamNo ratings yet

- William Stallings William Stallings Computer Organization and Architecture and Architecture 8th Edition P Internal MemoryDocument33 pagesWilliam Stallings William Stallings Computer Organization and Architecture and Architecture 8th Edition P Internal MemoryMonicaNo ratings yet

- Lecture 06Document43 pagesLecture 06Meena ShahNo ratings yet

- Lec10 Sram1Document19 pagesLec10 Sram1VenkatGollaNo ratings yet

- William Stallings Computer Organization and ArchitectureDocument22 pagesWilliam Stallings Computer Organization and ArchitectureJannat HappyNo ratings yet

- Memory and Programmable LogicDocument8 pagesMemory and Programmable LogicMd. Sarafat AyonNo ratings yet

- DigitalLogic ComputerOrganization L14 Memories HandoutDocument25 pagesDigitalLogic ComputerOrganization L14 Memories HandoutPhan Tuấn KhôiNo ratings yet

- Nintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8From EverandNintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8No ratings yet

- MainDocument9 pagesMainAhmed ShafeekNo ratings yet

- Project ECE414 Spring 2023 RX Design V2Document2 pagesProject ECE414 Spring 2023 RX Design V2Ahmed ShafeekNo ratings yet

- Project ECE414 Spring 2023 RX Design V2Document2 pagesProject ECE414 Spring 2023 RX Design V2Ahmed ShafeekNo ratings yet

- BRFall 16 TSPCDocument4 pagesBRFall 16 TSPCSMBNo ratings yet

- Assignment1 ECE414s Spring 2024 EM SimulationDocument2 pagesAssignment1 ECE414s Spring 2024 EM SimulationAhmed ShafeekNo ratings yet

- AN143f PDFDocument8 pagesAN143f PDFitamar_123No ratings yet

- Lab 2Document1 pageLab 2Ahmed ShafeekNo ratings yet

- M1-02 Cost - ScalingDocument32 pagesM1-02 Cost - ScalingAhmed ShafeekNo ratings yet

- M3-01 Implementation ApproachesDocument18 pagesM3-01 Implementation ApproachesAhmed ShafeekNo ratings yet

- M4-02 MultipliersDocument10 pagesM4-02 MultipliersAhmed ShafeekNo ratings yet

- M2-02 Interconnect Delay - PowerDocument26 pagesM2-02 Interconnect Delay - PowerAhmed ShafeekNo ratings yet

- M1-01 CMOS Fabrication - LayoutDocument27 pagesM1-01 CMOS Fabrication - LayoutAhmed ShafeekNo ratings yet

- IntroductionDocument49 pagesIntroductionAhmed ShafeekNo ratings yet

- Verilog RevisionDocument27 pagesVerilog RevisionAhmed ShafeekNo ratings yet

- System Verilog IIDocument18 pagesSystem Verilog IIAhmed ShafeekNo ratings yet

- Charge-Pump With A Regulated Cascode CircuitDocument3 pagesCharge-Pump With A Regulated Cascode CircuitAhmed ShafeekNo ratings yet

- Day2 PMDocument97 pagesDay2 PMAndrea FasatoNo ratings yet

- A 2.4-Ghz Monolithic Fractional-Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance MultiplierDocument9 pagesA 2.4-Ghz Monolithic Fractional-Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance MultiplierSampoornaGonellaNo ratings yet

- 1 - Integer-N Frequency SynthesizersDocument101 pages1 - Integer-N Frequency SynthesizersAhmed ShafeekNo ratings yet

- Analysis of Phase Noise in Phase - Frequency PDFDocument11 pagesAnalysis of Phase Noise in Phase - Frequency PDFkaart_3000No ratings yet

- LithographyDocument38 pagesLithographyAhmed ShafeekNo ratings yet

- CLean RoomsDocument29 pagesCLean RoomsAhmed ShafeekNo ratings yet

- Course PreambleDocument15 pagesCourse PreambleAhmed ShafeekNo ratings yet

- CMOS Transistor Reliability Unit-3Document8 pagesCMOS Transistor Reliability Unit-3AgnathavasiNo ratings yet

- Indikator Water Level Control: Circuit Diagram of Final ProjectsDocument4 pagesIndikator Water Level Control: Circuit Diagram of Final ProjectsJoseph BryanNo ratings yet

- Isc N-Channel MOSFET Transistor IRFP4768 IIRFP4768: FeaturesDocument2 pagesIsc N-Channel MOSFET Transistor IRFP4768 IIRFP4768: FeaturesAudio with PankajNo ratings yet

- U18ec096 Vlsi Lab5Document8 pagesU18ec096 Vlsi Lab5bharath malothNo ratings yet

- TIP35/35A/35B/35C: Silicon NPN Power TransistorsDocument4 pagesTIP35/35A/35B/35C: Silicon NPN Power TransistorsJose David Perez ParadaNo ratings yet

- 90 NM K SramDocument4 pages90 NM K SramVLSISD36 Edwin DominicNo ratings yet

- Modern Semiconductor Devices For Integrated Circuits 1st Edition Hu Solutions ManualDocument19 pagesModern Semiconductor Devices For Integrated Circuits 1st Edition Hu Solutions Manualorianahilaryic3u1s100% (23)

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument4 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationmigcasterNo ratings yet

- RK9410 Mosfet 30v 7aDocument4 pagesRK9410 Mosfet 30v 7aVukica IvicNo ratings yet

- Datasheet PDFDocument3 pagesDatasheet PDFMaury MacíasNo ratings yet

- Transistor TestDocument1 pageTransistor Testmahesh12ka4No ratings yet

- Chet Boylestad Electronic 8 I PNPN I and Other Devices Fill in The BlanksDocument7 pagesChet Boylestad Electronic 8 I PNPN I and Other Devices Fill in The BlanksVam SiNo ratings yet

- Evolution of DRAM 1kbit To 1gbit June 2004Document47 pagesEvolution of DRAM 1kbit To 1gbit June 2004Peter GillinghamNo ratings yet

- Bipolar Transistor Cross-Reference Search - Equivalent TransistorsDocument3 pagesBipolar Transistor Cross-Reference Search - Equivalent TransistorsDhany SiregarNo ratings yet

- Fets: Field Effect Transistors: MosfetsDocument25 pagesFets: Field Effect Transistors: MosfetsMANIKANDANNo ratings yet

- Sirena Policial AmericanaDocument9 pagesSirena Policial AmericanaromarioNo ratings yet

- 2SD1391 Shenzhen SPTECH Microelectronics Co LTD DatasheetDocument2 pages2SD1391 Shenzhen SPTECH Microelectronics Co LTD Datasheetgiambi-1No ratings yet

- DSD Exp 1Document8 pagesDSD Exp 1shylaja9No ratings yet

- Underlap Double Gate Mosfet1234Document26 pagesUnderlap Double Gate Mosfet1234Arvind DautaniyaNo ratings yet

- MicroElectronicsTransistorsIcDataBook Text PDFDocument371 pagesMicroElectronicsTransistorsIcDataBook Text PDFاسد کمالNo ratings yet

- Puolop-Pt4435 C351420Document3 pagesPuolop-Pt4435 C351420Hyppo BolangiNo ratings yet

- C2328a PDFDocument2 pagesC2328a PDFVictorManuelBernalBlancoNo ratings yet

- Pass Transistor LogicDocument17 pagesPass Transistor LogicHimanshiNo ratings yet

- Dual N-Channel Trench MOSFET 30V, 12.9A, 10.5m : Features General DescriptionDocument6 pagesDual N-Channel Trench MOSFET 30V, 12.9A, 10.5m : Features General DescriptionyaidelNo ratings yet

- SCR - VI Characteristics - Switching CharacteristicsDocument50 pagesSCR - VI Characteristics - Switching CharacteristicsSahale Shera Lutse 18BEE0376No ratings yet

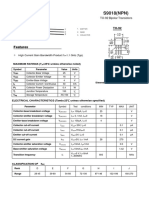

- S9018 (NPN) : FeaturesDocument2 pagesS9018 (NPN) : Featuresran lanNo ratings yet

- P2610ADG Niko-Sem: N-Channel Enhancement Mode Field Effect TransistorDocument6 pagesP2610ADG Niko-Sem: N-Channel Enhancement Mode Field Effect Transistormhmd193No ratings yet

- Question 3Document19 pagesQuestion 3LIVYA DASINI A/P SOMAIAH STUDENTNo ratings yet

- 507 - EnginneringDocument60 pages507 - EnginneringUdara DissanayakeNo ratings yet

- Ohp Cmos 3 (H20-4-25) PDFDocument26 pagesOhp Cmos 3 (H20-4-25) PDFGouse ModeenNo ratings yet