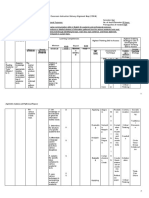

EASWARI ENGINEERING COLLEGE DEPARTMENT OF ECE

QUESTION BANK

Subject : DIGITAL PRINCIPLES AND SYSTEM DESIGN Subject Code : CS 2202 Faculty : D. Vydeki Class : III Sem CSE (A & B) UNIT I PART-A 1. Convert the (153.513)10 to Octal. [May 2010] 2. Simplify the following Boolean functions to a minimum number of literals (a) (x + y)(x + y) (b) xy + xz + yz [May 2010] 3. Draw the logic diagram for the Boolean expression ((A+B)C)D using NAND gates.

[Nov 2009]

4. Perform subtraction using 1s complement (11010)2 - (10000)2 [Nov 2009] 5. Perform 9s and 10s compliment subtraction between 18 and -24[Nov 2009] 6. Simplify the following Boolean expression to a minimum number of literals: AB + A C D + A B D + A B C D [May 2009] 7. Simplify the following Boolean function by Karnaugh map method: F(A, B, C, D) = m(1, 5, 9, 12, 13, 15) [May 2009] 8. Convert (367)10 into Excess - 3 code. [Dec 2008] 9. Express Gray code 10111 into binary numbers. [Dec 2008] 10. Write the Boolean function of an X-OR gate give its truth table. [Dec 2008] 11. What is the largest binary number that can be expressed with 12 bits? What is the equivalent decimal and hexadecimal? [May 2008] [Link] (x+y) (x+y' ) to a minimum number of literals. [May 2008] 13. Find the minterm of xy+yz+xy' z. [May 2008] 14. What are minterms? [May 2007] 15. Convert the following function into sum of product form (AB+C)(B+CD)

[May 2007]

16. Convert the following number from one base to other (65.342)8=( )7

[May 2007]

17. What is the advantage of gray codes over the binary number sequence?

[May 2007]

18. Simplify the following Boolean function: (a) x(x+y) (b) xy + xz + yz [May 2007] 19. Convert the following number from one base to other (354.52)6 = ( ) 10 (100)10 = ( ) 16. [Dec 2006] 20. What are the different ways to represent a negative number? [Dec 2006] 21. Find the hexadecimal equivalent of the octal number 1024.77 [May 2006] 22. Express x1+x2+x3 as the product of maxterms. [May 2006] 23. State a single rule, which can be used to form the complement of a Boolean expression in one step. [Dec 2005] 24. Find the minterm expansion of f(a,b,c,d)= a(b+d)+acd [Dec 2005] 25. Define the following terms: implicant, prime implicant, essential prime implicant. 26. Convert 231.34 to base 7.

[Dec 2005] [May 2005]

�27. State and prove Consensus theorem. [May 2005] 28. Implement AND gate and OR gate using NAND gate. [May 2005] 29. Find the binary representation of decimal 125. [Dec 2004] 30. Complement the expression X(Y+Z) [Dec 2004] 31. Show that a positive logic NAND gate is the same as a negative logic NOR gate

[Dec 2004]

32. A hexadecimal counter capable of counting upto atleast (10,000)10 is to be constructed. What is the minimum number of hexadecimal digits that the counter must have?

[May 2004]

33. Convert the decimal number 214 to hexadecimal. [May 2004] 34. Show that how NAND gates can be used to implement the basic Boolean functions. 35. Define the following: minterm and maxterm. 36. Find the decimal equivalent of (346)7. 37. Find the complement of x+yz. PART-B 1. (i).Simplify the following Boolean function F together with dont-care condition d, and then express the simplified function in sum of minterms F (w, x, y, z) = (1,3,7,11,15) + d (0,2,5) (ii) Implement the following Boolean function with NAND gates. F (x, y, z) = (1,2,3,4,5,7) . [May 2010] 2. Determine the prime-implicants of the Boolean function by using the tabulation method. F(w, x, y, z)=(1,4,6,7,8,9,10,11,15) . [May 2010] 3. Simplify the following Boolean expression using Quine McCluskey method: F=m(0,9,15,24,29,30)+d(8,11,31). [Nov 2009] 4. i) Implement Boolean expression for EXOR gate using NAND and NOR gates. ii) Prove that (AB+C+D)(C+D)(C+D+E)=ABC+D. iii) Using 2s complement perform (42)10 (68)10 [Nov 2009] 5. Simplify the following Boolean function F together with dont care condition using ....Karnaugh map method. a. F(A,B,C,D) = m(0, 6, 8, 13,14), d(A, B, C, D) = m(2, 4, 10) b. F(A,B,C,D) = m(0, 2, 4, 5, 8, 14, 15), d(A, B, C, D) = m(7, 10,13) c. F(A,B,C,D) = m(4, 6, 7, 8, 12, 15), d. d(A, B, C, D) = m(2,3,5,10,11,14) [May 2009] 6. Simplify the following Boolean expressions to a minimum number of literals. (i) ABC + ABC+AB (ii) ABC + AC + B (iii)(A+B)(A+B) (iv)BC(AD + AD) + AB (v) (A + B+ AB)(AB + AC + BC) [May 2009] 7. (i) Obtain the canonical POS for F(A,B,C,D) = (A+B)(B+C)(A+C) (ii) Using k-map method obtain the minimal SOP and POS expressions for the f unction F(x,y,z,w) = (1,3,4,5,6,7,9,12,13) [Dec 2008] 8. (i) Apply Demorgan theorem for the function (a+b+c)d. (ii) Find the complement of A+BC+AB. [May 2008]

[May 2004] [May 2004] [Dec 2003] [Dec 2003]

�9. Using Tabulation method simplify the Boolean function F(V,W,X.Y,Z)=S(0,1,8,11,12,15,20,21,22,24,29,31) which has the dont care conditions d(9,18,30) [May 2007] 10. (i).Simplify the Boolean function using map method: F(w,x,y,z)= S(0,2,4,6,8,10,12,14) (ii).Perform subtraction on the following numbers using the 9s complement of subtrahend (1)5763-3145 (2)59-9876 (3)5200-561 [May 2007] 11. Using Tabulation method simplify the Boolean function F(w, x, y, z) = (1, 2, 3, 5, 9, 12, 14, 15) which has the dont care conditions d(4, 8, 11). [Dec 2007] 12. Reduce the Boolean function using K Map technique and implement using gates F(w, x, y, z) = (0, 1, 4, 8, 9, 10) which has the dont care conditions d(w, x, y, ,z) = (2, 11). [Dec 2007] 13. What is the advantage of using Tabulation method? Determine the prime implicants of the following function using Tabulation method. F(w,x,y,z) = (1,4,6,7,8,9,10,11,15) [Dec 2006] 14. Given the following Boolean function F = AC + AB + ABC + BC Express it in sum of minterms and find the minimal SOP expression [May 2006] 15. Find a minimum sum of products expression for the following function using Quine-McClusky method. F (A,B,C,D,E) = (0,2,3,5,7,9,11,13,14,16,18,24,26,28,30) [Dec 2005] 16. (i) Determine the minimum sum of products and minimum product of sums for f = bcd+bcd+acd+abbcd (ii) Find the minterm expansion of f(a,b,c,d) = a(b+d)+acd [May 2005] 17. (i) Find a network of AND and OR gates to realize f(a,b,c,d) = m (1,5,6,10,13,14) (ii) Design a network to convert 8-4-2-1 BCD code to excess 3 code. [May 2005] [Link] the following Boolean function by using Tabulation method F=(0,1,2,8,10,11,14,15) [Dec 2004] 19. State and Prove the postulates of Boolean Algebra. [May 2004] 20. (i) State and prove DeMorgans Theorem. (ii) Determine the SOP form of F(abcd)= (0,2,4,6,8) + d(10,11,12,13,14,15)

[Dec 2003]

UNIT II PART-A 1. 2. 3. 4. 5. 6. 7. 8. 9. Distinguish between the combinational and sequential logic circuits. [May 2010] What do you mean by HDL? . [May 2010/ May 2003] Draw the logic diagram for half adder. [Nov 2009] Define Combinational circuit. [May 2009/ May 2004] What is the need for code conversion? Give two commonly used codes.[May 2009] Give the truth table of Full adder. [Dec 2008/ May 2004] List the important features of HDL. [Dec 2008] What are functions of encoders and decoders? [May 2008] What is Multiplexer? [May 2008]

�10. What is logic synthesis in HDL? [Dec 2007] 11. What is a priority encoder? [Dec 2007] 12. What are the modeling techniques available to build HDL module? [May2007] 13. What is a demultiplexer? [Dec 2006] 14. What is a full adder? [May2007/ 2006] 15. Write down the truth table of a half subtractor [Nov 2005/ 2004] 16. Draw the half adder circuit. [Nov 2005] 17. Explain the design procedure for combinational circuits [May 2004] 18. What is overflow? [May 2004] 19. Write down the truth table of a. full subtractor. [Nov 2003] 20. Draw 4 bit binary parallel adder [Nov 2003] 21. What is meant by VHDL and what is its advantage [Nov 2003] 22. Define magnitude comparator? [Nov 2003] 23. What are the two steps in Gray to binary conversion? [May 2003] 24. What is HDL? [May 2003] PART B 1. Design a combinational logic diagram for BCD to Excess-3 code converter.

[May 2010]

2. (i) Design a Full Adder circuit with necessary diagram. (ii) Write the HDL description of the circuit specified by the following Boolean function. x =AB+ C y= C. [May 2010/ May 2006] 3. a) Explain the gray code to binary converter with the necessary diagram . b) Design a half subtractor circuit [Nov 2009] 4. With neat diagram explain BCD subtractor using 9s and 10s complement method

[Nov 2009]

5. Design a BCD to 7 segment decoder. [May 2009] 6. With a suitable block diagram explain the operation of BCD adder. [May 2009] 7. Draw and explain the working of a carry-look ahead adder. [Dec 2008] 8. Design a 4 bit magnitude comparator two 4 bit numbers [Dec 2008] 9. Construct a combinational circuit to convert given binary coded decimal number into an Excess 3 code. For example when the input to the gate is 0110 then the circuit should generate output as 1001. [May 2008] 10. Construct a full adder circuit and write a HDL program module for the same.

[May 2008/ May 2007]

11. Construct a BCD adder circuit and write a HDL program module for the same.

[May 2008]

12. i)Design a combinational circuit to convert BCD to gray code ii) Design a 4 bit subtractor. [Dec 2007] 13 .i) Design a combinational circuit to convert Excess-3 code to BCD code. ii) Design a 2bit 2bit multiplier. [Dec 2007] 14. Design a network of AND and OR gates to convert excess 3 code to 8-4-2-1 BCD code. [May 2007] 15. Explain the procedure for converting Binary to Gray code number and Gray code to Binary number with samples. [Nov 2006] 16. Design a BCD adder to add two BCD digits [Nov 2005]

�17.(a) Design a 4-bit binary to BCD code converter (b)Design a 4-bit binary to gray code converter [Nov 2005] 18. (i) Design a full adder and full subtractor (ii) Draw the block diagram of 2s complement adder/subtractor [May 2005] 19. Design a circuit to compare to four bit numbers [Nov 2004] 20. What is the need of arithmetic circuits? Design a full subtractor .How it is different from a full adder. [Nov 2003] 21. What is the need of arithmetic circuits? Design a full subtractor .How it is different from a full adder. [Nov 2003] 22. Design a combinational circuit that accepts 3 bit binary number and converts it to excess 3 codes. [May 2003/May 2005] UNIT-III PART A 1. 2. 3. 4. 5. What is Multiplexer? [May 2010] Define Encoder. [May 2010] What is the difference between decoder and demultiplexer? [Nov 2009] What is programmable logic array? How does it differ from ROM? [Nov 2009] What is Decoder? Draw the block diagram and truth table for 2 to 4 decoder.

[May 2009]

6. Give some applications of multiplexer. [May 2009/ May 2007/ May 2003] 7. Draw the block diagram of Dynamic RAM cell. [Dec 2008] 8. Explain write operation with an example. [May 2008] 9. Draw the circuit diagram for 3 bit parity generator. [May 2008] 10. What is RAM? [Nov 2007] 11. What are the types of ROM? [Nov 2007] 12. What is a priority encoder? [May 2007] 13. Write the logic equation and draw the internal logic diagram for a 4-to-1 MUX.

[May 2007]

14. How can a decoder be converted into a demultiplexer? [Nov 2006] 15. Give any two application of PLAS. [Nov 2006] 16. What is a sequential circuit? [May 2006] 17. How does ROM retain information? [May 2006] 18. List basic types of programmable logic devices. [Dec 2005] 19. Define address and word: [Dec 2005] 20. What is a decoder and obtain the relation between the number of inputs n and outputs m of a decoder [May 2005] 21. Define binary decoder? [May 2005] 22. What will be the maximum number of outputs for a decoder with a 6bit data word?

[May 2005]

23. What is field programmable logic array? [Dec 2004] 24. What is PROM? [Dec 2004] 25. What is programmable logic array? How it differs from ROM? [May 2004] 26. What is mask - programmable? [May 2004] 27. Give the comparison between prom and PLA. [May 2003] 28. Mention the uses of decoders [May 2003]

�PART B 1. (i) Design a 3 to 8-line decoder with necessary diagram. (ii) Implement the given Boolean function using 4 1 multiplexer. F(x, y, z) =(1, 2, 6, 7) . [May 2010] 2. We have found a minimum sum of products expression for each of two function, F and G, minimizing them individually (no sharing) F = WY + XYZ G = WXY + XY +WYZ . (i) Implement them with a ROM. (ii) Implement them in the PLA using no more than four terms. . [May 2010] [Link] with necessary diagram a BCD to 7 segment display decoder. [Nov 2009] 4.(i)Write the comparison between PROM,PLA,PAL. (ii)Design a BCD to excess-3 code converter and implement using PLA. [Nov 2009] 5. Define Decoder. Design a 3 to 8 decoder. With suitable block diagram explain how a 4 to 16 decoder can be performed by using the same. [May 2009] 6. Explain the operation of DRAM with suitable diagram. Also explain how Read/Write operations are performed in DRAM with timing diagram. [May 2009] 7. Implement the function with a multiplexer. F(A,B,C,D) = (0,1,3,4,8,9,15) [Dec 2008] 8. (i) Explain the operation of a 4 bit magnitude comparator circuit. (ii) Explain even parity checker. [Dec 2008] 9. i) Implement the following with a multiplexer F(A, B, C) = (1, 2, 4, 5) (8) (ii) What is micro programmed control unit? Explain the different types of ROM. (8) [May 2008] 10. Explain the different types of shift registers with neat diagram. [May 2008] [Link] Rom, implement a combinational circuit which accepts a 3 bit number and generates an output binary number equal to the square of the input number.

[Dec 2007]

12. i) Implement the following Boolean function using 8:1 multiplexer. F(A,B,C,D)=ABD+ACD+BCD+ACD ii) What are the advantages of PLA over ROM?Explain the internal construction of PLA. [May 2007] 13. A combinational circuit is defined by the functions F1(A,B,C)=(3,5,6,7) F2(A,B,C)=(0,2,4,7) implement the circuit with a PLA. [May 2007] 14 .i) Implement the following function with a multiplexer. F(A,B,C,D)=(0,1,3,4,8,9,15). ii)A combinational circuit is defined by the functions: F1(A,B,C)= (3,5,6,7) F2(A,B,C)= (0,2,4,7) [May 2006] 15. A combinational circuit is described by the functions F1 =m(3,5,7), F2=m(4,5,7) Implement the circuit with a PLA having 3inputs, 3 product terms and two outputs [Nov 2005] [Link] the structural VHDL description for 2 to 4 decoder and explain it in detail. 17. (i) Design a BCD to excess 3 code converter using a ROM (ii)Design and explain the working of a 1 to 8 demultipexer

[Nov 2005] [May 2005]

�18. Compare the following PLDS: PROM, PLA, PAL [May 2005] [Link] that when two input multiplexer drive another 2 input MUX, the result is a 4 i/p MUX [Nov 2004] 20. Write a HDL program for 2*1 MUX [Nov 2004] 21. Draw a 4:1 Mux and implement the following function F=(0,1,2,4,6,9,12,14)

[May 2004]

UNIT-IV PART A 1. Differentiate Flip-Flop from Latches. [May 2010] 2. Draw the excitation table and state diagram for JK and SR Flip-Flop. [May 2010] 3. Write down the differences between sequential and combinational circuit? [Nov 2009] 4. What is race around condition? [Nov 2009] 5. How many flip-flops are required for designing synchronous MOD 5 counter?

[May 2009]

6. What is shift register? List the types. [May 2009] 7. Convert a T-FF into an sr-FF. Draw the circuit. [Dec 2008] 8. Draw the state diagram of a MOD-10 counter. [Dec 2008] 9. What are the differences between sequential and combinational logic? [May 2008] 10. Draw the logic diagram for D-Type Latch. [May 2008] 11. How can a D flip flop be converted in to a T flip-flop? [May 2007, Nov 2005] 12. How many states are there in a 3-bit ring counter? What are they? [May 2007] 13. What is meant by the term edge triggered? [Dec 2007] 14. How does a J-K flip flop differ from an S-R flip-flop in its basic operation.

[Nov 2006]

15. Define Synchronous counter. [Nov 2006] 16. What are the memory elements used in a clocked sequential circuit? [May2006] 17. What is meant by state diagram? [Nov 2005] 18. List out at least four applications of FFs [Nov 2005] 19. What are the states of a 4-bit ring counter [Nov 2005] 20. What are the principal between synchronous and asynchronous counters?

[Apr 2005]

21. Distinguish between combinational logic circuits and sequential logic circuits?

[Apr 2005]

22. What are the advantages of shift registers? [May 2005/Nov 2003] 23. Derive the characteristic equation of T flip flop [May 2004] 24. What is the minimum of Flip flops required to build a counter of modulus 8

[May 2004]

25. Define propagation Delay. [May 2004] 26. Define rise time and fall time? [May 2004] 27. What is edge-triggered flip-flop? [May 2004] 28. How will you convert a JK flip-flop into a D-flip flop? [Nov 2003] 29. What is a shift register? [Nov 2003] 30. What are the various types of triggering of FFS [Nov 2003] 31. The t pd for each flip-flop is 50 ns. Determine the maximum operating frequency for MOD - 32-ripple counter [Nov 2003] 32. Why is a parallel counter faster than ripple counter? [Nov 2003]

�PART B 1. Design a synchronous sequential circuit using JK flip-flop to generate the following sequence and repeat. 0, 1, 2, 4, 5, 6 [May 2010] 2. What is the aim of state reduction? Reduce the given state diagram and prove that the both state diagrams are equal.

[May 2010]

3. Design and implement a Mod-5 synchronous counter using JK flip-flop. Draw the timing diagram also. [Nov 2009] 4. (i)Explain the working of master slave JK flip-flop. (ii)Draw the diagram for a 3 bit ripple counter. [Nov 2009] 5. (i) Write a verilog description for JK negative edge triggered flip flop with clock CLK. (ii) Explain the characteristic table for JK flipflop. [May 2009] 6. (i) Design a sequential circuit with JK FF to satisfy the following state equations. A(T+1) = ABCD+ABC+ACD+ACD B(T+1) = AC+CD+ABC C(T+1) = B D(T+1) =D (ii) Draw the logic diagram of a D-FF using NAND gates and explain. [Dec 2008] 7. With a neat circuit explain a universal shift register. [Dec 2008] 8. Design a T-FF giving the flow table, state table, state assignment, excitation table and excitation map. [Dec 2008] 9. Design a 3 bit binary Up Down counter [May 2008] 10. (i) Summarize the design procedure for synchronous sequential circuit (6) (ii) Reduce the following state diagram. (10) [May 2008] 11. Explain the operation of 4-bit binary ripple counter. [Dec 2007] 12. Explain the operation of BCD counter. [Dec 2007] 13.i) Explain the operation of D-Type Edge triggered flip-flop. ii) Write HDL code for the following Mealy sate diagram. [May 2007] 14. What are the general capabilities of universal shift register?And write the HDL code for the same. [May 2007] 15. Draw the Four bit Johnson counter and explain its operation. [Nov 2006] 16. a)Design an Asynchronous BCD down counter using J-K flip=flop and verify its operation. [May 2006] b) What are Edge triggered [Link]. 17. Design a synchronous mod-8 down counter and implement it [Nov 2005]

�[Link] a sequence detector circuit with a single input line and a single output [Link] the input consists of the sequence 101,the output should be [Link] example, if the input is 00110101then the output is 00000101. In other words, overlapping sequences are allowed. Use any type of flip flop.

[Nov 2005]

19. Design a modulus 5 counter using JK flip flop and implement it. Construct its Timing diagram [Nov 2005] 20. What is race around condition? How is it avoided? [Nov 2005] 21. Draw the schematic diagram of Master slave JK FF and input and output waveforms. Discuss how does it prevent race around condition. [Nov 2005/May 2005/ 22. Design and explain the working of a synchronous mod-3 counter 23. Design and explain the working of a up-down ripple counter. [May 2005] 24. Using JK flip-flops design a parallel counter, which counts in the sequence 101,110,001,010,000,111,101 [Nov 2004] [Link] SR flip-flops design a parallel counter, which counts in the sequence 000,111,101,110,001,010,000. [May 2004] [Link] the state diagram and characteristic equation of TFF, DFF, and JKFF

[Nov 2003] Nov 2006] [May 2005]

UNIT-V PART A 1. What is Race Conditions? [May 2010/ Dec 2008/ Dec 2006] 2. What happens when a Hazard happens in a logic circuit? [May 2010] 3. What is meant by a lockout condition? [Nov 2009] 4. What are the steps for design of asynchronous sequential circuit? [Nov 2009] 5. Define Race condition. How can it be avoided? [May 2009] 6. Explain Dynamic Hazard. [Dec 2008] 7. What is a hazard in combinational circuits? [May 2008] 8. What are the assumptions made for pulse mode circuit? [May 2008, 2007] 9. What is a hazard in combinational circuits? [May 2009May 2007/ Dec 2007] 10. What is an Asynchronous sequential circuit. [May 2006] 11. Mention any advantage and disadvantage of asynchronous sequential circuits.

[Nov 2005]

12. What is a critical race? Why should it be avoided? 13. Define the terms race, critical race and non-critical race 14. Define a primitive flow table 15. Define static 0-hazard,static 1-hazard and dynamic hazard

[Nov 2005/May 2005]

[Nov 2005/2003] [Nov 2005]

[Apr 2005/ Nov 2004/Nov 2003]

16. What is the most important consideration in making state assignments for asynchronous networks [Apr 2005] 17. What is the difference between Mealy machine and Moore machine [Apr 2005] 18. Give the comparison between state Assignment Synchronous circuit and state assignment asynchronous circuit. [May 2004/ Dec 2005] 19. Explain the procedure for state minimization. [May 2004/Dec 2005] 20. What are the types of asynchronous circuits [May 2004/ Dec 2005] 21. What are the steps for the design of asynchronous sequential circuit? [May 2004] 22. What is fundamental mode sequential circuit? [May 2003/ May 2004]

�23. When is a sequential machine said to be strongly connected

[Nov 2003]

PART B 1. With suitable example and diagram explain the hazards in combinational and sequential logic circuits. [May 2010] 2. With necessary example and diagram explain the concept of reduction of state and flow tables. [May 2010] 3. (i)Design a comparator. (ii)Design a non sequential ripple counter which will go through the states 3,4,5,7,8,9,10,3,4..draw bush diagram also [Nov2009] 4. (i)Design a parity checker. (ii)Design a sequential circuit with JK flip-flop. [Nov2009]

11

5. Design an asynchronous sequential circuit wih inpus x1 and x2 and one output z. Initially both the inputs are equal to 0. When x1 and x2 becomes 1, z becomes 1. When second input also becomes 1, z = 0; The output stays at 0 until circuit goes back to initial state. [May 2009] 6. Discuss in detail the static hazards. [May 2009] 7. a) Develop the state diagram and primitive flow table for a logic system that has 2 inputs, x and y and an output z. And reduce primitive flow table. The behavior of the circuit is stated as follows. Initially x = y = 0. Whenever x = 1 and y = 0 then z = 1, whenever x = 0 and y = 1 then z = 0. When x = y = 0 or x = y = 1 no change in z it remains in the previous state. The logic system has edge-triggered inputs without having a clock. The logic system changes state on the rising edges of the 2 inputs. Static input values are not to have any effect in changing the z output. [Dec 2008] 8. (i) What is the objective of state assignment in asynchronous circuit? Give hazard free realization for the following Boolean functions f(A, B, C, D) = M(0, 2, 6, 7, 8, 10, 12) (8) (ii) Summarize the design procedure for asynchronous sequential circuit. (8)

[Dec 2008]

9. a).An asynchronous sequential circuit is described by the following excitation and output function X=(Y1Z1W2)X +(Y1Z1W2) S=X (i).Draw the logic diagram of the circuit (ii).Derive the translation table and output map

�(iii).Describe the behavior of the circuit [May 2008] 10. Explain essential, static and dynamic hazards in digital circuit. Give hazard-free realization for th following Boolean function .F(I,J,K,L)= S(1,3,4,5,6,7,9,11,15)

[May 2008]

[Link] asynchronous network has two inputs and one output. The input sequence X1X2 =00, 01,11causes the output to become [Link] next input change then causes the output to return to 0. No other input sequence will produce a 1 output. Construct the state diagram using primitive flow table. [Dec 2007] 12. i)Give hazard-free realization for the following Boolean function F(A,B,C,D)=m(1,3,6,7,13,15) ii) Summarize the design procedure for asynchronous sequential circuit. [May 2007] 13. An asynchronous sequential circuit is described by the following excitation and output function. Y=X1X2+(X1+X2)Y & Z=Y i) Draw the logic diagram ii) Derive the transition table and output map iii) Describe the behavior of the circuit. [May 2007] 14. a)Draw the fundamental mode Asynchronous circuits and explain in detail. b)Define the following terms. i) Critical-race ii) Non-Critical race iii)Hazards iv) Flow table [Nov 2006] 15. a)Design a circuit with inputs A and B to give an output Z equal to 1 when AB=11 but only if A becomes 1 before B, by drawing total state Diagram, primitive flow table and output map in which transient state is Included. b) Design a circuit with primary inputs A and B to give an output Z equal to 1 When A becomes 1 if B is already [Link] Z=1 it will remain so until A goes to c) Draw waveform diagram, total state diagram, primitive flow table for designing the circuit. [May 2006] 16. What are the two types of asynchronous circuits? Differentiate between them.

[Nov 2005]

17. Discuss on Hazards and Races [Nov 2005] 18. Design a asynchronous sequential circuit with 2 inputs X and Y and with one output Z whenever Y is 1, input X is transferred to [Link] Y is 0,the output does not change for any change in X. use SR latch for implementation of the circuit.

[May 2005]

[Link] notes on asynchronous sequential circuits and VHDL [Nov 2004] 20. What is a merger graph .How it is used to reduce states in the incompletely specified table [May 2004] [Link] are the problems in asynchronous circuits and what are essential hazards and static hazards how it can be eliminated. [Nov 2003] 22. Explain the meaning of Mealy machines and Moore machines [May 2003]

PREPARED BY ([Link])

REVIEWED BY ([Link])

APPROVED BY HoD/ECE