Professional Documents

Culture Documents

Basic Cmos: Doan Minh Tue

Basic Cmos: Doan Minh Tue

Uploaded by

DoanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Basic Cmos: Doan Minh Tue

Basic Cmos: Doan Minh Tue

Uploaded by

DoanCopyright:

Available Formats

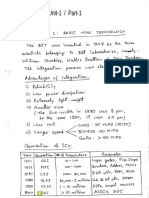

BASIC CMOS

DOAN MINH TUE

CONFIDENTIAL INFORMATION

The information contained in this presentation is the confidential and proprietary

information of Synopsys. You are not permitted to disseminate or use any of

the information provided to you in this presentation outside of Synopsys

without prior written authorization.

IMPORTANT NOTICE

In the event information in this presentation reflects Synopsys’ future plans, such plans

are as of the date of this presentation and are subject to change. Synopsys is not

obligated to update this presentation or develop the products with the features and

functionality discussed in this presentation. Additionally, Synopsys’ services and products

may only be offered and purchased pursuant to an authorized quote and purchase order

or a mutually agreed upon written contract with Synopsys.

Synopsys Confidential Information © 2019 Synopsys, Inc. 2

P-N Junction

Physic of semiconductor

Zeros bias

Forward bias

Reverse bias

IV curve of the silicon p-n junction diode

Synopsys Confidential Information © 2019 Synopsys, Inc. 3

Semiconductor

A semiconductor is a material product usually comprised of silicon, which conducts electricity more

than an insulator, such as glass, but less than a pure conductor, such as copper or aluminum. Their

conductivity and other properties can be altered with the introduction of impurities, called doping, to

meet the specific needs of the electronic component in which it resides

Synopsys Confidential Information © 2019 Synopsys, Inc. 4

Mobility

In solid-state physics, the electron mobility characterises how quickly an electron can move

through a metal or semiconductor when pulled by an electric field. There is an analogous

quantity for holes, called hole mobility. The term carrier mobility refers in general to both electron

and hole mobility

Semiconductor mobility depends on the impurity concentrations (including donor and acceptor

concentrations), defect concentration, temperature, and electron and hole concentrations. It also

depends on the electric field, particularly at high fields when velocity saturation occurs

The mobility of electrons is faster than that of holes

Synopsys Confidential Information © 2019 Synopsys, Inc. 5

Silicon Lattice

Transistors are built on a silicon substrate

Silicon is a Group IV material

Forms crystal lattice with bonds to four neighbors

Synopsys Confidential Information © 2019 Synopsys, Inc. 6

Doping

Silicon is a semiconductor

Pure silicon has no free carriers and conducts poorly

Adding dopants increases the conductivity

Group V: extra electron (n-type)

Group III: missing electron, called hole (p-type)

N-type P-type

Synopsys Confidential Information © 2019 Synopsys, Inc. 7

Zero bias in P-N Junction

In a p-n junction, without an external applied voltage, an equilibrium condition is reached in

which a potential difference forms across the junction. This potential difference is called built-in

potential

Synopsys Confidential Information © 2019 Synopsys, Inc. 8

Forward bias in PN Junction

In forward bias, the p-type is connected with the positive terminal and the n-type is connected

with the negative, current can flow (depending upon the magnitude of the applied voltage). This

configuration is called "Forward Biased”

Reduce the width of the depletion region

Diffusion current increases exponentially

Synopsys Confidential Information © 2019 Synopsys, Inc. 9

Reverse bias in PN Junction

Connecting the p-type region to the negative terminal of the voltage supply and the n-type region

to the positive terminal corresponds to reverse bias

Increase the width of the depletion region

Diffusion current is reduced exponentially

Synopsys Confidential Information © 2019 Synopsys, Inc. 10

IV curve of the silicon p-n junction diode

Synopsys Confidential Information © 2019 Synopsys, Inc. 11

CMOS basic

Why CMOS?

MOSFET structure

MOSFET operation

I/V Characteristics

Second-Order Effects

Fabrication process

FINFET vs MOSFET

Synopsys Confidential Information © 2019 Synopsys, Inc. 12

Why CMOS?

CMOS technologies rapidly captured the digital market: CMOS gates dissipated power only

during switching and required very few devices

MOS devices could be scaled down more easily than those of other types of transistors

The low cost of fabrication and the possibility of placing both analog and digital circuits on the

same chip so as to improve the overall performance and/or reduce the cost of packaging made

CMOS technology attractive

Another critical advantage of MOS devices over bipolar transistors is that the former can operate

with lower supply voltages. The lower supplies have permitted a smaller power consumption for

complex integrated circuits

Synopsys Confidential Information © 2019 Synopsys, Inc. 13

MOSFET structure

Four-terminal device: gate (G), source (S), drain (D) and bulk (B)

The device size (channel region) is specified by width (W) and length (L)

Two kinds of MOSFETs: n-channel (NMOS) and p-channel (PMOS)

Source and drain terminals are specified by the operation voltage

Synopsys Confidential Information © 2019 Synopsys, Inc. 14

MOSFET operation

Threshold Voltage

Cut-off

Triode Region

Saturation region

Synopsys Confidential Information © 2019 Synopsys, Inc. 15

Threshold Voltage

Voltage at gate Vg required to fully invert our semiconductor

For , electrons are attracted to the interface under gate, establishing a "channel" for conduction.

The channel is also called the “inversion layer’’

For , depletion region under channel remains relatively constant, but the charge in inversion

layer increases

Synopsys Confidential Information © 2019 Synopsys, Inc. 16

Cut-off region

Cut-off: <

• MOSFET is “OFF”

• No formation of channel

• No Drain current flows ( ID = 0 )

• MOSFET operates as an “open switch”

Synopsys Confidential Information © 2019 Synopsys, Inc. 17

Triode Region

Triode Region: > and < –

• Formation of channel, connect the source and drain terminals

• A positive voltage between terminals D and S will create an flow through the channel

• The channel connecting terminal Drain and terminal Source is treated as a resistor

Synopsys Confidential Information © 2019 Synopsys, Inc. 18

Saturation region

Saturation region: > and > –

• MOSFET “ON”

• MOSFET operates as a low resistance “closed switch”

• At the point = – , the channel is pinched off at the drain side

Synopsys Confidential Information © 2019 Synopsys, Inc. 19

I/V Characteristics

Cut-off region: < )

=0

Triode region: > )

–) -

Deep triode Region: << –

–)

Synopsys Confidential Information © 2019 Synopsys, Inc. 20

Saturation: > )

Synopsys Confidential Information © 2019 Synopsys, Inc. 21

Second-Order Effects

Body Effect

Channel-Length Modulation

Subthreshold conduction

Synopsys Confidential Information © 2019 Synopsys, Inc. 22

Body Effect

As becomes more negative, more holes can break loose from atoms under the gate area,

leaving negative ions behind => depletion region can contribute more charge => inversion layer

forms for larger => threshold voltage increase

Synopsys Confidential Information © 2019 Synopsys, Inc. 23

Channel-Length Modulation

Channel length modulation is a shortening of the length of the inverted channel region with

increase in drain bias for large drain biases. The result of channel length modulation is an

increase in current with drain bias

As increase, the width of depletion region between inversion layer and drain increase =>

effective channel length decrease => increase

Synopsys Confidential Information © 2019 Synopsys, Inc. 24

Subthreshold Conduction

Subthreshold conduction is the current between the source and drain of a MOSFET when the

transistor is in subthreshold region, or weak-inversion region, that is, for gate-to-source voltages

below the threshold voltage

Synopsys Confidential Information © 2019 Synopsys, Inc. 25

Fabrication process

CMOS transistors are fabricated on silicon wafer

Lithography process similar to printing press

On each step, different materials are deposited or etched

Easiest to understand by viewing both top and cross-section of wafer in a

simplified manufacturing process

Synopsys Confidential Information © 2019 Synopsys, Inc. 26

Fabrication Steps

Step 1: First we choose a substrate as a base for

fabrication. For N- well, a P-type silicon substrate is

selected

Step 2: Oxidation

Step 3: Growing of Photoresist

Synopsys Confidential Information © 2019 Synopsys, Inc. 27

Step 4:

• Expose photoresist through n-well mask

• Strip off exposed photoresist

Step 5: Etching

Step 6: Removal of Whole Photoresist

Layer

Synopsys Confidential Information © 2019 Synopsys, Inc. 28

Step 7: Formation of N-well

Step 8: Removal of SiO2

Step 9: Deposition of Polysilicon

Synopsys Confidential Information © 2019 Synopsys, Inc. 29

Step 10: Formation of Gate Region

Step 11: Oxidation Process

Step 12: Masking and Diffusion

Synopsys Confidential Information © 2019 Synopsys, Inc. 30

Step 13: Removal of Oxide

Step 14: P-type Diffusion

Step 15: Laying of Thick Field oxide

Step 16: Metallization

Synopsys Confidential Information © 2019 Synopsys, Inc. 31

FINFET vs MOSFET

• FinFET is a multi gate MOSFET. It is named as FinFET because the 3D structure above the

subtrate looks like set of fins.

• It is 3D transistor and widely used in integration circuit recently instead of planar CMOS FET.

• It is used more than other FETs because of its area of performance, lower leakage power, low

voltage operation.

Synopsys Confidential Information © 2019 Synopsys, Inc. 32

FINFET vs MOSFET?

Synopsys Confidential Information © 2019 Synopsys, Inc. 33

Single stage amplifier

• Common-source

• Common-gate

• Source-follower

• Cas-code

Synopsys Confidential Information © 2019 Synopsys, Inc. 34

Common-source

• In common-source amplifiers, the input is (somehow!) connected to G and the output is

(somehow!) taken from D

• We can divide CS amplifiers into two groups:

o Without source degeneration(no body effect for the main transistor)

o With source degeneration (with body effect for the main transistor)

Synopsys Confidential Information © 2019 Synopsys, Inc. 35

Common-Source Stage with Resistive Load

• Resistive Load is often used in high-speed circuit because of the linearity of resistance, and also

the output voltage swing may reach up to Vdd

Synopsys Confidential Information © 2019 Synopsys, Inc. 36

Large-Signal Analysis

• When < , M1 is in cut-off region, =0, =

• When >

• When

and triode region

• When , M1 is in the triode region

• If

if

Synopsys Confidential Information © 2019 Synopsys, Inc. 37

Small-Signal Model

• Assuming that the transistor is in saturation region and channel length modulation is ignored

• Output Voltage:

• Small-signal Gain:

Synopsys Confidential Information © 2019 Synopsys, Inc. 38

• Channel length modulation becomes more significant as increases

• Using the Small-Signal Model because of its simplicity

// =>

• Intrinsic gain

If ≈ ∞, then

Called the “intrinsic gain” of a transistor, this quantity represents the

maximum voltage gain that can be achieved using a single device.

For ideal long-channel device -> ∞, Intrinsic gain -> ∞.In today’s

CMOS technology, gm of short-channel devices is between

roughly 5 and 10. We usually assume 1/gm << .

Synopsys Confidential Information © 2019 Synopsys, Inc. 39

• Input impedance of common source is ∞

• Output impedance of common source is

Synopsys Confidential Information © 2019 Synopsys, Inc. 40

You might also like

- 15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsDocument31 pages15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsPallavi Ch71% (7)

- Basic Cmos: Doan Minh TueDocument42 pagesBasic Cmos: Doan Minh TueRua Tuệ ĐoànNo ratings yet

- Analog Physical Design: Analog Basic Building BlocksDocument36 pagesAnalog Physical Design: Analog Basic Building Blocksmohamed mahmoudNo ratings yet

- Amp LierDocument13 pagesAmp LierDoanNo ratings yet

- Question & AnswerDocument10 pagesQuestion & AnswerArighna BasakNo ratings yet

- Numerical Simulation of Silicon Heterojunction Solar Cells Featuring Metal Oxides As Carrier-Selective ContactsDocument9 pagesNumerical Simulation of Silicon Heterojunction Solar Cells Featuring Metal Oxides As Carrier-Selective ContactsOussama IkhlefNo ratings yet

- Unit - 3: Microwave Diodes - Lecture 4 Impatt DiodeDocument3 pagesUnit - 3: Microwave Diodes - Lecture 4 Impatt DiodesuryaNo ratings yet

- LINEAR INTEGRATED CIRCUITS AND APPLICATIONS (2 Marks)Document16 pagesLINEAR INTEGRATED CIRCUITS AND APPLICATIONS (2 Marks)Gokul G-Factor Kumar100% (5)

- Introduction To Vlsi TechnologyDocument32 pagesIntroduction To Vlsi TechnologysivaNo ratings yet

- FinFet TechnologyDocument13 pagesFinFet TechnologyChintha VenuNo ratings yet

- Linear Integrated Circuits - EC2254Document77 pagesLinear Integrated Circuits - EC2254Muthu LakiNo ratings yet

- FINFETDocument15 pagesFINFETPrajwal GowdaNo ratings yet

- Leakage Power Optimization Using Gate Length Biasing and Multiple VTDocument13 pagesLeakage Power Optimization Using Gate Length Biasing and Multiple VTSanupKumarSinghNo ratings yet

- Vlsi 2 Marks QSDocument16 pagesVlsi 2 Marks QSJay SubbareddyNo ratings yet

- Introduction To VLSI Technology: Abhijeet KumarDocument32 pagesIntroduction To VLSI Technology: Abhijeet KumarPrithireddy ThenetiNo ratings yet

- Question Bank: Vlsi-DesignDocument21 pagesQuestion Bank: Vlsi-DesignHarshini ANo ratings yet

- Lenin Raja,: Assistant Professor / Research CoordinatorDocument5 pagesLenin Raja,: Assistant Professor / Research CoordinatorArighna BasakNo ratings yet

- Vlsi 2marksDocument5 pagesVlsi 2marksJenny ThanushawNo ratings yet

- 7.6.2. Poly-Silicon Gate TechnologyDocument14 pages7.6.2. Poly-Silicon Gate TechnologyHarshad KulkarniNo ratings yet

- VLSIDocument475 pagesVLSIAtharva JoshiNo ratings yet

- PN Junction ThesisDocument7 pagesPN Junction ThesisWhitney Anderson100% (2)

- Seminar KKKDocument67 pagesSeminar KKKNavyasreeNo ratings yet

- Automotive IC-Design: January 2004Document16 pagesAutomotive IC-Design: January 2004Sergey RosenfeldNo ratings yet

- Important Short Questions and Answers - VLSI Design - CMOS TechnologyDocument10 pagesImportant Short Questions and Answers - VLSI Design - CMOS TechnologysamactrangNo ratings yet

- Iiiyr Visem Vlsi DesignDocument20 pagesIiiyr Visem Vlsi DesignlokeshwarrvrjcNo ratings yet

- (SOI) Technology Have Emerged As An Efective Means of ExtendingDocument38 pages(SOI) Technology Have Emerged As An Efective Means of ExtendingShwetaAgarwalNo ratings yet

- CMOS FundamentalsDocument96 pagesCMOS Fundamentalskvxrw7201No ratings yet

- CMOS Fundamentals Part2Document24 pagesCMOS Fundamentals Part2Bck SreedharNo ratings yet

- Vlsi Unit1Document32 pagesVlsi Unit1venkatNo ratings yet

- Engineering Seminar Topics - Seminar Paper - FINFET Technology - Engineering SeminarDocument7 pagesEngineering Seminar Topics - Seminar Paper - FINFET Technology - Engineering SeminarjeshkakkadNo ratings yet

- Seeminar 429 ECE ADocument33 pagesSeeminar 429 ECE AManeesha NidigondaNo ratings yet

- Assignment A1 001 A GIT0723Document14 pagesAssignment A1 001 A GIT0723Shafiq PanicKingNo ratings yet

- VLSI - 16marksDocument44 pagesVLSI - 16marksdheeraj.udaiNo ratings yet

- Application of Diodes Rectifier Circuits Clipper Circuits - PPT Video Online DownloadDocument7 pagesApplication of Diodes Rectifier Circuits Clipper Circuits - PPT Video Online DownloadAlejandroNo ratings yet

- Finfet: Soi and The Non-Planar Finfet DeviceDocument34 pagesFinfet: Soi and The Non-Planar Finfet Devicesandeeppareek926100% (1)

- BASIC VLSI DESIGN .PptsDocument32 pagesBASIC VLSI DESIGN .PptsNarayana Rao RevallaNo ratings yet

- FINFETDocument29 pagesFINFETNMAHESWARA REDDY KAYALA100% (6)

- Ec2254 - Linear Integrated Circuits and Applications: Two Mark Questions and AnswersDocument27 pagesEc2254 - Linear Integrated Circuits and Applications: Two Mark Questions and AnswersarunathangamNo ratings yet

- Ee503 - Ic Fabrication and Packaging TechnologyDocument34 pagesEe503 - Ic Fabrication and Packaging TechnologyPrevenaManiamNo ratings yet

- EC19641-VLSI Design - Part A - Q & ADocument36 pagesEC19641-VLSI Design - Part A - Q & AmyavananNo ratings yet

- Answer KeyDocument28 pagesAnswer KeyKrishnandrk 5577No ratings yet

- Unit-1 / Part-1Document54 pagesUnit-1 / Part-1Andrews austinNo ratings yet

- VLSI Unit 2 Technology - SDocument52 pagesVLSI Unit 2 Technology - SIndrajeet GautamNo ratings yet

- Sic Mos Trench Self Align Micromachines-14-02212Document12 pagesSic Mos Trench Self Align Micromachines-14-02212terry chenNo ratings yet

- VLSI Design TechniquesDocument119 pagesVLSI Design Techniquesrajesh26julyNo ratings yet

- New Reliability Issues of CMOS Transistors With 1.3nm Thick Gate OxideDocument1 pageNew Reliability Issues of CMOS Transistors With 1.3nm Thick Gate OxideRamprasad PoluruNo ratings yet

- Substrate Noise Coupling Analysis in Mixed Signal ICsDocument34 pagesSubstrate Noise Coupling Analysis in Mixed Signal ICsapi-19668941No ratings yet

- Isolation: CMOS Processing TechnologyDocument15 pagesIsolation: CMOS Processing TechnologyAshwani RanaNo ratings yet

- Ec6601 2m Rejinpaul IDocument21 pagesEc6601 2m Rejinpaul IAngelinNo ratings yet

- " Pembumian Sistem Elektronik Frekuensi Tinggi Dan Penerapannya Pada Pusat Data Dan Pemancar " - by Muhamad Harli - MediumDocument41 pages" Pembumian Sistem Elektronik Frekuensi Tinggi Dan Penerapannya Pada Pusat Data Dan Pemancar " - by Muhamad Harli - MediummartonoscribNo ratings yet

- Chapter 5Document30 pagesChapter 5yeshi janexoNo ratings yet

- Finfet TechnologyDocument29 pagesFinfet TechnologyPrajwal GowdaNo ratings yet

- Question AnswerDocument7 pagesQuestion AnswerSaurabh KumarNo ratings yet

- Low Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesDocument6 pagesLow Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesseventhsensegroupNo ratings yet

- 2.what Are The Limitations of Integrated Circuits? 1. 2Document6 pages2.what Are The Limitations of Integrated Circuits? 1. 220EUEE053- MADHUBALAN.SNo ratings yet

- VLSI Lab Viva Questions and Answers 1Document21 pagesVLSI Lab Viva Questions and Answers 1anand_duraiswamyNo ratings yet

- Vlsi Unit-IDocument45 pagesVlsi Unit-Isuneelanubolu7No ratings yet

- Power and Analog Devices Trends, Challenges:: Implant and Thermal Processing ApplicationsDocument4 pagesPower and Analog Devices Trends, Challenges:: Implant and Thermal Processing ApplicationsSergeiNo ratings yet

- CMOS FabricationDocument18 pagesCMOS FabricationkeyareddykarthiNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- 38man OiDocument172 pages38man OiCarlos FrancoNo ratings yet

- Manual Sony 3D Digital HD VideoDocument142 pagesManual Sony 3D Digital HD VideoJosé F. VivesNo ratings yet

- Project 1Document5 pagesProject 1AjithNo ratings yet

- Horizontal Line Parallel To The Ceiling: Technical CharacteristicsDocument2 pagesHorizontal Line Parallel To The Ceiling: Technical CharacteristicsThanosEleftheroudisNo ratings yet

- Fast, Compact and Versatile Industrial RobotDocument2 pagesFast, Compact and Versatile Industrial RobotAlexandru ZdbNo ratings yet

- Part2 Synchronous CountersDocument6 pagesPart2 Synchronous CountersLilya OuarabNo ratings yet

- UNIT V. Microwave Components: Lecture No:-35 (Introduction and Scattering Parameters)Document46 pagesUNIT V. Microwave Components: Lecture No:-35 (Introduction and Scattering Parameters)Sai ReddyNo ratings yet

- Proportional Amplifier PVR: For Reversing DrivesDocument8 pagesProportional Amplifier PVR: For Reversing DrivesNelson Enrique Pimiento SerranoNo ratings yet

- Rev4 (User's Manual)Document119 pagesRev4 (User's Manual)Павел ЗагудалинNo ratings yet

- Instructions Type PV-38M and PV-27M Manually Operated Ground and Test DevicesDocument12 pagesInstructions Type PV-38M and PV-27M Manually Operated Ground and Test DevicessajidkaleemNo ratings yet

- Home Theater Audio Video Receiver RT2500Document22 pagesHome Theater Audio Video Receiver RT2500Polleria HahnchenNo ratings yet

- Absolute and Gauge Pressure Ceraphant PTP31BDocument3 pagesAbsolute and Gauge Pressure Ceraphant PTP31BAntônio PimentaNo ratings yet

- Lab Session 3 Earthing: ObjectiveDocument8 pagesLab Session 3 Earthing: ObjectiveHermain Fayyaz KarimNo ratings yet

- Biosensors: Printed Circuit Board (PCB) Technology For Electrochemical Sensors and Sensing PlatformsDocument16 pagesBiosensors: Printed Circuit Board (PCB) Technology For Electrochemical Sensors and Sensing PlatformsJustformedia JustformediaNo ratings yet

- Inductors Details StudyDocument45 pagesInductors Details StudyTanmay HazraNo ratings yet

- NVP6124 DatasheetDocument127 pagesNVP6124 DatasheetOldman TestNo ratings yet

- Summer Tranning-Evaluation: Indian Telephone Industry Santosh PatelDocument28 pagesSummer Tranning-Evaluation: Indian Telephone Industry Santosh PatelVishal Singh MallNo ratings yet

- WWW Learncbse in Lakhmir Singh Physics Class 10 Solutions Chapter 2Document48 pagesWWW Learncbse in Lakhmir Singh Physics Class 10 Solutions Chapter 2akritiNo ratings yet

- Explosion O002Document4 pagesExplosion O002Merazul IslamNo ratings yet

- S1L2-R1 - Technical Data SheetDocument9 pagesS1L2-R1 - Technical Data Sheetsarahalawa222No ratings yet

- AST3300 Hmi Proface PDFDocument11 pagesAST3300 Hmi Proface PDFDuc LeNo ratings yet

- Single Sideband CommunicationDocument26 pagesSingle Sideband CommunicationJane Erestain BuenaobraNo ratings yet

- Re 29016 2021-03Document24 pagesRe 29016 2021-03Denis KonstantinovNo ratings yet

- Project IdeasDocument1 pageProject Ideasc19138913iNo ratings yet

- Rockmite Transceiver ProjectDocument5 pagesRockmite Transceiver Projectdavid reyesNo ratings yet

- Esd5500E Series Speed Control Unit: Model DescriptionDocument23 pagesEsd5500E Series Speed Control Unit: Model DescriptionEslam MahfouzNo ratings yet

- Product Data: 24ABB3 Baset13 Air Conditioner With Puronr RefrigerantDocument38 pagesProduct Data: 24ABB3 Baset13 Air Conditioner With Puronr RefrigerantMauricioNo ratings yet

- Kertas Penerangan 1Document19 pagesKertas Penerangan 1Amin IqmalNo ratings yet

- 24 LC 64Document12 pages24 LC 64wabp_23No ratings yet

- AUV Electric Propulsion Thrusters: Subsea GroupDocument2 pagesAUV Electric Propulsion Thrusters: Subsea GroupMol MolNo ratings yet