Professional Documents

Culture Documents

54111mtdigital System Design

54111mtdigital System Design

Uploaded by

surya038Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

54111mtdigital System Design

54111mtdigital System Design

Uploaded by

surya038Copyright:

Available Formats

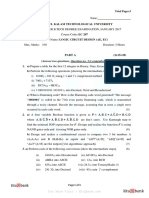

Code No: 54111/MT M.Tech.

I Semester Supplementary Examinations, September, 2008 DIGITAL SYSTEM DESIGN (Common to Digital Systems & Computer Electronics/ Digital Electronics & Communication Systems/ VLSI System Design) Time: 3hours Answer any FIVE questions All questions carry equal marks ---

NR

Max. Marks:60

1.a) Draw the ASM chart to detect the overlapping sequence 1010 from the incoming bit stream and output 1 for each detection. Ex: x: 10101010110- - - - - - Z: 00010101000- - - - - - Implement the controller circuit using MUX method. b) What is the difference between melay and moore state machine. 2.a) b) Draw the general structure of an FPGA and explain how a logicfunction can be realized on FPGA with a simple example. Design and implement a BCD counter on PLD (PLA). Draw the complete fuse-map circuit.

3.a) Using the path sensitization method and Boolean difference method find the test vectors for SAO fault on input line 1 and SA1 Fault on the internal line 2 of the circuit shown below

b) Draw the table giving the set of all possible single struck faults and the faulty and fault-free responses and also construct the fault cover table for the circuit shown in below.

Contd2.,

Code No: 54111/MT 4.a)

::2::

What is the significance of Kohavi Algorithm? Explain how it detects multiple faults in a two-level networks with a simple example. b) Discuss the different types of faults in digital circuits (fault models).

5.a) Find a preset distinguishing experiment that determine the initial state of the machine shown in table given below. Given that it cannot be initially in state E. b) Can you identify the initial state when the initial uncertainity is (ABCDE)? Table Ps Ns, z x=0 , x=1 A B,1 A,1 B E,0 A,1 C A,0 E,1 D C,1 D,1 E E,0 D,1 c) Classify the fault detection experiments for the sequential circuits. 6.a) Find minimized PLA of the following multiple output Boolean functions on a map. Calculate the area and cross point densities of the un -minimized and minimized PLAS. f1 = (2, 4,5, 6, 7,10,14,15) f 2 = (4,5, 7,11,15) Briefly describe about PLA folding.

b)

7.a) Explain the different types of fault models and fault types in a PLA. b) Plot the following PLA on the map. Identify the undetectable faults. Determine a minimal test set for an detectable faults.

x1 x2 x3 x4

0 2 21 2 1 12 0 1 21 8.a)

Z1 Z 2

1 0 1 1 0 1

b)

The output Z of a fundamental-mode , two input sequential circuit is to change from 0 to 1 only when x2 changes from 0 to 1 while x1 =1. The output is to change from 1 to 0 only when x1 changes from 1 to 0 while x2 =1. (i) Find a minimum- row reduced flow table, the output should be fast and flicker-free. (ii) Show a valid assignment and write a set of (static) hazardfree exitation and output equations. Define the races and cycles in sequential circuits. &_&_&_&

You might also like

- POWSD ManualDocument100 pagesPOWSD ManualThai Tran100% (4)

- Digital System Design Question PaperDocument1 pageDigital System Design Question Papermujju433100% (1)

- VMFT Radar ReviewDocument28 pagesVMFT Radar ReviewHoovers RamirezNo ratings yet

- DSD Previous PapersDocument8 pagesDSD Previous Paperssunilreddy2winNo ratings yet

- Rr311901 Digital Systems DesignDocument8 pagesRr311901 Digital Systems DesignSrinivasa Rao GNo ratings yet

- Tutdac 99Document2 pagesTutdac 99baburao_kodavatiNo ratings yet

- M.tech Digital System DesignDocument2 pagesM.tech Digital System DesignsrinivasNo ratings yet

- 9d06101a Digital Systems DesignDocument2 pages9d06101a Digital Systems DesignsubbuNo ratings yet

- WWW Manaresults Co inDocument2 pagesWWW Manaresults Co inNaresh KumarNo ratings yet

- Ap9212 AdsdDocument12 pagesAp9212 AdsdKartheeswaran Arumugam33% (3)

- 6438nr-Digital System DesignDocument2 pages6438nr-Digital System DesignNaresh KumarNo ratings yet

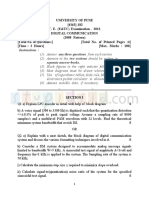

- T.E. - Examination, (Revised) Code:66318: (SemesterDocument3 pagesT.E. - Examination, (Revised) Code:66318: (SemesterSandhya GaikwadNo ratings yet

- Gujarat Technological University: InstructionsDocument26 pagesGujarat Technological University: Instructionsdilawar sumraNo ratings yet

- Te Oct 2014Document149 pagesTe Oct 2014contrasterNo ratings yet

- S T L DDocument12 pagesS T L DMohan Krishna0% (1)

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Monica NareshNo ratings yet

- ELX304 Ref ExamDocument13 pagesELX304 Ref ExamNadeesha Bandara0% (1)

- 2023 Midterm PapersDocument5 pages2023 Midterm Papers40 XII-B Satyam SinhaNo ratings yet

- Rr210203 Switching Theory and Logic DesignDocument9 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao GNo ratings yet

- Answer All Questions PART A - (5 2 10)Document3 pagesAnswer All Questions PART A - (5 2 10)Anonymous NV7nnJDeNo ratings yet

- Electronics and Communication Engineering VI SemesterDocument2 pagesElectronics and Communication Engineering VI SemesterRamNo ratings yet

- Logic CircuitsDocument2 pagesLogic CircuitsRaman yadavNo ratings yet

- STLD 2009 RegularDocument4 pagesSTLD 2009 RegularrangerNo ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- Logic Circuits 2012 FallDocument2 pagesLogic Circuits 2012 FallSimant ChaudharyNo ratings yet

- DSP Integrated Circuits 4Document3 pagesDSP Integrated Circuits 4brindkowsiNo ratings yet

- 4C Reports: Introduction To Labview & Ni-Usrp (C1)Document3 pages4C Reports: Introduction To Labview & Ni-Usrp (C1)Cyrille MagdiNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- DC Dec 16Document2 pagesDC Dec 16SAURABH BHISENo ratings yet

- Continuous Assessement: 2019/2020 Academic Year: Course Title: Digital Control Systems. Course Code: Eeep3201Document3 pagesContinuous Assessement: 2019/2020 Academic Year: Course Title: Digital Control Systems. Course Code: Eeep3201Danny JrNo ratings yet

- Rr311202 Communication TheoryDocument8 pagesRr311202 Communication TheorySrinivasa Rao G100% (1)

- Question Bank - ADSD ET7101Document7 pagesQuestion Bank - ADSD ET7101karthikamageshNo ratings yet

- 113BU032016Document2 pages113BU032016mushahedNo ratings yet

- 13A04502 Digital Communication SystemsDocument1 page13A04502 Digital Communication SystemsMallikarjuna Rao YamarthyNo ratings yet

- Ec302 ADocument2 pagesEc302 AJazir HameedNo ratings yet

- Subject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeeDocument16 pagesSubject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeePavithra ManiNo ratings yet

- EE8351 Iq 16 Marks PDFDocument7 pagesEE8351 Iq 16 Marks PDFdeepika senthilNo ratings yet

- Answer Two Questions, Question No. 3 Is CompulsoryDocument3 pagesAnswer Two Questions, Question No. 3 Is CompulsoryABHILESH G KNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- Rr210203 Switching Theory and Logic DesignDocument8 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao G100% (2)

- Previous Year Paper Digital Logic DesignDocument1 pagePrevious Year Paper Digital Logic DesignShivanshu Kumar UpadhyayNo ratings yet

- Guessing Papers 1-2-12th Electronics Sub Code C2Document6 pagesGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922No ratings yet

- Ec 1202 Digital System DesignDocument8 pagesEc 1202 Digital System DesignworkubNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Digital Communications (DCOM)Document4 pagesDigital Communications (DCOM)Mamotete MohohloNo ratings yet

- NR 311901 Digital Systems DesignDocument5 pagesNR 311901 Digital Systems DesignSrinivasa Rao GNo ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- B.Tech. Theory Examination (Sem-Viii) 2016-17 Electronic SwitchingDocument1 pageB.Tech. Theory Examination (Sem-Viii) 2016-17 Electronic SwitchingDeepak Kumar100% (1)

- HWDocument3 pagesHWAurongo NasirNo ratings yet

- A G1002 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesA G1002 Pages: 2: Answer Any Two Full Questions, Each Carries 15 MarksAdithyan JNo ratings yet

- Block Coder/decoder:: T T New T New TDocument3 pagesBlock Coder/decoder:: T T New T New TAurongo NasirNo ratings yet

- 15A04502 Digital Communication Systems (1) - 1Document1 page15A04502 Digital Communication Systems (1) - 117BF1A04L7 kalyanNo ratings yet

- Electrochemical Processes in Biological SystemsFrom EverandElectrochemical Processes in Biological SystemsAndrzej LewenstamNo ratings yet

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsFrom EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikNo ratings yet

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Electronic Systems: Study Topics in Physics Book 8From EverandElectronic Systems: Study Topics in Physics Book 8Rating: 5 out of 5 stars5/5 (1)

- JNTUH Syllabus 2013 M.tech Communication SysDocument26 pagesJNTUH Syllabus 2013 M.tech Communication SysSRINIVASA RAO GANTANo ratings yet

- JNTUH MCA Syllabus 2013Document107 pagesJNTUH MCA Syllabus 2013SRINIVASA RAO GANTANo ratings yet

- JNTUH M.TECH PEDS 2013 SyllabusDocument24 pagesJNTUH M.TECH PEDS 2013 SyllabusSRINIVASA RAO GANTA100% (1)

- JNTUH MBA Course Structure and Syllabus 2013Document80 pagesJNTUH MBA Course Structure and Syllabus 2013SRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 M.Tech EPSDocument23 pagesJNTUH Syllabus 2013 M.Tech EPSSRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 M.Tech CSEDocument33 pagesJNTUH Syllabus 2013 M.Tech CSESRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 Civil Engg Course StructureDocument2 pagesJNTUH Syllabus 2013 Civil Engg Course StructureSRINIVASA RAO GANTANo ratings yet

- Paper-I Set-WDocument16 pagesPaper-I Set-WKaran AggarwalNo ratings yet

- Library Quality Criteria For NBA AccreditationDocument3 pagesLibrary Quality Criteria For NBA AccreditationSRINIVASA RAO GANTA100% (6)

- Kvs Librarypolicy2012Document59 pagesKvs Librarypolicy2012SRINIVASA RAO GANTANo ratings yet

- Guidelines For Open Educational Resources (OER) in Higher EducationDocument27 pagesGuidelines For Open Educational Resources (OER) in Higher EducationSRINIVASA RAO GANTANo ratings yet

- IP Addresses and SubnettingDocument16 pagesIP Addresses and SubnettingHusnainNo ratings yet

- Librarian Is Teaching or Non TeachingDocument1 pageLibrarian Is Teaching or Non TeachingSRINIVASA RAO GANTANo ratings yet

- Vbit Journals 2011-12Document6 pagesVbit Journals 2011-12SRINIVASA RAO GANTANo ratings yet

- Reg Pay Degree 020110Document16 pagesReg Pay Degree 020110SRINIVASA RAO GANTANo ratings yet

- Ready Reckoner Radar EwDocument27 pagesReady Reckoner Radar EwSRINIVASA RAO GANTANo ratings yet

- Code - No: 25042: Freespace Guide CutoffDocument8 pagesCode - No: 25042: Freespace Guide CutoffSRINIVASA RAO GANTANo ratings yet

- Dspace On WindowsDocument15 pagesDspace On WindowsSRINIVASA RAO GANTANo ratings yet

- NET EXAM Paper 1Document27 pagesNET EXAM Paper 1shahid ahmed laskar100% (4)

- r05011801 Metallurgical AnalysisDocument4 pagesr05011801 Metallurgical AnalysisSRINIVASA RAO GANTANo ratings yet

- Code No: 25079Document8 pagesCode No: 25079SRINIVASA RAO GANTANo ratings yet

- Code No: 25056Document8 pagesCode No: 25056SRINIVASA RAO GANTANo ratings yet

- Rr322105-High Speed AerodynamicsDocument8 pagesRr322105-High Speed AerodynamicsSRINIVASA RAO GANTANo ratings yet

- Code No: 25022Document4 pagesCode No: 25022SRINIVASA RAO GANTANo ratings yet

- Rr322305 ImmunologyDocument4 pagesRr322305 ImmunologySRINIVASA RAO GANTANo ratings yet

- Code No: 35051Document8 pagesCode No: 35051SRINIVASA RAO GANTANo ratings yet

- Code No: 35060Document4 pagesCode No: 35060SRINIVASA RAO GANTANo ratings yet

- r05311902 Computer GraphicsDocument4 pagesr05311902 Computer GraphicsSRINIVASA RAO GANTANo ratings yet

- Exp 04Document6 pagesExp 04ganga_ch1No ratings yet

- Analysis of Boost ConverterDocument3 pagesAnalysis of Boost ConverterPraveenNo ratings yet

- Window Utitlization Factor KuDocument4 pagesWindow Utitlization Factor KuJavierNo ratings yet

- Totem-Pole Paper - 0Document9 pagesTotem-Pole Paper - 0wartchev39No ratings yet

- Avr R448 (Leroy Sommer)Document4 pagesAvr R448 (Leroy Sommer)Ilyas Rangga RamadhanNo ratings yet

- Case Expension - LVDT SensorDocument6 pagesCase Expension - LVDT Sensortrung2iNo ratings yet

- Optical Fiber Communication (EEE 4175) : Introduction and Course OverviewDocument40 pagesOptical Fiber Communication (EEE 4175) : Introduction and Course OverviewSaikat Mahmud100% (1)

- Eflux Ax21000Document28 pagesEflux Ax21000Manuel “Mevch” vNo ratings yet

- 05 Chapter 03 LFSIMDocument97 pages05 Chapter 03 LFSIMarunathangamNo ratings yet

- Design For Testability (DFT) : Vlsi Ii: Design of Very Large Scale Integration CircuitsDocument22 pagesDesign For Testability (DFT) : Vlsi Ii: Design of Very Large Scale Integration CircuitsSiam HasanNo ratings yet

- Parallel Ups SystemsDocument10 pagesParallel Ups SystemsShameel PtNo ratings yet

- AD603Document24 pagesAD603Vu Huy LongNo ratings yet

- BXEDocument79 pagesBXEAnkita WankhadeNo ratings yet

- Lesson 3: The FDE Cycle: KS4 - Computer SystemsDocument15 pagesLesson 3: The FDE Cycle: KS4 - Computer SystemsWilliam GreyNo ratings yet

- IBM System Storage N Series Introduction and Planning Guide - Ga32054325Document338 pagesIBM System Storage N Series Introduction and Planning Guide - Ga32054325akramh2No ratings yet

- Basic ElectronicsDocument126 pagesBasic ElectronicsFarazNo ratings yet

- Mini Presentation FileDocument21 pagesMini Presentation FileregasaNo ratings yet

- Simple Fire Alarm CircuitDocument2 pagesSimple Fire Alarm CircuitReneo Remigoso50% (2)

- PhilNITS Quiz BowlDocument22 pagesPhilNITS Quiz Bowlfujitsu_07No ratings yet

- SONY KDL-40X3500 KDL-46X3500 KDL-52X3500 - Chassis - Fix2 PDFDocument256 pagesSONY KDL-40X3500 KDL-46X3500 KDL-52X3500 - Chassis - Fix2 PDFboroda2410No ratings yet

- MACF - Memory Address Content Forgery (Eric A. Schulman)Document11 pagesMACF - Memory Address Content Forgery (Eric A. Schulman)Eric A. SchulmanNo ratings yet

- Circuits Electronics: Introduction and Lumped Circuit AbstractionDocument24 pagesCircuits Electronics: Introduction and Lumped Circuit AbstractionRaghav100% (1)

- 800-01951-C PW-6000 Two-Reader Module Installation GuideDocument29 pages800-01951-C PW-6000 Two-Reader Module Installation Guidejosepalacio30No ratings yet

- JMX568 Data Sheet Ver A2Document13 pagesJMX568 Data Sheet Ver A2Anonymous o2N2OMhUBd100% (1)

- Internal Architecture of 89C52Document24 pagesInternal Architecture of 89C52Anjali KamlapureNo ratings yet

- ICT Grade 7Document20 pagesICT Grade 7Mendis SteaveNo ratings yet

- 93104v00 RF Whitepaper-FinalDocument11 pages93104v00 RF Whitepaper-FinalSrinivas CharyNo ratings yet

- WWW - Use.co - TH - Downloads - GST (Fire Master BROCHUREDocument24 pagesWWW - Use.co - TH - Downloads - GST (Fire Master BROCHURECiba ModiNo ratings yet