Professional Documents

Culture Documents

6438nr-Digital System Design

Uploaded by

Naresh KumarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

6438nr-Digital System Design

Uploaded by

Naresh KumarCopyright:

Available Formats

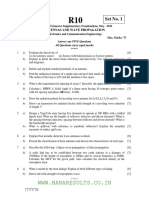

Code No: A5701

NR

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

M.Tech I Semester Examinations, October/November-2011

DIGITAL SYSTEM DESIGN

(VLSI STSTEM DESIGN)

Time: 3hours Max. Marks: 60

Answer any five questions

All questions carry equal marks

---

1.a) Draw an ASM chart to design a control logic of a binary multiplier.

b) Realize the above design using MUX, decoder and D-type flip flops. [12]

2.a) Draw the general structure of a CPLD and explain how a logic function can be

realized on CPLD with simple example.

b) Design a four-way traffic light controller that will keep traffic moving efficiently

along two busy streets that intersect. Implement the controller using PALs. [12]

3.a) Using the path-sensitization method and Boolean difference method find the test

vectors for SA0 fault on input line 1 and SA1 fault on the internal line 2 of the

circuit shown in figure 1.

figure 1

b) Explain how Kohavi algorithm is useful in the detection of faults in digital

circuits. [12]

4.a) Apply D-algorithm to detect SA0 fault at point ‘h’ in the given circuit shown in

figure 2 and derive the test vectors.

figure 2

b) Apply signature analysis to the above circuit and generate the signatures using

4-bit LFSR with a feed back from 3rd flip flop. [12]

5.a) Distinguish between Mealy and Moore machines.

b) Convert the following Mealy machine into a corresponding Moore machine.

[12]

Contd….2

::2::

Machine 1

Ps Ns, Z

X=0 X=1

A B,0 D,0

B A,0 B,0

C D,1 A,0

D D,1 C,0

6.a) Apply PLA maximization procedure and obtain the minimized expression to be

implemented on PLA. F = 2021+0022+1200

b) Obtain the minimum test vector set for the above function ‘F’ in question 6 (a).

[12]

7.a) Explain the different types of fault models and fault types in a PLA.

b) Plot the following PLA on the map. Identify the undetectable faults. Determine a

minimal test set for detectable faults. [12]

x1 x2 x3 x4 Z1 Z2

0 2 2 1 1 0

2 1 1 2 1 1

0 1 2 1 0 1

8.a) The output Z of a fundamental-mode, two input sequential circuit is to change

from 0 to 1 only when 2x changes from 0 to 1 while1x=1. The output is to change

from 1 to 0 only when 1x changes from 1 to 0 while 2x=1.

(i) Find a minimum-row reduced flow table, the output should be fast and flicker-

free.

(ii) Show a valid assignment and write a set of (static) hazard-free excitation and

output equations.

b) Define the races and cycles in sequential circuits. [12]

******

You might also like

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- A0601-Digital System Design - 2Document6 pagesA0601-Digital System Design - 2LaxmiPrasad KonchaNo ratings yet

- DSD Previous PapersDocument8 pagesDSD Previous Paperssunilreddy2winNo ratings yet

- 54111-mt - Digital System DesignDocument2 pages54111-mt - Digital System DesignSRINIVASA RAO GANTANo ratings yet

- Digital System Design Question PaperDocument1 pageDigital System Design Question Papermujju433100% (1)

- Tutdac 99Document2 pagesTutdac 99baburao_kodavatiNo ratings yet

- 9d06101a Digital Systems DesignDocument2 pages9d06101a Digital Systems DesignsubbuNo ratings yet

- 3.MDL 2 DLCDocument3 pages3.MDL 2 DLCVINOD KUMAR.J.R MEC-AP/AERONo ratings yet

- Rr311901 Digital Systems DesignDocument8 pagesRr311901 Digital Systems DesignSrinivasa Rao GNo ratings yet

- M.tech Digital System DesignDocument2 pagesM.tech Digital System DesignsrinivasNo ratings yet

- DSD Model Paper 1Document7 pagesDSD Model Paper 1VigneshNo ratings yet

- DSD Model Paper 2Document8 pagesDSD Model Paper 2VigneshNo ratings yet

- 07a4ec09 STLDDocument6 pages07a4ec09 STLDSRINIVASA RAO GANTANo ratings yet

- Smart Materials, Sensors and ActuatorsDocument2 pagesSmart Materials, Sensors and ActuatorsmanojNo ratings yet

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiNo ratings yet

- DSD_JanFeb2018Document2 pagesDSD_JanFeb2018rocky dNo ratings yet

- Switching Theory and Logic Design QuestionsDocument8 pagesSwitching Theory and Logic Design QuestionsvasuvlsiNo ratings yet

- Term End Examination VLSI DesignDocument6 pagesTerm End Examination VLSI DesignSujeet KumarNo ratings yet

- 113BU032016Document2 pages113BU032016mushahedNo ratings yet

- AllDocument57 pagesAllKhondoker Razzakul HaqueNo ratings yet

- Operations Research Jan 2023Document12 pagesOperations Research Jan 2023gunas4767No ratings yet

- Advanced Optimization TechniquesDocument2 pagesAdvanced Optimization TechniquesIbmWasuserNo ratings yet

- Aditya College of EngineeringDocument2 pagesAditya College of EngineeringkarnamittapalliNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Electronic Instrumentation Measurements Kec057Document2 pagesElectronic Instrumentation Measurements Kec057childhoodtoons81No ratings yet

- Digital Signal ProcessingDocument2 pagesDigital Signal ProcessingSreedeviRajithaNo ratings yet

- See Adld 2020Document2 pagesSee Adld 20201ms21ec132No ratings yet

- Switching Theory and Logic Design Exam QuestionsDocument4 pagesSwitching Theory and Logic Design Exam QuestionsrangerNo ratings yet

- Btech Cs 5 Sem Design and Analysis of Algorithm Rcs502 2022Document1 pageBtech Cs 5 Sem Design and Analysis of Algorithm Rcs502 2022YASH GARGNo ratings yet

- Question Paper Sep 2009Document3 pagesQuestion Paper Sep 2009Vignesh MuruganNo ratings yet

- Comp SC 18Document8 pagesComp SC 18Masiur RahamanNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Monica NareshNo ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- CD 5291 Computer Aided Tools For ManufactiringDocument2 pagesCD 5291 Computer Aided Tools For ManufactiringGnaneswaran Narayanan63% (8)

- RRASE COLLEGE MODEL EXAM DESIGN ANALYSIS ALGORITHMDocument2 pagesRRASE COLLEGE MODEL EXAM DESIGN ANALYSIS ALGORITHMkarthick VijayanNo ratings yet

- T.E (2019 Pattern)Document852 pagesT.E (2019 Pattern)Shubham SagarNo ratings yet

- GATE 2015 COMPUTER SCIENCE QUESTIONS AND ANSWERSDocument12 pagesGATE 2015 COMPUTER SCIENCE QUESTIONS AND ANSWERSPooja SinhaNo ratings yet

- Cambridge University - Computer Science Tripos - y2023PAPER2Document10 pagesCambridge University - Computer Science Tripos - y2023PAPER2GtrendsCE Account0% (1)

- Unit-1-2-3 Question Bank DEC 2131004Document2 pagesUnit-1-2-3 Question Bank DEC 2131004Amit KumarNo ratings yet

- Switching Theory and Logic DesignDocument6 pagesSwitching Theory and Logic DesignVijay MNo ratings yet

- Rr210203 Switching Theory and Logic DesignDocument9 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao GNo ratings yet

- Information Theory Coding Kec075Document2 pagesInformation Theory Coding Kec075xefedoy533No ratings yet

- DesignandAnalysisofAlgorithms March2019 M SC Withcredits RegularJune-2017PatternM ScPart-I D7DEF24FDocument2 pagesDesignandAnalysisofAlgorithms March2019 M SC Withcredits RegularJune-2017PatternM ScPart-I D7DEF24FRizwan AhemadNo ratings yet

- Hoursl:: Computii (G (I/Eural Logic Ai (D Gei/Etic Algorithm) (Totalmarks:Lq0Document3 pagesHoursl:: Computii (G (I/Eural Logic Ai (D Gei/Etic Algorithm) (Totalmarks:Lq0abhishekNo ratings yet

- CSS 22531-2023-Summer-question-paper EGDocument4 pagesCSS 22531-2023-Summer-question-paper EGrushikarande0024No ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- 2018-OE(CS)802D-Operation-ResearchDocument5 pages2018-OE(CS)802D-Operation-Researchvmandal.cr7No ratings yet

- Electronics and Communication Engineering VI SemesterDocument2 pagesElectronics and Communication Engineering VI SemesterRamNo ratings yet

- S T L DDocument12 pagesS T L DMohan Krishna0% (1)

- rr311303 Operations ResearchDocument9 pagesrr311303 Operations ResearchSRINIVASA RAO GANTA100% (1)

- Digital Logic Design Model Question PaperDocument2 pagesDigital Logic Design Model Question PaperWINORLOSENo ratings yet

- Digital Signal Processing Lab ECLR-51 Dept. of Electronics & Communication EngineeringDocument48 pagesDigital Signal Processing Lab ECLR-51 Dept. of Electronics & Communication Engineeringrachit websitesNo ratings yet

- Digital Logic Design (Jntu - Uandistar.org)Document4 pagesDigital Logic Design (Jntu - Uandistar.org)Arepalli SathibabuNo ratings yet

- Digital Differential Analysers: International Series of Monographs on Electronics and InstrumentationFrom EverandDigital Differential Analysers: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- Social Systems Engineering: The Design of ComplexityFrom EverandSocial Systems Engineering: The Design of ComplexityCésar García-DíazNo ratings yet

- RGPV EE/EX-7103 (GS) SCADA Systems and Applications Past PaperDocument1 pageRGPV EE/EX-7103 (GS) SCADA Systems and Applications Past PaperNaresh KumarNo ratings yet

- SCADA Systems Components and ApplicationsDocument1 pageSCADA Systems Components and ApplicationsNaresh KumarNo ratings yet

- 19ecs431 - Embedded SystemsDocument18 pages19ecs431 - Embedded SystemsNaresh KumarNo ratings yet

- HAVANA Brochure 1 FinalDocument12 pagesHAVANA Brochure 1 FinalNaresh KumarNo ratings yet

- Scheme - I Sample Question PaperDocument4 pagesScheme - I Sample Question PaperNaresh KumarNo ratings yet

- JNTU MTech Course on SCADA SystemsDocument2 pagesJNTU MTech Course on SCADA SystemsNaresh KumarNo ratings yet

- JNTU ANANTAPUR - 2016 - 9A04701 Embedded Real Time Operating SystemsDocument1 pageJNTU ANANTAPUR - 2016 - 9A04701 Embedded Real Time Operating SystemsNaresh KumarNo ratings yet

- JNTU Kakinada - M.Tech - EMBEDDED REAL TIME OPERATING SYSTEMSDocument7 pagesJNTU Kakinada - M.Tech - EMBEDDED REAL TIME OPERATING SYSTEMSNaresh KumarNo ratings yet

- Memory TechnologiesDocument1 pageMemory TechnologiesNaresh KumarNo ratings yet

- Criterion 3 UG NBADocument39 pagesCriterion 3 UG NBANaresh KumarNo ratings yet

- Microcontroller and ApplicationsDocument4 pagesMicrocontroller and ApplicationsNaresh KumarNo ratings yet

- JNTUK - M Tech - 2017 - 2nd Semester-H6810052017 SEMICONDUCTOR MEMORY DESIGN AND TESTINGDocument1 pageJNTUK - M Tech - 2017 - 2nd Semester-H6810052017 SEMICONDUCTOR MEMORY DESIGN AND TESTINGNaresh KumarNo ratings yet

- CVDocument11 pagesCVNaresh KumarNo ratings yet

- IoT Lesson PlanDocument2 pagesIoT Lesson PlanNaresh KumarNo ratings yet

- Lica 1 MarkDocument6 pagesLica 1 MarkNaresh KumarNo ratings yet

- Project Expo PosterDocument1 pageProject Expo PosterNaresh KumarNo ratings yet

- Malla Reddy Engineering College: B. Tech. Iv Semester (Mr15) Regular End ExaminationsDocument2 pagesMalla Reddy Engineering College: B. Tech. Iv Semester (Mr15) Regular End ExaminationsNaresh KumarNo ratings yet

- Triple DES Using 3 Key MethodDocument3 pagesTriple DES Using 3 Key MethodNaresh KumarNo ratings yet

- GITAM ECE Electromagnetic Waves AssignmentsDocument3 pagesGITAM ECE Electromagnetic Waves AssignmentsNaresh KumarNo ratings yet

- CV 2 MarksDocument9 pagesCV 2 MarksNaresh KumarNo ratings yet

- Antennas and Wave Propagation Exam QuestionsDocument1 pageAntennas and Wave Propagation Exam QuestionsNaresh KumarNo ratings yet

- MR15 B.Tech IV Semester Electromagnetic Theory and Transmission Lines ExamDocument2 pagesMR15 B.Tech IV Semester Electromagnetic Theory and Transmission Lines ExamNaresh KumarNo ratings yet

- M.Tech. Degree Examination Embedded Systems: (EPRES 233)Document2 pagesM.Tech. Degree Examination Embedded Systems: (EPRES 233)Naresh KumarNo ratings yet

- AWP Question Paper2 2016Document1 pageAWP Question Paper2 2016Naresh KumarNo ratings yet

- Eec207: Electromagnetic Waves L T P C 3 1 0 4Document2 pagesEec207: Electromagnetic Waves L T P C 3 1 0 4Naresh KumarNo ratings yet

- EMW QuizDocument7 pagesEMW QuizNaresh Kumar100% (3)

- AWP Question Paper 2015Document4 pagesAWP Question Paper 2015Naresh KumarNo ratings yet

- AWP Question Paper 2016Document1 pageAWP Question Paper 2016Naresh KumarNo ratings yet

- 5844nr-Real Time Operating Systems For Embedded SystemsDocument1 page5844nr-Real Time Operating Systems For Embedded SystemsNaresh KumarNo ratings yet

- Suzanne Saroff - Year 9 Exam AnnaDocument1 pageSuzanne Saroff - Year 9 Exam Annaapi-569107627No ratings yet

- Download Risc V Assembly Language Programming Stephen Smith all chapterDocument67 pagesDownload Risc V Assembly Language Programming Stephen Smith all chapteralec.powell515100% (4)

- 14EIT72 Instrumentation System Design UNIT-V - P&I Diagrams and Instrument InstallationDocument38 pages14EIT72 Instrumentation System Design UNIT-V - P&I Diagrams and Instrument Installationksjanarthanan_sriNo ratings yet

- DPR TemplateDocument74 pagesDPR TemplateAnupamPanja0% (1)

- Why Astrology Is Science: Five Good Reasons: Tapan Das, PH.D., P.EngDocument56 pagesWhy Astrology Is Science: Five Good Reasons: Tapan Das, PH.D., P.EngNikhil TidkeNo ratings yet

- Summed Area TablesDocument29 pagesSummed Area TablesDhillonvNo ratings yet

- Peritoneal DialysisDocument26 pagesPeritoneal DialysisKath LeenNo ratings yet

- CS8603 Distributed SystemsDocument11 pagesCS8603 Distributed SystemsMohammad Bilal - Asst. Prof, Dept. of CSENo ratings yet

- Lightweight AP - Registration To WLC PDFDocument15 pagesLightweight AP - Registration To WLC PDFAnasham TegegnNo ratings yet

- Water Pressure Grid TutorialDocument17 pagesWater Pressure Grid Tutorialrrj44No ratings yet

- Karmaveer Bhaurao Patil Polytechnic, Satara: Control ActionsDocument104 pagesKarmaveer Bhaurao Patil Polytechnic, Satara: Control Actionsmohammd imran azizNo ratings yet

- Agile Testing Methods Guide: Scrum, Crystal, DSDM, FDD, Lean, XP & MoreDocument19 pagesAgile Testing Methods Guide: Scrum, Crystal, DSDM, FDD, Lean, XP & Moreangelica campuedNo ratings yet

- (BPL12-12FR) : VRLA Rechargeable BatteryDocument1 page(BPL12-12FR) : VRLA Rechargeable BatteryAlexander PischulinNo ratings yet

- Application OF Horizontal Vacuum: THE A Belt Filter TO Smuts Dewatering and Cane Mud FiltrationDocument5 pagesApplication OF Horizontal Vacuum: THE A Belt Filter TO Smuts Dewatering and Cane Mud FiltrationMichel M.No ratings yet

- Ansi B36.19Document13 pagesAnsi B36.19BimaNo ratings yet

- Electric and water requirements for concrete batch plantDocument8 pagesElectric and water requirements for concrete batch plantWael WaelNo ratings yet

- RecoverPoint With SRMDocument63 pagesRecoverPoint With SRMhemanth-07No ratings yet

- British Royal Yachts Historical BackgroundDocument9 pagesBritish Royal Yachts Historical BackgroundFelipe Andrés Reinal AranedaNo ratings yet

- 1 Gravity IntroductionDocument13 pages1 Gravity IntroductionPerry SegereNo ratings yet

- K-Gamma and K-Beta FunctionDocument5 pagesK-Gamma and K-Beta FunctionketashiNo ratings yet

- Purchase Specification FOR 1250A, 1000V, DC CONTACTOR FOR Oil Rig ApplicationDocument5 pagesPurchase Specification FOR 1250A, 1000V, DC CONTACTOR FOR Oil Rig ApplicationAhmed ShaabanNo ratings yet

- Chapter 3.1.3Document69 pagesChapter 3.1.300.wonderer.00No ratings yet

- C Language Basic Programs Which Used For BigginnersDocument112 pagesC Language Basic Programs Which Used For BigginnersRavikumar VendiNo ratings yet

- Classical Mechanics Motion Under Central ForcesDocument16 pagesClassical Mechanics Motion Under Central Forcessudipta paulNo ratings yet

- Diffusion Mass TransferDocument18 pagesDiffusion Mass TransferbhuniakanishkaNo ratings yet

- Thermodynamic and transport properties of saturated steam and waterDocument26 pagesThermodynamic and transport properties of saturated steam and waterMuhammad Reza FahleviNo ratings yet

- Microsurfaces: The Role of Apis in A Microservice ArchitectureDocument11 pagesMicrosurfaces: The Role of Apis in A Microservice ArchitectureSai CharanNo ratings yet

- Maxwell's Equations ExplainedDocument347 pagesMaxwell's Equations ExplainedFabri ChevalierNo ratings yet

- FM DemodulationDocument4 pagesFM DemodulationRudra Pratap SinghNo ratings yet