Professional Documents

Culture Documents

Data Sheet P Channel FET

Uploaded by

Michael McDonaldOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Data Sheet P Channel FET

Uploaded by

Michael McDonaldCopyright:

Available Formats

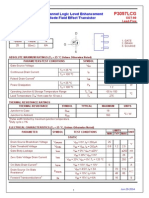

NIKO-SEM

P-Channel Logic Level Enhancement

Mode Field Effect Transistor

P06P03LVG

SOP-8 Lead-Free

D

PRODUCT SUMMARY V(BR)DSS -30 RDS(ON) 45m ID -6A 4 :GATE 5,6,7,8 :DRAIN 1,2,3 :SOURCE

G S

ABSOLUTE MAXIMUM RATINGS (TC = 25 C Unless Otherwise Noted) PARAMETERS/TEST CONDITIONS Drain-Source Voltage Gate-Source Voltage Continuous Drain Current Pulsed Drain Current Power Dissipation

1

SYMBOL VDS VGS

LIMITS -30 20 -6 -5 -30 2.5 1.3 -55 to 150

UNITS V V

TC = 25 C TC = 70 C TC = 25 C TC = 70 C

ID IDM PD Tj, Tstg

Operating Junction & Storage Temperature Range THERMAL RESISTANCE RATINGS THERMAL RESISTANCE Junction-to-Case Junction-to-Ambient

1 2

C UNITS C / W C / W

SYMBOL RJc RJA

TYPICAL

MAXIMUM 25 50

Pulse width limited by maximum junction temperature. Duty cycle 1% ELECTRICAL CHARACTERISTICS (TC = 25 C, Unless Otherwise Noted) PARAMETER SYMBOL TEST CONDITIONS STATIC Drain-Source Breakdown Voltage Gate Threshold Voltage Gate-Body Leakage Zero Gate Voltage Drain Current On-State Drain Current1 Drain-Source On-State Resistance1 Forward Transconductance1 V(BR)DSS VGS(th) IGSS IDSS ID(ON) RDS(ON) gfs VGS = 0V, ID = -250A VDS = VGS, ID = -250A VDS = 0V, VGS = 20V VDS = -24V, VGS = 0V VDS = -20V, VGS = 0V, TJ = 125 C VDS = -5V, VGS = -10V VGS = -4.5V, ID =- 5A VGS = -10V, ID = -6A VDS = -10V, ID = -6A -30 60 37 16 75 45 -30 -0.9 -1.5 -3 V LIMITS UNIT MIN TYP MAX

100 nA 1 10 A A m S

JUN-10-2004 1

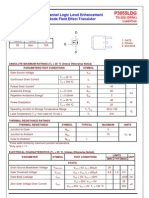

NIKO-SEM

P-Channel Logic Level Enhancement

Mode Field Effect Transistor

P06P03LVG

SOP-8 Lead-Free

DYNAMIC Input Capacitance Output Capacitance Reverse Transfer Capacitance Total Gate Charge

2

Ciss Coss Crss Qg Qgs Qgd

2

530 VGS = 0V, VDS = -15V, f = 1MHz 135 70 10 VDS = 0.5V(BR)DSS, VGS = -10V, ID = -6A 2.2 2 5.7 VDS = -15V, RL = 1 ID -1A, VGS = -10V, RGS = 6 10 18 5 nS 14 nC pF

Gate-Source Charge2 Gate-Drain Charge

2 2 2

Turn-On Delay Time Rise Time

td(on) tr td(off) tf

Turn-Off Delay Time Fall Time2

SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICS (TC = 25 C) Continuous Current Pulsed Current3 Forward Voltage1 Reverse Recovery Time Reverse Recovery Charge

1 2

IS ISM VSD trr Qrr IF = -1A, VGS = 0V IF = -5A, dlF/dt = 100A / S 15.5 7.9

-2.1 -4 -1.2

A V nS nC

Pulse test : Pulse Width 300 sec, Duty Cycle 2. Independent of operating temperature. 3 Pulse width limited by maximum junction temperature. REMARK: THE PRODUCT MARKED WITH P06P03LVG, DATE CODE or LOT # Orders for parts with Lead-Free plating can be placed using the PXXXXXXXG parts name.

JUN-10-2004 2

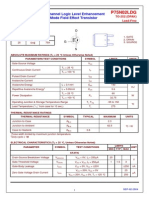

NIKO-SEM

P-Channel Logic Level Enhancement

Mode Field Effect Transistor

P06P03LVG

SOP-8 Lead-Free

Typical Characteristics

JUN-10-2004 3

NIKO-SEM

P-Channel Logic Level Enhancement

Mode Field Effect Transistor

P06P03LVG

SOP-8 Lead-Free

JUN-10-2004 4

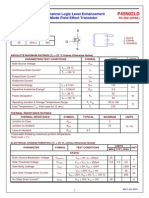

NIKO-SEM

P-Channel Logic Level Enhancement

Mode Field Effect Transistor

P06P03LVG

SOP-8 Lead-Free

SOIC-8 (D) MECHANICAL DATA

mm Min. 4.8 3.8 5.8 0.38 Typ. 4.9 3.9 6.0 0.445 1.27 1.35 0.1 1.55 0.175 1.75 0.25 Max. 5.0 4.0 6.2 0.51 mm Min. 0.5 0.18 Typ. 0.715 0.254 0.22 0 4 8 Max. 0.83 0.25

Dimension A B C D E F G

Dimension H I J K L M N

JUN-10-2004 5

You might also like

- Niko - p07d03lvgDocument5 pagesNiko - p07d03lvgTininha MachadoNo ratings yet

- Data Sheet - P3057LCG PDFDocument4 pagesData Sheet - P3057LCG PDFAdrian RouxNo ratings yet

- p3055ldg - Source Drain Diode - HPDocument4 pagesp3055ldg - Source Drain Diode - HParthurcofnNo ratings yet

- 3055 DatasheetDocument4 pages3055 DatasheetiuriepaliiNo ratings yet

- p75n02ldg - PDF MosfetDocument3 pagesp75n02ldg - PDF Mosfetindavi100% (1)

- N-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesN-Channel Enhancement Mode MOSFET: Product SummaryTony RodriguesNo ratings yet

- Advanced Power Electronics Corp.: AP4513GHDocument7 pagesAdvanced Power Electronics Corp.: AP4513GHqueequeg73No ratings yet

- P2103NV Niko-Sem: N-& P-Channel Enhancement Mode Field Effect TransistorDocument8 pagesP2103NV Niko-Sem: N-& P-Channel Enhancement Mode Field Effect TransistorMohamed SaiedNo ratings yet

- Advanced Power Electronics Corp.: AP4525GEMDocument7 pagesAdvanced Power Electronics Corp.: AP4525GEMsontuyet82No ratings yet

- Nikos p2003bdgDocument5 pagesNikos p2003bdgjavierrincon800No ratings yet

- PD1503YVS: Dual N-Channel Enhancement Mode MOSFETDocument7 pagesPD1503YVS: Dual N-Channel Enhancement Mode MOSFETAldemir Fernando BattagliaNo ratings yet

- P2003BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 pagesP2003BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorMahmoued YasinNo ratings yet

- Data Sheet P2804BDGDocument5 pagesData Sheet P2804BDGsantiagobjNo ratings yet

- Niko-Sem: Dual N-Channel Enhancement Mode Field Effect TransistorDocument7 pagesNiko-Sem: Dual N-Channel Enhancement Mode Field Effect TransistorVíctor MendozaNo ratings yet

- P1003EVG: P-Channel Enhancement Mode MOSFETDocument4 pagesP1003EVG: P-Channel Enhancement Mode MOSFETBig-man JuliannNo ratings yet

- Irf 7832Document10 pagesIrf 7832Nguyễn Minh TúNo ratings yet

- Irf7832Pbf: V R Max QGDocument10 pagesIrf7832Pbf: V R Max QGdreyes3773No ratings yet

- MMD70R600PDocument10 pagesMMD70R600PBoKi PoKiNo ratings yet

- UPA2790Document11 pagesUPA2790daniwesaNo ratings yet

- P45N03LTG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument3 pagesP45N03LTG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect Transistoraldo_suviNo ratings yet

- S1p2655a03-33 SamsungDocument10 pagesS1p2655a03-33 SamsungArturo NavaNo ratings yet

- 4800 AgmDocument5 pages4800 AgmaluiznetNo ratings yet

- P45N02LD Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument3 pagesP45N02LD Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorAnonymous qrSsYuxyoYNo ratings yet

- P2003EVG: P-Channel Enhancement Mode MOSFETDocument5 pagesP2003EVG: P-Channel Enhancement Mode MOSFETpepegotera454No ratings yet

- Sss7n60b (7n60b) MosfetDocument11 pagesSss7n60b (7n60b) MosfetCamilo AldanaNo ratings yet

- Pd1503yvs PDFDocument8 pagesPd1503yvs PDFAsep MuslihNo ratings yet

- Mosfet Irlb 8743Document9 pagesMosfet Irlb 8743Karan ArjunNo ratings yet

- Sipmos Power Transistor: Not For New DesignDocument9 pagesSipmos Power Transistor: Not For New Designstev_zoranNo ratings yet

- 12N50C3Document14 pages12N50C3AthinodorosNo ratings yet

- FQP6N60C/FQPF6N60C: 600V N-Channel MOSFETDocument10 pagesFQP6N60C/FQPF6N60C: 600V N-Channel MOSFETBiswajit SarkarNo ratings yet

- 2 N 7000Document6 pages2 N 7000zhlikhonNo ratings yet

- AO4413Document6 pagesAO4413Diana MedinaNo ratings yet

- IRFPS40N60K: Smps MosfetDocument9 pagesIRFPS40N60K: Smps MosfetRoozbeh BahmanyarNo ratings yet

- 2sj 598 Power Mos Dell 2407wfpbDocument8 pages2sj 598 Power Mos Dell 2407wfpbkarkeraNo ratings yet

- P0603BDGDocument5 pagesP0603BDGguvenelktNo ratings yet

- Lifetec LCD Monitor TransistorDocument9 pagesLifetec LCD Monitor TransistornegrusrlNo ratings yet

- 2SK3607-01MR: Super FAP-G SeriesDocument4 pages2SK3607-01MR: Super FAP-G SeriesPequeño IntelectoNo ratings yet

- 2SK2469-01MR: FAP-II SeriesDocument3 pages2SK2469-01MR: FAP-II SeriesHussain AzizNo ratings yet

- Mos Field Effect Transistor: Switching N-Channel Power Mos Fet Industrial UseDocument8 pagesMos Field Effect Transistor: Switching N-Channel Power Mos Fet Industrial UseroozbehxoxNo ratings yet

- Irfp 460 ADocument8 pagesIrfp 460 AKasun Darshana PeirisNo ratings yet

- FDS4435BZDocument6 pagesFDS4435BZCornel PislaruNo ratings yet

- SSF 7510Document5 pagesSSF 7510luis_h_t_79No ratings yet

- Apm 4546Document13 pagesApm 4546Walter FabianNo ratings yet

- K 3918Document8 pagesK 3918Anderson DuarteNo ratings yet

- Irfp 90 N 20 DDocument9 pagesIrfp 90 N 20 DAndré Frota PaivaNo ratings yet

- Mos Field Effect Transistor: Switching N-Channel Power Mos Fet Industrial UseDocument8 pagesMos Field Effect Transistor: Switching N-Channel Power Mos Fet Industrial Useaalex28No ratings yet

- FQPF5N60CDocument10 pagesFQPF5N60CguvenelktNo ratings yet

- 9915 H 04 DatasheetDocument6 pages9915 H 04 DatasheetBenny RoyNo ratings yet

- MTP52N06V Datasheet - 2 PDFDocument7 pagesMTP52N06V Datasheet - 2 PDFLeonel ValençaNo ratings yet

- MosfetDocument6 pagesMosfetfilibertooNo ratings yet

- MTP2955V Power MOSFET 12 Amps, 60 Volts: P-Channel TO-220Document8 pagesMTP2955V Power MOSFET 12 Amps, 60 Volts: P-Channel TO-220Rodrigo AlemánNo ratings yet

- Irfz46n PDFDocument9 pagesIrfz46n PDFYunier FernandezNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Hitachi NP6C Service ManualDocument20 pagesHitachi NP6C Service ManualMichael McDonaldNo ratings yet

- Error Code StandardizationDocument1 pageError Code StandardizationMichael McDonaldNo ratings yet

- Samsung Pn50c540g3fxza Troubleshooting Guide PDFDocument6 pagesSamsung Pn50c540g3fxza Troubleshooting Guide PDFMichael McDonaldNo ratings yet

- SoccersDocument1 pageSoccersMichael McDonaldNo ratings yet

- 17MB62Document9 pages17MB62Justin Williams100% (1)

- 17mb22 2 Circuit DiagramDocument8 pages17mb22 2 Circuit Diagramyomismooo32No ratings yet

- Vestel 17mb62-1 SCHDocument9 pagesVestel 17mb62-1 SCHb.nedelkov100% (2)

- 17PW22 4Document1 page17PW22 4rghathawayNo ratings yet

- 17pw26 2Document1 page17pw26 2marshall tmNo ratings yet

- The Basic Input-Output System SolutionsDocument2 pagesThe Basic Input-Output System SolutionsMichael McDonaldNo ratings yet

- LC-32SH130E LC-32SH130K LC-32SH340E: Service ManualDocument108 pagesLC-32SH130E LC-32SH130K LC-32SH340E: Service ManualMichael McDonaldNo ratings yet

- HP Compaq nx7010 COMPAL LA-1701R2.0Document49 pagesHP Compaq nx7010 COMPAL LA-1701R2.0Michael McDonaldNo ratings yet

- HP Compaq nx7010 COMPAL LA-1701R2.0Document49 pagesHP Compaq nx7010 COMPAL LA-1701R2.0Michael McDonaldNo ratings yet