Professional Documents

Culture Documents

p75n02ldg - PDF Mosfet

Uploaded by

indaviOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

p75n02ldg - PDF Mosfet

Uploaded by

indaviCopyright:

Available Formats

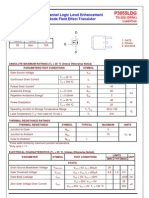

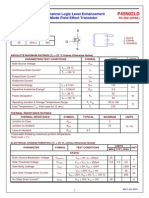

N-Channel Logic Level Enhancement

Mode Field Effect Transistor

NIKO-SEM

P75N02LDG

TO-252 (DPAK)

Lead-Free

D

PRODUCT SUMMARY

V(BR)DSS

RDS(ON)

ID

25

5m

75A

1. GATE

2. DRAIN

3. SOURCE

G

S

ABSOLUTE MAXIMUM RATINGS (TC = 25 C Unless Otherwise Noted)

PARAMETERS/TEST CONDITIONS

Gate-Source Voltage

TC = 25 C

Continuous Drain Current

1

Repetitive Avalanche Energy

VGS

20

75

50

170

IAR

60

L = 0.1mH

EAS

140

L = 0.05mH

EAR

5.6

TC = 25 C

Power Dissipation

UNITS

IDM

Avalanche Current

Avalanche Energy

LIMITS

ID

TC = 100 C

Pulsed Drain Current

SYMBOL

Operating Junction & Storage Temperature Range

1

Lead Temperature ( /16 from case for 10 sec.)

mJ

60

PD

TC = 100 C

32.75

Tj, Tstg

-55 to 150

TL

275

THERMAL RESISTANCE RATINGS

THERMAL RESISTANCE

SYMBOL

TYPICAL

MAXIMUM

Junction-to-Case

RJC

2.3

Junction-to-Ambient

RJA

62.5

Case-to-Heatsink

RCS

UNITS

C / W

0.6

Pulse width limited by maximum junction temperature.

Duty cycle 1

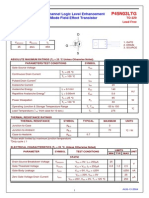

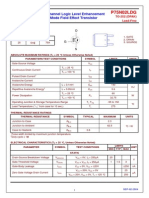

ELECTRICAL CHARACTERISTICS (TC = 25 C, Unless Otherwise Noted)

PARAMETER

SYMBOL

TEST CONDITIONS

LIMITS

UNIT

MIN TYP MAX

STATIC

V(BR)DSS

VGS = 0V, ID = 250A

25

VGS(th)

VDS = VGS, ID = 250A

Gate-Body Leakage

IGSS

VDS = 0V, VGS = 20V

250

Zero Gate Voltage Drain Current

IDSS

VDS = 20V, VGS = 0V

25

VDS = 20V, VGS = 0V, TJ = 125 C

250

Drain-Source Breakdown Voltage

Gate Threshold Voltage

V

1.5

3

nA

A

SEP-02-2004

N-Channel Logic Level Enhancement

Mode Field Effect Transistor

NIKO-SEM

1

On-State Drain Current

ID(ON)

Drain-Source On-State

1

Resistance

RDS(ON)

1

Forward Transconductance

VDS = 10V, VGS = 10V

gfs

P75N02LDG

TO-252 (DPAK)

Lead-Free

70

VGS = 10V, ID = 30A

VGS = 7V, ID = 24A

VDS = 15V, ID = 30A

16

m

S

DYNAMIC

Input Capacitance

Ciss

Output Capacitance

Coss

Reverse Transfer Capacitance

Crss

800

Qg

140

Total Gate Charge

2

2

Gate-Source Charge

2

Gate-Drain Charge

5000

VGS = 0V, VDS = 15V, f = 1MHz

Qgs

VDS = 0.5V(BR)DSS, VGS = 10V,

40

Qgd

ID = 35A

75

Turn-On Delay Time

td(on)

tr

VDS = 15V, RL = 1

td(off)

ID 30A, VGS = 10V, RGS = 2.5

24

Rise Time

Turn-Off Delay Time

2

Fall Time

pF

1800

nC

tf

nS

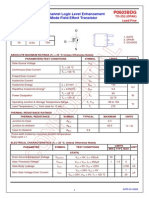

SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICS (TC = 25 C)

Continuous Current

Pulsed Current

3

1

Forward Voltage

Reverse Recovery Time

Peak Reverse Recovery Current

Reverse Recovery Charge

IS

75

ISM

170

VSD

IF = IS, VGS = 0V

1.3

trr

IRM(REC)

IF = IS, dlF/dt = 100A / S

Qrr

A

V

37

nS

200

0.043

Pulse test : Pulse Width 300 sec, Duty Cycle 2.

Independent of operating temperature.

3

Pulse width limited by maximum junction temperature.

1

2

REMARK: THE PRODUCT MARKED WITH P75N02LDG, DATE CODE or LOT #

Orders for parts with Lead-Free plating can be placed using the PXXXXXXXG parts name.

SEP-02-2004

N-Channel Logic Level Enhancement

Mode Field Effect Transistor

NIKO-SEM

P75N02LDG

TO-252 (DPAK)

Lead-Free

TO-252 (DPAK) MECHANICAL DATA

mm

mm

Dimension

Dimension

Min.

Typ.

Max.

Min.

Typ.

Max.

9.35

10.4

0.89

2.03

2.2

2.4

6.35

6.80

0.45

0.6

5.2

5.5

0.89

1.5

0.6

0.45

0.69

0.5

0.9

0.03

0.23

3.96

5.2

6.2

4.57

5.18

2

1

SEP-02-2004

You might also like

- p3055ldg - Source Drain Diode - HPDocument4 pagesp3055ldg - Source Drain Diode - HParthurcofnNo ratings yet

- Data Sheet - P3057LCG PDFDocument4 pagesData Sheet - P3057LCG PDFAdrian RouxNo ratings yet

- 3055 DatasheetDocument4 pages3055 DatasheetiuriepaliiNo ratings yet

- Niko - p07d03lvgDocument5 pagesNiko - p07d03lvgTininha MachadoNo ratings yet

- Data Sheet P Channel FETDocument5 pagesData Sheet P Channel FETMichael McDonaldNo ratings yet

- P2003BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument5 pagesP2003BDG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorMahmoued YasinNo ratings yet

- Nikos p2003bdgDocument5 pagesNikos p2003bdgjavierrincon800No ratings yet

- P45N03LTG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument3 pagesP45N03LTG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect Transistoraldo_suviNo ratings yet

- P0603BDGDocument5 pagesP0603BDGguvenelktNo ratings yet

- Data Sheet P2804BDGDocument5 pagesData Sheet P2804BDGsantiagobjNo ratings yet

- Advanced Power Electronics Corp.: AP4513GHDocument7 pagesAdvanced Power Electronics Corp.: AP4513GHqueequeg73No ratings yet

- N-Channel Enhancement Mode MOSFET: Product SummaryDocument5 pagesN-Channel Enhancement Mode MOSFET: Product SummaryTony RodriguesNo ratings yet

- S1p2655a03-33 SamsungDocument10 pagesS1p2655a03-33 SamsungArturo NavaNo ratings yet

- Niko-Sem: Dual N-Channel Enhancement Mode Field Effect TransistorDocument7 pagesNiko-Sem: Dual N-Channel Enhancement Mode Field Effect TransistorVíctor MendozaNo ratings yet

- Advanced Power Electronics Corp.: AP4525GEMDocument7 pagesAdvanced Power Electronics Corp.: AP4525GEMsontuyet82No ratings yet

- 9915 H 04 DatasheetDocument6 pages9915 H 04 DatasheetBenny RoyNo ratings yet

- P45N02LD Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument3 pagesP45N02LD Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorAnonymous qrSsYuxyoYNo ratings yet

- 2SK3607-01MR: Super FAP-G SeriesDocument4 pages2SK3607-01MR: Super FAP-G SeriesPequeño IntelectoNo ratings yet

- PD1503YVS: Dual N-Channel Enhancement Mode MOSFETDocument7 pagesPD1503YVS: Dual N-Channel Enhancement Mode MOSFETAldemir Fernando BattagliaNo ratings yet

- MosfetDocument6 pagesMosfetfilibertooNo ratings yet

- 60N03Document7 pages60N03BalbalaManiukNo ratings yet

- Fdb045An08A0: N-Channel Powertrench MosfetDocument12 pagesFdb045An08A0: N-Channel Powertrench MosfetRocio HernandezNo ratings yet

- D13a Motor de PartidaDocument8 pagesD13a Motor de Partidaalex lottiNo ratings yet

- FDP 8896Document11 pagesFDP 8896condejhonnyNo ratings yet

- 13N60 Series: N-Channel Power MOSFET 13A, 600volts DescriptionDocument8 pages13N60 Series: N-Channel Power MOSFET 13A, 600volts DescriptionAndres AlegriaNo ratings yet

- Tranzistor MOS FET Pentru Cif 250 Tip BSM 181Document7 pagesTranzistor MOS FET Pentru Cif 250 Tip BSM 181rataion241959No ratings yet

- Mosfet Irlb 8743Document9 pagesMosfet Irlb 8743Karan ArjunNo ratings yet

- P2103NV Niko-Sem: N-& P-Channel Enhancement Mode Field Effect TransistorDocument8 pagesP2103NV Niko-Sem: N-& P-Channel Enhancement Mode Field Effect TransistorMohamed SaiedNo ratings yet

- Power Transistor: SPP17N80C3 SPA17N80C3 Cool MOS™Document13 pagesPower Transistor: SPP17N80C3 SPA17N80C3 Cool MOS™cmlcaldeira10No ratings yet

- Power Mos Iv: APT6035BN 600V 19.0A 0.35Document4 pagesPower Mos Iv: APT6035BN 600V 19.0A 0.35Mario S Bar AguascalientesNo ratings yet

- 4800 AgmDocument5 pages4800 AgmaluiznetNo ratings yet

- Super FAP-G Series: Fuji Power MosfetDocument4 pagesSuper FAP-G Series: Fuji Power MosfetPedro Martinez GarayNo ratings yet

- Sipmos Power Transistor: Not For New DesignDocument9 pagesSipmos Power Transistor: Not For New Designstev_zoranNo ratings yet

- Lithium Ion Secondary Battery Applications Portable Equipment Applications Notebook PC ApplicationsDocument11 pagesLithium Ion Secondary Battery Applications Portable Equipment Applications Notebook PC Applicationstabassam7801No ratings yet

- Irfp 460 ADocument8 pagesIrfp 460 AKasun Darshana PeirisNo ratings yet

- 2 N 7000Document6 pages2 N 7000zhlikhonNo ratings yet

- Irfp 90 N 20 DDocument9 pagesIrfp 90 N 20 DAndré Frota PaivaNo ratings yet

- FAP-IIS Series: Features Outline DrawingDocument2 pagesFAP-IIS Series: Features Outline DrawingJulio Chuquilin BecerraNo ratings yet

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Document11 pagesN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateNo ratings yet

- Irf7832Pbf: V R Max QGDocument10 pagesIrf7832Pbf: V R Max QGdreyes3773No ratings yet

- P11N60Document14 pagesP11N60AndrewerNo ratings yet

- IRF540NDocument7 pagesIRF540Nmichaelliu123456No ratings yet

- NTD78N03 Power MOSFET: 25 V, 78 A, Single N Channel, DPAKDocument7 pagesNTD78N03 Power MOSFET: 25 V, 78 A, Single N Channel, DPAKfercikeNo ratings yet

- 2sk3673 MosfetDocument4 pages2sk3673 Mosfetagus2kNo ratings yet

- Irfb4020Pbf: Digital Audio MosfetDocument8 pagesIrfb4020Pbf: Digital Audio Mosfetto_netiksNo ratings yet

- 5M0380RDocument20 pages5M0380RGenaro Santiago MartinezNo ratings yet

- 2SK2469-01MR: FAP-II SeriesDocument3 pages2SK2469-01MR: FAP-II SeriesHussain AzizNo ratings yet

- Coolmos Power Transistor: Features Product SummaryDocument12 pagesCoolmos Power Transistor: Features Product SummarychiknaNo ratings yet

- 15NO3GHDocument19 pages15NO3GHSantiago BecharaNo ratings yet

- Pd1503yvs PDFDocument8 pagesPd1503yvs PDFAsep MuslihNo ratings yet

- Irf 7832Document10 pagesIrf 7832Nguyễn Minh TúNo ratings yet

- N-Channel Junction FET: Guangdong Yuejing High Technology CO.,LTDDocument1 pageN-Channel Junction FET: Guangdong Yuejing High Technology CO.,LTDLaura ZambranoNo ratings yet

- IRF8788Document9 pagesIRF8788Robert KovacsNo ratings yet

- P75N02LDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP75N02LDG: N-Channel Enhancement Mode MOSFETNoheli Moyano SuarezNo ratings yet

- F-III Series: Features Outline DrawingDocument2 pagesF-III Series: Features Outline DrawingdevelopmentworldNo ratings yet

- UPA2790Document11 pagesUPA2790daniwesaNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Ampli 90wDocument3 pagesAmpli 90windaviNo ratings yet

- Ampli 90wDocument3 pagesAmpli 90windaviNo ratings yet

- Phone MM 3111 eDocument3 pagesPhone MM 3111 eindaviNo ratings yet

- Ampli 90wDocument3 pagesAmpli 90windaviNo ratings yet

- QoS+ PCQDocument36 pagesQoS+ PCQAlexander Martinez0% (1)

- p75n02ldg - PDF MosfetDocument3 pagesp75n02ldg - PDF Mosfetindavi100% (1)

- Mangle IpDocument1 pageMangle IpindaviNo ratings yet

- Circulo para Saber Cores de ResistenciasDocument1 pageCirculo para Saber Cores de ResistenciasNelson SeixasNo ratings yet

- Samsung CL21K3W PDFDocument4 pagesSamsung CL21K3W PDFNelson Muñoz BautistaNo ratings yet

- RZ 15la66Document33 pagesRZ 15la66indaviNo ratings yet

- Panasonic DVD Dmr-Es15Document70 pagesPanasonic DVD Dmr-Es15cristian ianosNo ratings yet

- Smart Home Security and Intrusion Detection SystemDocument7 pagesSmart Home Security and Intrusion Detection SystemEditor IJTSRDNo ratings yet

- Specification ChillerDocument28 pagesSpecification Chillermishtinil100% (1)

- 12 Volt Gel Cell Charger by N1Hfx: Parts ListDocument3 pages12 Volt Gel Cell Charger by N1Hfx: Parts Listsa920189No ratings yet

- Mee 22625Document31 pagesMee 22625kunalpatil7367No ratings yet

- Exercises With Finite State Machines: CS 64: Computer Organization and Design Logic Lecture #17 Winter 2019Document17 pagesExercises With Finite State Machines: CS 64: Computer Organization and Design Logic Lecture #17 Winter 2019Gabriel CañadasNo ratings yet

- Sistema Electronico Del Motor A Gas HyundaiDocument18 pagesSistema Electronico Del Motor A Gas HyundaiJusto PaniaguaNo ratings yet

- TDA7449Document21 pagesTDA7449Sambhu Dharmadevan VU3KQFNo ratings yet

- Matrices - JEE Main 2022 Chapter Wise Questions by MathonGoDocument17 pagesMatrices - JEE Main 2022 Chapter Wise Questions by MathonGoPraiyansh GautamNo ratings yet

- QUBE Catalogue 2013Document30 pagesQUBE Catalogue 2013FBTelettronica100% (3)

- LG M197wae LW91BDocument37 pagesLG M197wae LW91B- M I L T O N - - G. -ANo ratings yet

- G - Analytical Forced Convection Modeling of Plate Fin Heat SinksDocument8 pagesG - Analytical Forced Convection Modeling of Plate Fin Heat SinksDhrubajyoti DasNo ratings yet

- Lab Assignment No.03Document8 pagesLab Assignment No.03uns chNo ratings yet

- SME102 - 1. IntroductionDocument48 pagesSME102 - 1. Introductionabdinigussie021No ratings yet

- Irs2092 Product InfoDocument17 pagesIrs2092 Product InfoAnderson LuizNo ratings yet

- (Chapter 2-5) Signal Analysis and Mixing (19-40)Document19 pages(Chapter 2-5) Signal Analysis and Mixing (19-40)Archangel GabNo ratings yet

- Robots, Androids, Al: Which TransmitDocument7 pagesRobots, Androids, Al: Which Transmitسعيد تامرNo ratings yet

- شيتات محطات كهربية PDFDocument8 pagesشيتات محطات كهربية PDFhazem saeidNo ratings yet

- Katalog ENDocument24 pagesKatalog ENtest asdNo ratings yet

- Amphenol A SeriesDocument36 pagesAmphenol A SeriesAMNo ratings yet

- IEEE - C136.27 - 1996 Roadway and Tunnel Lighting EquipmentDocument10 pagesIEEE - C136.27 - 1996 Roadway and Tunnel Lighting EquipmentSamir MukhtarNo ratings yet

- Achieving High Performance With Heft Analytics - AccentureDocument20 pagesAchieving High Performance With Heft Analytics - AccentureSweta DeyNo ratings yet

- Manual: Powder CoatingDocument3 pagesManual: Powder CoatingHans LimNo ratings yet

- SURAPID Door Operator Manual XT0223S16023Document34 pagesSURAPID Door Operator Manual XT0223S16023victor zapataNo ratings yet

- Electrical Works SpecificationsDocument131 pagesElectrical Works SpecificationsGnabBang100% (2)

- MINIMUM STOCK FLEET SUPPORT - Rev3Document3 pagesMINIMUM STOCK FLEET SUPPORT - Rev3Franco Flex Air Flex AirNo ratings yet

- CFS 02 MDB 06Document2 pagesCFS 02 MDB 06fahamida joyaNo ratings yet

- High Capacity 298Wh Rechargeable Li-Ion Battery With SmbusDocument1 pageHigh Capacity 298Wh Rechargeable Li-Ion Battery With SmbusMostafa MoghariNo ratings yet

- BN208-Networked Applications - T1 2020 - Assessment PaperDocument9 pagesBN208-Networked Applications - T1 2020 - Assessment PaperMuhammad YousafNo ratings yet

- Chapter 1 C.T.Document33 pagesChapter 1 C.T.Tana Azeez100% (1)