Professional Documents

Culture Documents

Realizacija Logickih Sklopova

Uploaded by

Richard LekajCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Realizacija Logickih Sklopova

Uploaded by

Richard LekajCopyright:

Available Formats

II.

Elektroniki sklopovi 1

DIGITALNA

ELEKTRONIKA

II. Elektroniki sklopovi 2

Tehnike realizacije logikih sklopova

Razliitosti tehnika s obzirom na:

Brzinu rada

Utroak snage

Otpornost na um

Jednostavnost izrade (cijena)

...

II. Elektroniki sklopovi 3

Tehnike realizacije logikih sklopova

Logike familije integriranih sklopova mogu se podijeliti u dvije osnovne

grupe:

Sklopove koji se temelje na radu bipolarnih tranzistora

Sklopove koji koriste MOSFET tranzistore

II. Elektroniki sklopovi 4

Tehnike realizacije logikih sklopova

Neke tehnike:

otpornik-tranzistor logika (RTL)

diodna logika (DL)

diodno-tranzistorska logika (DTL)

tranzistor-tranzistor logika (TTL)

logika zajednikog emitera (ECL)

MOSFET (MOS)

komplementarni MOSFET (CMOS)

II. Elektroniki sklopovi 5

Tehnike realizacije logikih sklopova

S razvojem tehnologije, neke tehnike su se pokazale male uspjenim od

drugih, npr:

otpornik-tranzistor logika (RTL) (nije vie u upotrebi)

diodna logika (DL) (nije u upotrebi u int.sklopovima)

diodno-tranzistorska logika (DTL) (nije vie u upotrebi)

tranzistor-tranzistor logika (TTL)

logika zajednikog emitera (ECL)

MOSFET (MOS)

komplementarni MOSFET (CMOS) danas najee

II. Elektroniki sklopovi 6

Tehnike realizacije logikih sklopova

Logiki sklopovi mogu biti realizirani u pozitivnoj i negativnoj logici.

Pozitivna logika je ona kod koje je napon nivoa '1' pozitivniji od nivoa '0' tj.

U(1) > U(0), a negativna logika je ona kod koje je napon nivoa '1' negativniji

od nivoa '0' tj. U(1) < U(0).

Drugim rijeima, negativna logika predstavlja inverziju pozitivne logike

II. Elektroniki sklopovi 7

Tehnike realizacije logikih sklopova

Svako realno linearno pojaalo ima ogranieni opseg izlaznih napona koji je

odreen naponom napajanja.

Prijenosna karakteristika tipinog invertirajueg linearnog pojaala prikazana

je na slici

II. Elektroniki sklopovi 8

Tehnike realizacije logikih sklopova

Ako takav sklop elimo koristiti kao linearno pojaalo, moramo osigurati da

ulazni napon bude unutar linearnog podruja rada sklopa.

No, moemo ga koristiti i kao logiki sklop: ako je ulazni signal uvijek izvan

linearnog podruja rada pojaala, dva preostala ulazna podruja napona

moemo predstaviti sa '0' (podruje niih ulaznih napona) i '1' (podruje viih

ulaznih napona)

II. Elektroniki sklopovi 9

Tehnike realizacije logikih sklopova

Izlazni napon onda moe imati samo dvije mogue vrijednosti maksimalna

izlazna vrijednost ('1') i minimalna izlazna vrijednost napona ('0').

ne koristi se!

Npr. ako ulazni napon ima bilo

koju od ovih vrijednosti, logiki

sklop e ga tretirati kao logiku 0

Ako izl. napon ima bilo koju

vrijednost iz ovog raspona, tretira

se kao logiko 1.

OTPORNOST

NA

UM / SMETNJU!

II. Elektroniki sklopovi 10

Tehnike realizacije logikih sklopova

Sa slike vidimo da za vrijednost na

ulazu '0', na izlazu imamo '1', i

obratno ovo je najjednostavniji

logiki sklop: logiki inverter ili NE

sklop.

Izlaz (naponska razina) iz ovakvog

sklopa moe se dovesti na ulaz

nekog drugog logikog sklopa.

Potrebno je napomenuti da se pri izradi logikih invertora nastoji linearno

podruje tj. podruje prijelaza iz jednog stanja u drugo to vie smanjiti

odnosno postii to bri prijelaz iz jednog stanja u drugo (obrnuto od

pojaala, gdje elimo to due (idealno, uvijek) ostati u linearnom

podruju).

II. Elektroniki sklopovi 11

Tehnike realizacije logikih sklopova

Bipolarni tranzistor kao logika sklopka (tranzistorska sklopka)

Kad je ulazni napon U

ul

blizu nule, BJT je iskljuen (ne vodi tj. radi u

zapiranju) i kroz kolektor protie zanemariva struja U

R

0. Izlazni napon U

iz

je zbog toga po iznosu gotovo jednak naponu napajanja U

CC

U

R

=R

C

I

C

2. Kirch.zakon:

U

iz

=U

CC

-U

R

II. Elektroniki sklopovi 12

Tehnike realizacije logikih sklopova

Bipolarni tranzistor kao logika sklopka

Kad je ulazni napon visok, BJT je ukljuen (vodi, tj. radi u zasienju),

U

R

U

CC

izlazni napon je jednak naponu U

CE

zasienja tranzistora, koji

openito iznosi oko 0.2 V.

Na slici su prikazani odnosi izmeu ulaznog

signala invertora i odgovarajue struje kolektora i

izlaznog napona.

Kada bi se tranzistor ponaao kao idealna

sklopka, za niski ulazni napon (0 na ulazu) izlazni

napon bi bio tono U

CC

, a za visoki ulazni napon

(1 na ulazu) tono 0V tranzistorska sklopka je

aproksimacija idealne sklopke

II. Elektroniki sklopovi 13

Tehnike realizacije logikih sklopova

Bipolarni tranzistor kao logika sklopka

Postoji kanjenje izmeu promjene ulaznog

napona i odziva na izlazu tranzistora.

Vrijeme iskljuenja je znaajno dulje od

vremena ukljuenja. Osnovni razlog je u

duljem vremenu potrebnom minoritetnim

nositeljima da napuste bazu prilikom

iskljuenja.

Ova vremena su vrlo kratka (tipino red

veliine ns do s)

ZAKLJUAK: Bipolarni tranzistor se moe

iskoristiti kao vrlo brza elektronika sklopka,

ije je stanje (ukljueno/iskljueno) odreeno

iznosom ulaznog napona

II. Elektroniki sklopovi 14

Tehnike realizacije logikih sklopova

MOSFET tranzistor kao logika sklopka

MOSFET je dominantan oblik koritenja FET-ova za primjenu u digitalnoj

tehnici.

Za analogne primjene naziv FET-ovi, u digitalnim sustavima - MOS

sklopovi (opisuje nain izrade tranzistora umjesto naina rada).

Glavne prednosti MOS tranzistora u odnosu na bipolarne tranzistore:

jednostavnost i jeftinija izrada.

Dodatne prednosti MOS logikih sklopova (sklopova temeljenih na MOS

tranzistorima): zauzimaju manju povrinu na siliciju (vei broj elemenata

na ipu); manja i potronja snage (manje zagrijavanje).

Nedostatak MOS tranzistora: (openito) sporiji rad

Osnovna shema i princip koritenja MOS-sklopke je vrlo slina BJT-

sklopki

II. Elektroniki sklopovi 15

Tehnike realizacije logikih sklopova

MOSFET tranzistor kao logika sklopka (NE sklop)

Kad je ulazni napon U

ul

(U

GS

) nizak (blizu 0 V), N-kanalni MOSFET obogaenog

tipa je iskljuen (ponaa se kao otvorena sklopka) jer je tranzistoru potreban

pozitivan napon na upravljakoj elektrodi za formiranje kanala izmeu S i D.

Struja izvoda I

D

je stoga zanemariva - na otporniku R gotovo nikakav pad napona.

Izlazni napon je stoga (2. K.Z., ista logika kao kod BJT-a)

blizu napona napajanja U

iz

U

DD

(logika '1').

Kad je ulazni napon na visokom potencijalu (blizu napona

napajanja), velik ulazni napon formira kanal vrlo malog

otpora. MOSFET je ukljuen (ponaa se kao zatvorena

sklopka) i struja tee kroz otpornik R i kanal. Kako je

otpor kanala znatno manji od R, pad napona na kanalu

(U

iz

) je znatno manji od pada napona na R (sjetimo se

naponskog djelila), tj. izlazni napon je blizu 0 V (logika

'0').

II. Elektroniki sklopovi 16

Tehnike realizacije logikih sklopova

MOSFET (MOS)

Koritenje otpornika u integriranim sklopovima nije ekonomino pa se kao

aktivna optereenja koriste MOSFET tranzistori osiromaenog tipa kojima

je U

GS

=0, pa je kanal uvijek isti (kanal glumi otpornik)

Koritenje N-kanalnih MOSFET tranzistora: NMOS logika

Koritenje P-kanalnih tranzistora: PMOS logika

Velika prednost MOS tehnologije: jednostavnost izrade u integriranoj

tehnici (cijena).

II. Elektroniki sklopovi 17

Tehnike realizacije logikih sklopova

MOSFET (MOS)

NE sklop NI sklop

ponaa se

kao otpornik

Samo ako su oba ulaza na

log.1, oba MOSFETa e biti

ukljuena (obje sklopke

zatvorene), pa potencijal

toke Z (izlazni napon) pada

na 0. Ako je i jedan od

MOSFETa iskljuen (na ulazu

ima nizak napon, tj. log. 0),

(gotovo) nema I

D

(gotovo)

nema pada napona na R

potencijal Z U

DD

II. Elektroniki sklopovi 18

Tehnike realizacije logikih sklopova

Komplementarni MOSFET (CMOS)

velika brzina rada

vrlo mala potronja (izl. struja praktino nikad ne tee)

Ovi sklopovi koriste istovremeno i N-kanalne i P-kanalne MOSFETe -

odatle i naziv: komplementarni MOSFET.

Kao i kod NMOS sklopova, napon U

DD

predstavlja logiku '1', a 0 V

predstavlja logiku '0'. Kako su razliito polarizirani, tranzistori se razliito

ponaaju s obzirom na napon na upravljakoj elektrodi.

Osnovni princip:

Dok visoki napon (npr. oko U

DD

) na upravljakoj elektrodi ukljuuje N-kanalni

tranzistor, istovremeno iskljuuje P-kanalni. Obratno vrijedi za niski (npr. oko

0V) napon na upravljakoj elektrodi.

II. Elektroniki sklopovi 19

Tehnike realizacije logikih sklopova

Komplementarni MOSFET (CMOS)

CMOS:

a) NE sklop

b) NI sklop

II. Elektroniki sklopovi 20

D

S

G

D

S

G

+5V

0V

+5V (logika 1)

T1

T2

0V (logika 0)

UGS1 = 0V

UGS2 = 5V

A Z

Tehnike realizacije logikih sklopova

Ako se komplementarni MOSFETi promatraju kao idealne sklopke upravljane naponom (ovo je

aproksimacija u svrhu lakeg promatranja osnovnog pricipa rada), N-kanalni se ponaa kao

zatvorena sklopka (formiran jak kanal) ako je potencijal G dovoljno vei od potencijala S (tj. U

GS

dovoljno pozitivan). Meutim, P-kanalni se ponaa kao zatvorena sklopka ako je potencijal G

dovoljno manji od S (da bi se kanal formirao, G treba privlaiti upljine), tj. U

GS

mora biti negativno

(ovaj sluaj je za sliku desno, kada je na ulazu logika 0: U

GS

= -5V).

Princip rada CMOS

NE sklopa (MOSFETi

se promatraju kao

idealne sklopke).

D

S

G

D

S

G

+5V

0V

0V (logika 0)

T1

T2

5V (logika 1)

UGS1 = -5V

UGS2 = 0V

A Z

II. Elektroniki sklopovi 21

Tehnike realizacije logikih sklopova

Princip rada CMOS NI sklopa za A=0,B=1 i A=1,B=0

D

S

G

D

S

G

D

S

G

D

S

G

T1 T2

T3

T4

+5V

A

B

0V (logika 0)

5V (logika 1)

Z

D

S

G

T1 T2

T3

T4

+5V

A

B

0V (logika 0)

Z

D

S

G

5V (logika 1)

5V (logika 1)

D

S

G

5V (logika 1)

D

S

G

II. Elektroniki sklopovi 22

D

S

G

D

S

G

T1 T2

T3

T4

+5V

A

B

0V (logika 0)

Z

0V (logika 0)

D

S

G

D

S

G

5V (logika 1)

Tehnike realizacije logikih sklopova

Princip rada CMOS NI sklopa za A=0,B=0 i A=1,B=1

D

S

G

T1 T2

T3

T4

+5V

A

B

5V (logika 1)

Z

0V (logika 0)

5V (logika 1)

D

S

G

D

S

G

D

S

G

II. Elektroniki sklopovi 23

Tehnike realizacije logikih sklopova

Komplementarni MOSFET (CMOS)

NAPOMENA:

Da bi se NMOS ponaao kao zatvorena sklopka, nije nuno da bude U

GS

=5V (kao u prethodnim

ilustrativnim primjerima), ve je dovoljno da G bude dovoljno pozitivniji od S (tipino po iznosu iznad

cca. 50% napona dodira promatranog NMOS-a, U

P

). Npr. ako je U

P

=2V za oba NMOS-a iz prethodnog

primjera, dovoljno je (tipino) da U

GS

>3V da bi se NMOS mogao smatrati zatvorenom sklopkom, no

to pozitivniji G u odnosu na S, kanal je deblji i NMOS predstavlja bolju aproksimaciju sklopke. Isto

tako, da bi se NMOS ponaao kao otvorena sklopka nije nuno da U

GS

=0V (kao u primjerima) -

dovoljno je samo da U

GS

<U

P

(jer tada nema kanala i otpor izmeu D i S je praktino beskonaan).

Potpuno isto vrijedi i za PMOS-e, samo su obrnuti predznaci. Npr. pretpostavimo da je napon dodira

oba PMOS-a iz prethodnog primjera U

P

= -2V. Ako je U

GS

<-3V, moemo uzeti da je formiran dovoljno

jak P-kanal da se PMOS moe smatrati zatvorenom sklopkom. Naravno, to je potencijal G nii u

odnosu na S, to je aproksimacija sklopke bolja npr. U

GS

=-5V (potencijal toke A je 0V) je bolje od

U

GS

=-4V (potencijal toke A je 1V). Isto tako, ako je U

GS

>-2V

, onda kanal ne postoji, te PMOS

predstavlja otvorenu sklopku (dakle, svejedno je dali je U

GS

= -1.5V, -1V ili 0V kanala nema!).

UKRATKO: Na ulaze A i B se nije moralo dovoditi 5V kao logika 1 i 0V kao logika 0, da bi sklop

korektno radio. Podjednako bi dobro radio i da smo dovodili npr. 4.8V kao logiku 1 i/ili npr. 0.4V kao

logiku 0.

II. Elektroniki sklopovi 24

Tehnike realizacije logikih sklopova

Komplementarni MOSFET (CMOS)

Iako je CMOS sklopove tee proizvesti nego NMOS ili PMOS sklopove jer je

potrebno izraivati istovremeno i N i P kanalne MOSFETe, velika brzina, mala

potronja i velika otpornost na um imaju za posljedicu da je ova tehnologija

najrairenija tehnologija koja se koristi pri izradi integriranih krugova (IC-

ova) danas.

You might also like

- Elektronski InstrumentiDocument58 pagesElektronski InstrumentialjosabaNo ratings yet

- Vaja Ie BoostDocument5 pagesVaja Ie BoostMaja SajamNo ratings yet

- PitanjaDocument4 pagesPitanjapredrag152No ratings yet

- V.katic - Ee2 - 2. Invertori - DC-ACDocument26 pagesV.katic - Ee2 - 2. Invertori - DC-ACAleksandar Kerekesh100% (2)

- Analogne Modulacije Kratki Rad I ObjasnjenjeDocument46 pagesAnalogne Modulacije Kratki Rad I ObjasnjenjeBoris VujasinovićNo ratings yet

- DSP 2Document6 pagesDSP 2matijapoNo ratings yet

- DSP 5Document19 pagesDSP 5matijapoNo ratings yet

- PkseDocument32 pagesPkseapi-3763057100% (2)

- Tranzistorske Priručne TabeleDocument450 pagesTranzistorske Priručne Tabeleemir.muderizovicNo ratings yet

- EME Predavanja 2 DelDocument23 pagesEME Predavanja 2 DelJaka ŠkuljNo ratings yet

- VAJE 1-8 2022-23 2.skupinaDocument32 pagesVAJE 1-8 2022-23 2.skupinajakamerelaNo ratings yet

- Mini Recnik Iz ElektronikeDocument8 pagesMini Recnik Iz ElektronikeBojan NeškovićNo ratings yet

- Unipolarni Tranzistorji: Princip Delovanja MosfetaDocument6 pagesUnipolarni Tranzistorji: Princip Delovanja MosfetaSebastjan ŽeleznikNo ratings yet

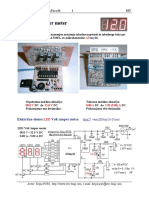

- Svet Elektronike Esr C Meter-2Document4 pagesSvet Elektronike Esr C Meter-2aves1100% (1)

- Elektro - Vprašanja Z Odgovori - Matura ZagovorDocument10 pagesElektro - Vprašanja Z Odgovori - Matura ZagovorSlobodan GerićNo ratings yet

- Hasan Halilčević - Osnove Elektrotehnike Modul 6Document36 pagesHasan Halilčević - Osnove Elektrotehnike Modul 6Ahmed SagdatiNo ratings yet

- Elektricne Instalacije in RazsvetljavaDocument17 pagesElektricne Instalacije in Razsvetljavajure100% (1)

- Projektni Zadatak Za STSDocument3 pagesProjektni Zadatak Za STSSlaven PavlovicNo ratings yet

- Elektronika I ElektrotehnikaDocument148 pagesElektronika I ElektrotehnikaDomagojLevatić100% (2)

- Drugi DanDocument7 pagesDrugi DanDragana VuckovicNo ratings yet

- Impulsni I Digitalni SklopoviDocument189 pagesImpulsni I Digitalni Sklopoviandrej.majtanNo ratings yet

- EFI PrirocnikDocument20 pagesEFI PrirocnikGorazd ŠNo ratings yet

- Imortant TTL Kolo ObjasnjenjeDocument42 pagesImortant TTL Kolo ObjasnjenjeŠuša StefanNo ratings yet

- 19 Merilni TransformatorjiDocument3 pages19 Merilni TransformatorjiknarimNo ratings yet

- Elektronske Komponente - Laboratorijske Vezbe PDFDocument15 pagesElektronske Komponente - Laboratorijske Vezbe PDFOlena DjenicNo ratings yet

- Elektronska Merenja (Uputstvo Za Laboratorijske Vežbe)Document14 pagesElektronska Merenja (Uputstvo Za Laboratorijske Vežbe)eratilNo ratings yet

- Ek17 3705 EmkDocument4 pagesEk17 3705 EmkarozmanNo ratings yet

- Ra 1Document32 pagesRa 1shaq32No ratings yet

- Punjac Akumulatora 0,1-3ADocument4 pagesPunjac Akumulatora 0,1-3Akurajber11No ratings yet

- Analize Kratkih SpojevaDocument125 pagesAnalize Kratkih SpojevaPadalović ArnelNo ratings yet

- Elektronika Za 3 Razred TŠDocument6 pagesElektronika Za 3 Razred TŠIt's LuciferNo ratings yet

- VAmeter LEDDocument6 pagesVAmeter LEDGOST TECH GOST-технологияNo ratings yet

- TSiTR Predloge VajeDocument14 pagesTSiTR Predloge VajetablicafiskalNo ratings yet

- Rif Ref A D Konvertorji 01Document6 pagesRif Ref A D Konvertorji 01MatjazNo ratings yet

- Zbirka Rešenih Zadataka Iz Proizvodnje, Prenosa I Upotrebe Električne Energije - J ŠtarkljDocument40 pagesZbirka Rešenih Zadataka Iz Proizvodnje, Prenosa I Upotrebe Električne Energije - J ŠtarkljVerica RanđelovićNo ratings yet

- Prezentacija Optolaserska TehnikaDocument20 pagesPrezentacija Optolaserska Tehnikas26marNo ratings yet

- 3 Simboli Elektronskih KomponentDocument14 pages3 Simboli Elektronskih Komponentneuro4761No ratings yet

- Enosmerna VezjaDocument8 pagesEnosmerna Vezjamarkoskace02No ratings yet

- Modeliranje Električnih Strojev Zbirka NalogDocument65 pagesModeliranje Električnih Strojev Zbirka NalogRobert MlakerNo ratings yet

- Zbirka Zadataka Iz ElektronikeDocument104 pagesZbirka Zadataka Iz ElektronikeNecokvNo ratings yet

- Vaja 01Document7 pagesVaja 01Matjaž AdlerNo ratings yet

- VAJA03 NapetostInLastnostiBaterijDocument8 pagesVAJA03 NapetostInLastnostiBaterijLovro VeberNo ratings yet

- Amperov - ZakonDocument8 pagesAmperov - Zakonn2o2oNo ratings yet

- Ele Vsa VprasanjaDocument58 pagesEle Vsa Vprasanjalubej.mitjaNo ratings yet

- Navodila 2F v3Document8 pagesNavodila 2F v3Bogdan ZepanNo ratings yet

- SeminarskaDocument5 pagesSeminarskaminecraft davidNo ratings yet

- Električne MašineDocument16 pagesElektrične MašineMiro Žarić0% (1)

- Skripta Iz MikroelektronikeDocument65 pagesSkripta Iz MikroelektronikeHologramNo ratings yet

- Industrijska ElektronikaDocument20 pagesIndustrijska ElektronikaDomagojLevatićNo ratings yet

- TeorijaDocument65 pagesTeorijadane discordNo ratings yet

- BrojilaDocument2 pagesBrojilaJosip MešinNo ratings yet

- Elektronske KomponenteDocument407 pagesElektronske Komponentemarfi1994No ratings yet

- Resene Vaje-Izracun Kratkih StikovDocument39 pagesResene Vaje-Izracun Kratkih StikovJurij BlaslovNo ratings yet

- ReferatDocument16 pagesReferatblaagicaNo ratings yet

- 1.kontrolna Naloga EEL3, E3B Na DaljavoDocument1 page1.kontrolna Naloga EEL3, E3B Na DaljavoLukaNo ratings yet