Professional Documents

Culture Documents

BJT Bias 1

BJT Bias 1

Uploaded by

Steph VillaruzOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BJT Bias 1

BJT Bias 1

Uploaded by

Steph VillaruzCopyright:

Available Formats

ENGI 242/ELEC 222

January 2004

BJT Fixed Bias

ENGI 242

ELEC 222

BJT Biasing 1

For Fixed Bias Configuration:

Draw Equivalent Input circuit

Draw Equivalent Output circuit

Write necessary KVL and KCL Equations

Determine the Quiescent Operating Point

Graphical Solution using Loadlines

Computational Analysis

Design and test design using a computer simulation

January 2004

Fixed Bias

ENGI 242/ELEC 222

ENGI 242/ELEC 222

January 2004

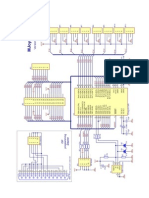

Complete CE Amplifier with Fixed Bias

January 2004

ENGI 242/ELEC 222

Fixed Bias and Equivalent DC Circuit

January 2004

Fixed Bias

ENGI 242/ELEC 222

ENGI 242/ELEC 222

January 2004

Fixed-Bias Circuit

January 2004

ENGI 242/ELEC 222

DC Equivalent Circuit

January 2004

Fixed Bias

ENGI 242/ELEC 222

ENGI 242/ELEC 222

January 2004

Base-Emitter (Input) Loop

Using Kirchoffs voltage law: VCC + IBRB + VBE = 0

Solving for IB: I B =

January 2004

V C C - V BE

RB

ENGI 242/ELEC 222

Collector-Emitter (Output) Loop

Since:

IC = IB

Using Kirchoffs voltage law: VCC + IC RC + VCE = 0

Because:

VCE = VC VE

Since VE = 0V, then:

VC = VCE

And

VCE = VCC - IC RC

Also:

VBE = VB - VE

with VE = 0V, then:

VB = VBE

January 2004

Fixed Bias

ENGI 242/ELEC 222

ENGI 242/ELEC 222

January 2004

BJT Saturation Regions

When the transistor is operating in the

Saturation Region, the transistor is

conducting at maximum collector

current (based on the resistances in

the output circuit, not the spec sheet

value) such that:

VCC - VCE

RC

where VCE = 0.2 V

ICsat =

January 2004

ENGI 242/ELEC 222

Determining Icsat

January 2004

Fixed Bias

ENGI 242/ELEC 222

10

ENGI 242/ELEC 222

January 2004

Determining ICSAT for the fixed-bias configuration

January 2004

ENGI 242/ELEC 222

11

Load Line Analysis

January 2004

Fixed Bias

ENGI 242/ELEC 222

12

ENGI 242/ELEC 222

January 2004

Load Line Analysis

The end points of the line are : ICsat and VCEcutoff

For load line analysis, use VCE = 0 for ICSAT, and IC = 0 for VCEcutoff

ICsat:

VCEcutoff:

VCC

|VCE = 0V

RC

VCE = VCC |IC = 0mA

ICsat =

Where IB intersects with the load line we have the Q point

Q-point is the particular operating point:

Value of RB

Sets the value of IB

Where IB and Load Line intersect

Sets the values of VCE and IC.

January 2004

ENGI 242/ELEC 222

13

Circuit values effect Q-point

January 2004

Fixed Bias

ENGI 242/ELEC 222

14

ENGI 242/ELEC 222

January 2004

Circuit values effect Q-point (continued)

January 2004

ENGI 242/ELEC 222

15

Circuit values effect Q-point (continued)

January 2004

Fixed Bias

ENGI 242/ELEC 222

16

ENGI 242/ELEC 222

January 2004

Load-line analysis

January 2004

ENGI 242/ELEC 222

17

DC Fixed Bias Circuit Example

January 2004

Fixed Bias

ENGI 242/ELEC 222

18

ENGI 242/ELEC 222

January 2004

Loadline Example Family of Curves

January 2004

ENGI 242/ELEC 222

19

Emitter Stabilized Bias

ENGI 242

ELEC 222

Fixed Bias

10

ENGI 242/ELEC 222

January 2004

BJT Emitter Bias

For the Emitter Stabilized Bias Configuration:

Draw Equivalent Input circuit

Draw Equivalent Output circuit

Write necessary KVL and KCL Equations

Determine the Quiescent Operating Point

Graphical Solution using Loadlines

Computational Analysis

Design and test design using a computer simulation

January 2004

ENGI 242/ELEC 222

21

Improved Bias Stability

The addition of RE to the Emitter circuit improves the stability of a transistor

output

Stability refers to a bias circuit in which the currents and voltages will

remain fairly constant over a wide range of temperatures and transistor

forward current gain ()

The temperature (TA or ambient temperature) surrounding the transistor

circuit is not always constant

Therefore, the transistor is not a constant value

January 2004

Fixed Bias

ENGI 242/ELEC 222

22

11

ENGI 242/ELEC 222

January 2004

Emitter-Stabilized Bias Circuit

Adding an emitter resistor to the circuit between the emitter lead and ground stabilizes

the bias circuit over Fixed Bias

January 2004

ENGI 242/ELEC 222

23

Base-Emitter Loop

January 2004

Fixed Bias

ENGI 242/ELEC 222

24

12

ENGI 242/ELEC 222

January 2004

Equivalent Network

January 2004

ENGI 242/ELEC 222

25

Reflected Input impedance of RE

January 2004

Fixed Bias

ENGI 242/ELEC 222

26

13

ENGI 242/ELEC 222

January 2004

Base-Emitter Loop

Applying Kirchoffs voltage law:

Since:

- VCC + IB RB + VBE +IE RE = 0

IE = ( + 1) IB

We can write:

- VCC + IB RB + VBE + ( + 1) IB RE = 0

Grouping terms and solving for IB:

Or we could solve for IE with:

January 2004

VCC - VBE

RB + (+1)RE

RB

- VCC + IE

+ VBE + IE RE = 0

( + 1)

IB =

ENGI 242/ELEC 222

27

Collector-Emitter Loop

January 2004

Fixed Bias

ENGI 242/ELEC 222

28

14

ENGI 242/ELEC 222

January 2004

Collector-Emitter Loop

Applying Kirchoffs voltage law:

- VCC + IC RC + VCE + IE RE = 0

Assuming that IE IC and solving for VCE: VCE = VCC IC (RC + RE)

If we can not use IE IC the IC = IE and: VCE = VCC IC (RC + RE)

V E = IE R E

Solve for VE:

Solve for VC:

VC = VCC - IC RC

or

VC = VCE + IE RE

Solve for VB:

VB = VCC - IB RB

or

VB = VBE + IE RE

January 2004

ENGI 242/ELEC 222

29

Transistor Saturation

At saturation, VCE is at a minimum

We will find the value VCEsat = 0.2V

For load line analysis, we use VCE = 0

To solve for ICSAT, use the output KVL

equation:

ICSAT =

January 2004

Fixed Bias

ENGI 242/ELEC 222

V CC - V CE

RC + RE

30

15

ENGI 242/ELEC 222

January 2004

Load Line Analysis

The load line end points can be calculated:

At cutoff:

VCE = VCC | IC = 0 mA

At saturation:

IC =

January 2004

VCC

| VCE = 0V

RC + RE

ENGI 242/ELEC 222

31

Emitter Stabilized Bias Circuit Example

January 2004

Fixed Bias

ENGI 242/ELEC 222

32

16

ENGI 242/ELEC 222

January 2004

Design of an Emitter Bias CE Amplifier

Where .1VCC VE .2VCC

And .4VCC VC .6VCC

January 2004

ENGI 242/ELEC 222

33

Emitter Bias with Dual Supply

January 2004

Fixed Bias

ENGI 242/ELEC 222

34

17

ENGI 242/ELEC 222

January 2004

Emitter Bias with Dual Supply

Input

January 2004

Fixed Bias

Output

ENGI 242/ELEC 222

35

18

You might also like

- AMI Model 227 Power Supply Operator Training GuidelinesDocument156 pagesAMI Model 227 Power Supply Operator Training Guidelinesrodstiffington160% (5)

- Exp 1 Group 4 DraftDocument35 pagesExp 1 Group 4 DraftJERUSHA ANNE RETARDONo ratings yet

- 54765e PDFDocument152 pages54765e PDFCristobal PerezNo ratings yet

- Scientech Manual - 1Document19 pagesScientech Manual - 1Piyush Patel0% (1)

- Activity5 Group1Document24 pagesActivity5 Group1NicoNo ratings yet

- Unijunction Transistor: Experiment No.4Document9 pagesUnijunction Transistor: Experiment No.4Martin John RamirezNo ratings yet

- DC Motor Are of 3 Types They Are .Document12 pagesDC Motor Are of 3 Types They Are .Krishna100% (1)

- GS02 33 35Document2 pagesGS02 33 35Adal VeraNo ratings yet

- EASA AC Redesign Manual V.0214-0815 PDFDocument140 pagesEASA AC Redesign Manual V.0214-0815 PDFDon FreemanNo ratings yet

- SKEE 2742 Basic Electronics Lab: Experiment 2 BJT Small-Signal AmplifierDocument8 pagesSKEE 2742 Basic Electronics Lab: Experiment 2 BJT Small-Signal Amplifierمحمد ابو جرادNo ratings yet

- DADocument40 pagesDAkrishneel sharmaNo ratings yet

- BJT BiasingDocument26 pagesBJT BiasingShafiul Huda Eraz100% (1)

- EEM328 Electronics Laboratory - Report4 - BJT BiasingDocument4 pagesEEM328 Electronics Laboratory - Report4 - BJT Biasingdonatello84No ratings yet

- Group 2 Act 5Document6 pagesGroup 2 Act 5Quezza Phola S PatulinNo ratings yet

- DC and AC Analysis BJTsDocument100 pagesDC and AC Analysis BJTsHasmizar Abd Halim (KTN)No ratings yet

- Transformer 1 2Document94 pagesTransformer 1 2Tobi AQWNo ratings yet

- EEM328 Electronics Laboratory - Experiment 3 - Diode ApplicationsDocument3 pagesEEM328 Electronics Laboratory - Experiment 3 - Diode Applicationsdonatello84No ratings yet

- A C Circuit-II FinalDocument57 pagesA C Circuit-II FinalVaibhavNo ratings yet

- Experiment 1Document12 pagesExperiment 1Jomar RosalesNo ratings yet

- BE Descriptive Notes PDFDocument199 pagesBE Descriptive Notes PDFBOOMERaNG boomNo ratings yet

- Series Type Voltage RegulatorDocument4 pagesSeries Type Voltage RegulatorErika VistanNo ratings yet

- Bipolar Junction Transistor: E B CE CBDocument18 pagesBipolar Junction Transistor: E B CE CBMohammadAshraful100% (1)

- 6.BJT 6 (CH 8 Electronic Devices and Circuit Theory Robert Boylestad Louis Nashelsky 7th Edition)Document46 pages6.BJT 6 (CH 8 Electronic Devices and Circuit Theory Robert Boylestad Louis Nashelsky 7th Edition)shilaNo ratings yet

- Group Study - Industrial Electronics and Robotics Answer KeyDocument6 pagesGroup Study - Industrial Electronics and Robotics Answer KeySheehan Kayne De CardoNo ratings yet

- Ecad Lab ManualDocument83 pagesEcad Lab ManualJacklyn Untalan100% (1)

- BJT NotesDocument110 pagesBJT NotesHardesh Chauhan100% (1)

- Quadrature Phase Shift Keying (QPSK)Document41 pagesQuadrature Phase Shift Keying (QPSK)Luis Fernando Grueso-TenorioNo ratings yet

- Experiment 3 - Common Emitter AmplifierDocument6 pagesExperiment 3 - Common Emitter AmplifierAsyraf Norahairuzan100% (1)

- Lesson 2 - BJT Small Signal Amp PDFDocument62 pagesLesson 2 - BJT Small Signal Amp PDFToánNo ratings yet

- Technological University of The Philippines: Laboratory ReportDocument10 pagesTechnological University of The Philippines: Laboratory Reportmoy balgosNo ratings yet

- Basic BJT Operation and BiasingDocument59 pagesBasic BJT Operation and BiasingangenghuatNo ratings yet

- EE212 Short Test 1 2016 SolDocument4 pagesEE212 Short Test 1 2016 SolkioneNo ratings yet

- Electronic Devices Experiment 4Document13 pagesElectronic Devices Experiment 4ArvinALNo ratings yet

- Diode Limiters and Clampers ReportDocument19 pagesDiode Limiters and Clampers ReportMG Acdal PagulonNo ratings yet

- DC MotorDocument38 pagesDC MotorMarc Joshua MACATANGAYNo ratings yet

- Power Electronics-3rd ChapterDocument80 pagesPower Electronics-3rd ChapterPasupuleti SivakumarNo ratings yet

- Intro Op AmpDocument44 pagesIntro Op AmpNimish PrabhakarNo ratings yet

- DC Lab Exp 6 (Study of Superposition Theorem) - Acs PDFDocument11 pagesDC Lab Exp 6 (Study of Superposition Theorem) - Acs PDFSaidur Rahman50% (2)

- Solved Problems On Transistor Biasing Excellent StuffDocument15 pagesSolved Problems On Transistor Biasing Excellent StuffStudent HelperNo ratings yet

- Remote Control For Toy CarDocument2 pagesRemote Control For Toy CarAriel MaubogNo ratings yet

- Home Assignment - 1Document2 pagesHome Assignment - 1chaitanyaNo ratings yet

- Elex MergeDocument94 pagesElex MergenicoleNo ratings yet

- Final Exam Part 1 StudentDocument4 pagesFinal Exam Part 1 StudentRJ Balbedina100% (1)

- TransducersDocument9 pagesTransducersRo#it100% (1)

- Topic 4: Bipolar Junction TransistorsDocument188 pagesTopic 4: Bipolar Junction TransistorsbhargaviNo ratings yet

- Experiment 3 Indiv. ReportDocument3 pagesExperiment 3 Indiv. ReportKyla Mae Arago100% (1)

- Chapter 1 Introduction To Electronic Communication PROFDocument69 pagesChapter 1 Introduction To Electronic Communication PROFJohn Ace Faustino0% (1)

- Chapter5 PDFDocument128 pagesChapter5 PDFTonmoyNo ratings yet

- Basic Electronics Lab Manual For BSCDocument15 pagesBasic Electronics Lab Manual For BSCGanesan KandasamyNo ratings yet

- Sample and Hold AssignmentDocument8 pagesSample and Hold AssignmentRen BurnettNo ratings yet

- Experiment 1Document6 pagesExperiment 1Jomel JomelNo ratings yet

- Capacitors PDFDocument84 pagesCapacitors PDFNaseerUddin100% (1)

- Electronics Lab Report: Transistor As A SwitchDocument7 pagesElectronics Lab Report: Transistor As A SwitchshahzaibNo ratings yet

- Unit 5 Transistors: StructureDocument23 pagesUnit 5 Transistors: StructureParminder singh parmarNo ratings yet

- Biasing DC and Ac Load LinesDocument15 pagesBiasing DC and Ac Load Linesarjuna4306No ratings yet

- A Transistor May Be Operated in Three Different ConfigurationsDocument7 pagesA Transistor May Be Operated in Three Different ConfigurationsApurva NagdeoteNo ratings yet

- EE 146 Exercise 5Document5 pagesEE 146 Exercise 5Mich TriaNo ratings yet

- Linear Circuit AnalysisDocument19 pagesLinear Circuit AnalysisFelixAvilaNo ratings yet

- Mariah Lydia Supremo Ee 404 Laboratory Experiment 5Document5 pagesMariah Lydia Supremo Ee 404 Laboratory Experiment 5andrei saad100% (1)

- Electronic Device Lab 1 Diode CharacteristicsDocument9 pagesElectronic Device Lab 1 Diode CharacteristicsVy NguyễnNo ratings yet

- BJT Fixed Bias: ENGI 242 ELEC 222Document35 pagesBJT Fixed Bias: ENGI 242 ELEC 222Edward FahmiNo ratings yet

- Engi 242/elec 222Document7 pagesEngi 242/elec 222betteralwzNo ratings yet

- Transister Fixed BiasDocument21 pagesTransister Fixed BiasHariom RavatNo ratings yet

- BJT Bias 2Document21 pagesBJT Bias 2kashi13No ratings yet

- 8085 Microprocessor ArchitectureDocument46 pages8085 Microprocessor ArchitectureJuhil H Patel100% (1)

- BJT Bias 2Document21 pagesBJT Bias 2kashi13No ratings yet

- Engi 242/elec 222Document7 pagesEngi 242/elec 222betteralwzNo ratings yet

- FET BiasingDocument48 pagesFET Biasingbetteralwz100% (3)

- Viewsonic Pjd5112 SMDocument60 pagesViewsonic Pjd5112 SMGabriel VidelaNo ratings yet

- Assembling AC DCPower SupplyDocument51 pagesAssembling AC DCPower SupplyDexter Rogero GumapoNo ratings yet

- PSM Veena Project 19-20 - 1Document69 pagesPSM Veena Project 19-20 - 1Atul KumarNo ratings yet

- TM 11-6665-209-40 - Radiac - Set - AN - PDR-27 - 1981Document45 pagesTM 11-6665-209-40 - Radiac - Set - AN - PDR-27 - 1981Wurzel1946No ratings yet

- Midi All 2Document595 pagesMidi All 2yudaadhiwaraNo ratings yet

- Module 1-1 (RC Coupling)Document9 pagesModule 1-1 (RC Coupling)Jenz Ryan GacutanNo ratings yet

- Toshiba 27a34Document45 pagesToshiba 27a34IrwingSanchezNo ratings yet

- Manual Skoda Octavia 1,9 74kW ATDDocument64 pagesManual Skoda Octavia 1,9 74kW ATDCornea Horatiu Sebastian100% (2)

- Catalogo Delta c2000bDocument48 pagesCatalogo Delta c2000bEduardo CamNo ratings yet

- DS STS207 HV 2007 e R03Document2 pagesDS STS207 HV 2007 e R03Žarko MočnikNo ratings yet

- MJoy 16 C 1Document2 pagesMJoy 16 C 1Edilberto SantosNo ratings yet

- Rain Alarm Investigatory ProjectDocument16 pagesRain Alarm Investigatory ProjectSakshi DuttaNo ratings yet

- DataSheet Antenas para Enlace Punto A Punto 60GHz Gigabit+ Wirelles Bridge Ubiquiti UniFi Building Bridge PDFDocument5 pagesDataSheet Antenas para Enlace Punto A Punto 60GHz Gigabit+ Wirelles Bridge Ubiquiti UniFi Building Bridge PDFPlanetNo ratings yet

- Block DiagramDocument17 pagesBlock DiagramSimran Jeet Singh MakenNo ratings yet

- Omnik - Let Mankind Share and Enjoy Blue Sky and White Clouds Professional Inverter ManufacturerDocument18 pagesOmnik - Let Mankind Share and Enjoy Blue Sky and White Clouds Professional Inverter ManufactureromnikshanNo ratings yet

- MemristorDocument30 pagesMemristorjoseph458No ratings yet

- Direct Current Circuit AnalysisDocument58 pagesDirect Current Circuit AnalysisLutfi LatifNo ratings yet

- FarmBeats Student Kit Build InstructionsDocument28 pagesFarmBeats Student Kit Build InstructionsheribertoloezaNo ratings yet

- Empower RF Amplifier 1117Document3 pagesEmpower RF Amplifier 1117DaniNo ratings yet

- Iecex Bas 09.0080XDocument9 pagesIecex Bas 09.0080XFrancesco_CNo ratings yet

- Standard One-Storey School Building: (1 - Classroom)Document20 pagesStandard One-Storey School Building: (1 - Classroom)Edelyn Lindero AmbosNo ratings yet

- ETN1B PracDocument12 pagesETN1B Pracnkosingiphilephiri639No ratings yet

- CSR8635 DatasheetDocument105 pagesCSR8635 DatasheetJoe Mar0% (1)

- BTech CSE Syllabus 2015 16Document97 pagesBTech CSE Syllabus 2015 16Satya Sai PrasadNo ratings yet

- Samsung CL29K3W Chassis KS3ADocument92 pagesSamsung CL29K3W Chassis KS3AHernan Ortiz EnamoradoNo ratings yet